SCOTT, FORESMAN AND COMPANY COMPUTER BOOKS

### PROGRAMMING THE INTEL 80386

## PROGRAMMING THE INTEL 80386

Bud E. Smith Mark T. Johnson

Scott, Foresman and Company Glenview, Illinois London

ISBN 0-673-18568-0

Copyright © 1987 Bud E. Smith.

All Rights Reserved.

Printed in the United States of America.

#### Library of Congress Cataloging-in-Publication Data

Smith, Bud E. Programming the Intel 80386.

Includes index. 1. Intel 80386 (Microprocessor)—Programming. I. Johnson, Mark T. II. Title. QA76.8.I2928S65 1987 005.265 86–29862 ISBN 0–673–18568–0

1 2 3 4 5 6 MVN 91 90 89 88 87 86

#### NOTICE OF LIABILITY

The information in this book is distributed on an "As Is" basis, without warranty. Neither the author nor Scott, Foresman and Company shall have any liability, loss, or damage caused or alleged to be caused directly or indirectly by the programs contained herein. This includes, but is not limited to, interruption of service, loss of data, loss of business or anticipatory profits, or consequential damages from the use of the programs.

Scott, Foresman Professional Publishing Group books are available for bulk sales at quantity discounts. For information, please contact Marketing Manager, Professional Books, Professional Publishing Group, Scott, Foresman and Company, 1900 East Lake Avenue, Glenview, IL 60025.

### Dedication

Dedicated to all those who are right now burning the midnight oil trying to make something "insanely great" happen with a pile of quirky transistors in silicon, and to their long-suffering friends and families. Acknowledgments

Our first debt is to Jonathon Shiell of Carlton G. Amdahl Associates, Inc., in Santa Clara, California. He has put many hours into suggestions, comments, and criticisms. He also contributed notes for what became Chapter 7, and gave us early access to his excellent series of articles for *Byte* magazine and the research behind them. Beyond this, he has also marshalled an impressive array of friends and confreres in Silicon Valley who have interrupted important and pressure-filled work to contribute. The level of advice would normally be expensive to get; the level of energy and committment given to turning a pedestrian work into something to be proud of are priceless.

Ken Williams, Vice President for Research and Development at Softguard Systems, was the single main source in keeping us relentlessly upto-date with the latest developments. Many others at Softguard have also provided assistance at a time when all of them needed R & R, not more 386-oriented work.

Dick Balluf of DB Micro offered a software developer's viewpoint of what's needed in a book of this nature.

Andrew J. Piziali looked past the technical details to help correct our all-too-frequent abuse of that most important programming language, English.

Bill Gladstone and Tershia D'Elgin of Waterside Productions put the wheels back on when they were about to fall off, introduced the principals to one another and kept on top of schedules and financial commitments.

Richard Swadley at Scott, Foresman had patience with a project that went slowly for all too long.

Bob Caldwell of Centaurus Software and Roger Ogden gave hardware support for the writing process.

Contents

| INTRO | DDUCTION                                                | xi  |

|-------|---------------------------------------------------------|-----|

| CHAP  | PTER 1 ASSEMBLY LANGUAGE BASICS                         | 1   |

|       | Assembly Language and the Assembler<br>Computer Numbers | 2 9 |

|       | Binary Math                                             | 14  |

|       | Binary Math Applications                                | 19  |

| CHAP  | TER 2 80386 APPLICATIONS ARCHITECTURE                   | 23  |

|       | Intel's and Other Early Microprocessors                 | 24  |

|       | The 8086 Family                                         | 25  |

|       | Microprocessor Basics                                   | 26  |

|       | The Fetch-Decode-Execute Cycle and the 80386            | 28  |

|       | A Bit-by-bit Look at EFlags                             | 33  |

|       | Flat and Segmented Memory                               | 37  |

| CHAP  | TER 3 GUIDE TO THE INSTRUCTIONS                         | 51  |

|       | Data Movement Instructions                              | 52  |

|       | Standard Arithmetic Instructions                        | 54  |

|       | Data Conversion Instructions                            | 58  |

|       | Decimal Arithmetic Instructions                         | 60  |

|       | Logical Instructions                                    | 61  |

|       | Shift and Rotate Instructions                           | 62  |

|       | Bit Instructions                                        | 64  |

|       | Flag Control Instructions                               | 65  |

|       | String Instructions                                     | 66  |

|       | Flow Control Instructions                               | 68  |

|       | High-Level Language Support Instructions                | 70  |

|       |                                                         | ix  |

| Processor Control Instructions               | 71  |

|----------------------------------------------|-----|

| Address Manipulation Instructions            | 71  |

| Translation Instruction                      | 72  |

| Summary                                      | 73  |

| CHAPTER 4 THE 80386 INSTRUCTION SET          | 75  |

| How Assembly Language Works                  | 78  |

| What is an Instruction's Format?             | 79  |

| Timing Information                           | 81  |

| The 80386 and other iAPX 86 Chips            | 84  |

| The Instructions                             | 86  |

| CHAPTER 5 PROTECTED MODE                     | 277 |

| Multitasking                                 | 278 |

| Segmentation                                 | 281 |

| Paging                                       | 284 |

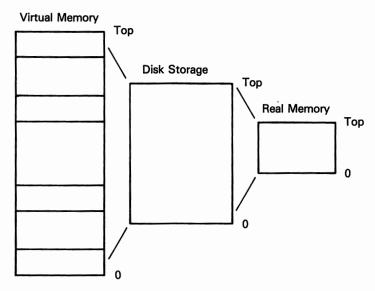

| Virtual Memory                               | 287 |

| CHAPTER 6 V8086 MODE AND MORE                | 291 |

| Virtual 8086 Mode Defined                    | 292 |

| Virtual Machines                             | 293 |

| More On Virtual Modes                        | 294 |

| Processors and Modes Compared                | 296 |

| Operating System Considerations              | 304 |

| CHAPTER 7 THE 80386 PROCESSOR IN DEPTH       | 307 |

| Computer System Performance                  | 308 |

| How an 80386 Memory Access Works             | 309 |

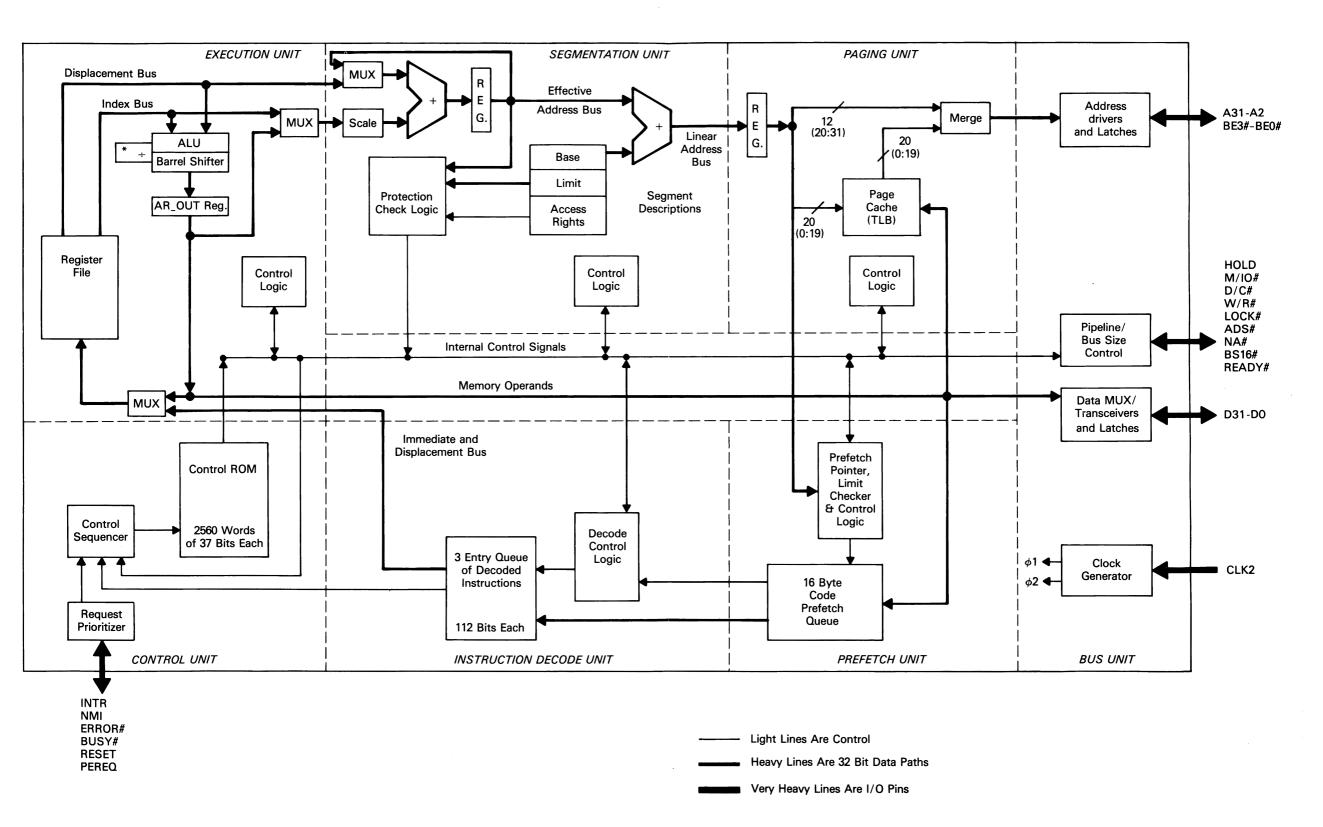

| Inside the 80386                             | 323 |

| Ripley's Believe It or Not                   | 338 |

| Some Applications Programming Considerations | 339 |

Introduction

Welcome to *Programming the Intel 80386*, the most detailed yet easy to understand book to date on the capabilities of the Intel 80386 micro-processor. In this book, we hope to reach several audiences:

The experienced 8086/8088 programmer who wants or needs to understand the capabilities of the 80386. This book delves into the lowlevel and operating system considerations which give necessary background for designing and implementing serious programming projects.

The programmer experienced with other microprocessors (68000, 6502, Z80, etc.) who wants to step into the 8086 family. This book not only gives detailed coverage of the instruction set, it explains how addressing, protection, and other important features of the 80386 work. It does not assume prior experience with previous Intel microprocessors.

The high-level language programmer who wants to learn assembly language. This book includes an introduction to numbering systems and other basic topics. This reader, however, will also need programming examples, either in book form or from a fellow programmer, to understand how assembly language is used.

The person with good computer knowledge who wants to be an intelligent computer and software buyer. Besides describing the processor itself, this book talks about different memory arrangements and possible operating system capabilities. Someone buying an 80386-based computer would do well to know what the processor can handle as background for judging the products that use it.

This book is not designed to be a complete source for those who are writing systems programs like operating systems, device drivers, etc; no single book can do that. Reading this book would be an excellent first step, however, for writing these complex programs. This book is not for the person new to programming, although the first chapter and parts of other chapters are accessible to the general reader. Given the variety of material presented here, you may want to read it out of order, or skim some parts as you go through it the first time; it's hard to imagine anyone reading the instruction set in Chapter 4 straight through. Even if you are normally very careful with your books, this might be a good one to write in. Put question marks next to new subjects you want to explore more, and check off sections as you read them. For anyone who's not already an expert there will be much here to learn and to research further later on.

#### **HIGHLIGHTS OF THE 80386**

This book looks at the 80386 on its own terms, not just as a derivative of the 8086/88 and the 80286 (we will refer to the 8086 and the 8088 together as simply "the 8086" unless otherwise specified). In fact, much of the text deals with ideas that have come to the microprocessor world from minicomputers and mainframes. Capabilities like paging, virtual memory, and multitasking are discussed at some length. These are features which are made available by operating systems; the experienced programmer of IBM PC-type computers will be eager to know what advantages the 80386 offers the applications programmer. Each of these advantages is discussed at length, with terms defined where needed. Here's a short list of important new capabilities available in Real Mode, based on the experience of a friend who's writing systems software for the new processor:

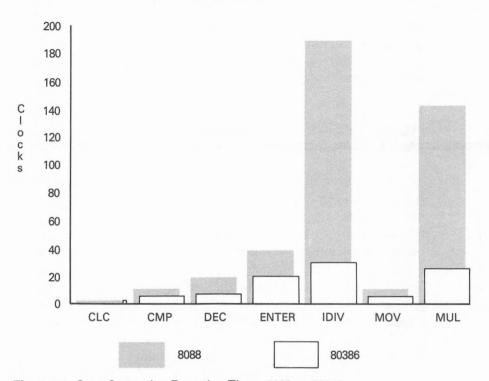

SPEED. Simply by running at a clock speed of 16 MHz, the 80386 is twice as fast as most 80286s. Lower clock counts and new instructions give a further 50% speed increase. Thus, machines built around the new processor run about three times as fast as an IBM PC AT. The use of cache memories and other memory optimizations can increase performance even more.

32-BIT REGISTERS. Larger registers make it very easy to handle large numbers and other data items efficiently. They also make it possible to do more work with register variables and cut down memory accesses.

NEW INSTRUCTIONS. Among the most important of the many new instructions offered by the 80386 are the Bit Test instructions, which allow testing and turning on and off of individual bits.

EXTRA SEGMENT REGISTERS. The new FS and GS registers are offered as segment registers for additional data segments. They can also

be used as general registers (up to a point), and are very useful in either capacity.

NEW DEBUG REGISTERS. The 80386 has registers which make it easy to put in code or even data breakpoints, and to single-step a program. These registers can be used either from within a program or by a debugger.

SCALED INDEXING. Memory addresses which use indexing can now be scaled by a factor of 2, 4, or 8 bytes, making certain data structures very easy and fast to access.

IMMEDIATE SHIFTS AND ROTATES. This capability, which first appeared on the 80286 and continues with the 80386, makes many applications problems easier to solve. The number of bits by which to shift or rotate a quantity can now be given as an immediate value in the code itself, avoiding extra register usage.

FLAT MEMORY MODEL. The old 64 Kb limit on segment size is now gone. The new limit is 4 Gb, making it easy for even a very large program to have just one code segment, one stack segment, and one or more data segments, each with huge data structures not broken into segments. However, unlike the advantages listed above, this one is only available in Protected Mode.

#### **OVERVIEW**

This book is somewhat unusual for a work about microprocessors. The 80386 has many capabilities similar to those of a minicomputer or even (in some cases) a mainframe. As an example, the 80386 can execute up to 4 million instructions per second (mips). It was only ten years ago that the first mainframe to attain a speed of 1 mips became available. Thus all the work that was done for optimizing those computers—support hardware, efficient and capable operating systems, and more—applies directly to the 80386. The designers at Intel have been very conscious of this previous work, building capabilities like paging and virtual memory support right into the chip for the first time in any microprocessor. In order to describe the capabilities of the new chip, much space is devoted to paging, segmentation, and other advanced topics not usually covered in such a "chip book."

This book is called Programming the Intel 80386, and it includes a complete description of the instruction set as used for non-systems pro-

grams, with a summary of the different classes of instructions and examples of how each works. However, it does not include large-scale programming examples or a systematic treatment of optimization techniques. There is so much ground to cover in describing the processor itself and the operations it can perform that large application examples are left for future books, including one from this pair of authors. These future programming-examples books will generally assume that you've read a book like this one as preparation for plunging into the details of actual applications.

Because there are not yet an operating system and computer which really stretch the power of the 80386, successive topics within a chapter may seem somewhat unrelated. This is because the system software and large applications which will relate them, tying the capabilities together into new and powerful programs, are not yet written. The information in this book will give the programmer the vocabulary and insight he or she will need in order to design and implement the programs which will be demanded in the next few years. As you use an 80386-based system with a suitable operating system, the capabilities described here will come alive for you and be reflected in the programs you write.

This book is not only broad in its coverage of important topics, it is also deep. As authors we have been surprised to find out how little most programmers know about how a microprocessor really works. For instance, when we say an instruction takes two clocks to execute, how does this relate to what's going on inside the chip itself? Chapter 7 explains the operations of the 80386 and the units which make it up. It describes techniques for memory access and follows a short programming example as it is executed. We hope that even those who mostly program some other microprocessor will find this chapter interesting, and that it will give programmers a better understanding of what they're actually causing to happen as they do their work.

#### CONTEXT

A book like this aims for a certain timelessness; it should be as useful ten years after it was published as when it first came out. However, this work is being published early enough in the life cycle of the 80386 that some background should be given. In early 1987, as this is published, the 80386 itself is in version B0. It is available in 12.5 MHz and 16 MHz versions, but the 16 MHz version seems to be the choice of system developers.

The processor is being produced using a 1.5 micron feature size, which means that the highest resolution possible in placing circuit elements is 1.5 microns. It's believed that within one year Intel will come out with an 80386 made with a 1 micron feature size. This new version should allow clock speeds of 20 or even 25 MHz, but won't cause any changes in the instruction set or in the number of clocks needed for each instruction.

There are currently three types of 80386-based systems: 1) the Compaq 386, built around a proprietary design by Compaq; 2) other announced computers built around an 80386 motherboard (processor plus support chips) made by Intel; and 3) Turbo cards for the IBM PC AT and compatibles, which offer an 80386 and a cache memory and which plug into the socket normally occupied by an 80286.

As this is written there are no true operating systems for the 80386, only a bootstrapping program from Microsoft which allows the Compaq 386 to run 8086-based operating systems. The bootstrapper supports an extended memory specification to allow access to memory beyond the 640 Kb limit of MS-DOS 2.x and 3.x. Also, there are only a couple of assemblers available, and these are known to be "buggy."

Our contacts at companies working on system software for the 80386 tell us that it works as expected, with the exception of some obscure bugs which will not be noticed by applications programmers. This book does not depend on any one operating system, version of an assembler, or computer system. However, the mnemonics (instruction names like MUL and ADD) used by your assembler might be slightly different from the ones we use here.

Future revisions of this book, which will be produced as demand warrants, will note any changes in the 80386. We would be interested in hearing your likes and gripes about this book, along with the things you would like to see included in it or in other works. In particular, we are planning a book of programming examples which will be a companion to this volume, and would appreciate any suggestions for that book. Such letters can be sent to the authors care of Scott, Foresman; simply put both authors' names and the name of this book on the envelope. CHAPTER 1 Assembly Language Basics

ASSEMBLY LANGUAGE AND THE ASSEMBLER COMPUTER NUMBERS BINARY MATH BINARY MATH APPLICATIONS

There is a tremendous range of experience among programmers using the 80386. Some are systems programmers with extensive experience in operating systems, device drivers, or large assembly language programs. Others are experienced in one or more high-level languages like BASIC and PASCAL, but have used assembly language very little, perhaps only as in-line code within a high-level program. This chapter will help ensure that each reader is exposed to the most important concepts used in assembly language programming.

First we'll take a look at an 80386-style assembly language statement as an example of what an assembler does and what each statement causes the machine to do. Following this we'll discuss the different types of numbers used in assembly-language programming—binary, BCD, hexadecimal, and more. Most programmers will know most of these terms, but the basics of number types and operations will be assumed later in the book, so an overview is given here. If you have programmed 2

Intel chips in assembler before, you may want to skim this chapter rather than read it. On the other hand, if much of what follows is new to you, further study might be indicated before plunging into 80386 programming. This chapter will be a useful review for the large number of programmers with some, but not extensive, assembler experience.

#### ASSEMBLY LANGUAGE AND THE ASSEMBLER

The following instruction is a typical 80386 assembly language statement:

#### MOV AX, BX

The first word is MOV, an assembly language command, like a direct order from the programmer to the computer. So what gets moved? AX and BX are registers, storage locations in the 80386 itself. The number stored in the BX register is moved into location AX. After the MOV both AX and BX will contain the same value.

Each non-blank line in an assembly language program contains either an "instruction" or a "directive." The most important pieces of an instruction are a command and up to three operands. The command performs some operation, generally using the data in its operands. Other parts of an instruction and a directive are described below.

MOV AX, BX, for instance, has a command and two operands. Most two-operand instructions are of the form:

#### **COMMAND** Destination, Source

Arithmetic instructions with the commands ADD and DIV, for example, look like this. The instruction takes its second operand, performs some operation on it using the first operand (like adding the two together), then stores the result in the first operand. Whatever was in the first operand is overwritten by the result.

Many instructions have implied operands. For instance, the instruction CLC means "clear the C bit," that is, put the Carry bit to 0. The command itself is "clear," the operand (the Carry bit) is implied by the instruction. An instruction's operands can be individual bits in the chip's own registers, bytes, words or doublewords in registers, or any of these in the computer's main memory. Chapter 2 will cover more about the overall design of the computer system.

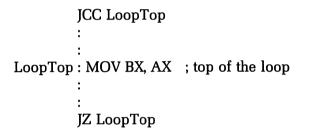

Normally a computer executes instructions in the order in which they appear in the program. However, we need to be able to change this sometimes—in order to make the program execute a loop, for example. To make this happen we might use these instructions:

The word "LoopTop" is a label for the statement MOV BX, AX. The symbol ";" on the same line indicates a comment, which follows immediately. The dots on some lines indicate statements that we're not interested in for now.

The JCC (Jump if Carry Clear) instruction checks the Carry bit (more on this later) and, if a 0 is in it, passes control to the MOV statement labeled "LoopTop." The JZ (Jump if Zero) instruction does the same thing, but checks the Zero bit to decide whether to jump to the label.

An assembly language statement can take the form:

Label: COMMAND Operand(s) ; comment

The label is optional, and so is the comment; the number of operands needed varies with the command used. The only part of a statement that is always required is the command itself; if a label is alone on a line it's assumed to go with the command on the following line.

Instead of going on with examples of various 80386 instructions here, we refer the interested reader to Chapter 3, which gives a brief functional description of each type of 80386 instruction. Beyond the actual instructions and operands, there are several other elements in assembly language, and these are explained below.

#### Instruction Prefixes

Prefixes (reserved words used in an 80386 statement just before the instruction itself) cause some instructions to act differently than they would otherwise. Two useful prefixes are LOCK, which helps the 80386 grab sole control of a piece of RAM when several processors are sharing the same memory, and REP and its variants, which cause an instruction to be repeated. Prefixes are mentioned here because they further enlarge what we can find on any single line of an assembler program:

Label: PREFIX COMMAND Operand(s) ; comment

For example:

OneLoop: REP MOVS Dest, Source ; moves bytes

This moves a given number of bytes (the number is found in one of the chip's registers) from one location in RAM to another.

#### Assembler Directives

The commands discussed above are all instructions, which the assembler translates into machine language commands to be executed by the microprocessor. The assembler determines exactly which form of a given command to use in order to get the effect the programmer wants.

There are times when we need to tell the assembler in advance what it is we plan to do. For instance, if our data items in a program are all word-sized (16-bit quantities), we don't want the computer to move doublewords (32-bit quantities) around. Assembler directives look a lot like regular instructions, but aren't translated directly into machine language commands which tell the processor what to do next. Instead, they tell the assembler how to interpret the instructions and directives which follow them, point out where a program starts and stops, and serve many other functions.

For example, almost every program has variables in it. A directive to tell the assembler a variable's name has the form:

Name Directive Initial Value ; comment

For example:

| MyAge | DB | 29 | ; directive w/fake data     |

|-------|----|----|-----------------------------|

|       | DB | 0  | ; 2nd byte, initial value 0 |

This tells the assembler that whenever the variable MyAge is referred to in the program following, a byte value is being referred to and the byte's initial value is 29. The byte reserved on the next line could be referred to as MyAge + 1, meaning "the byte after the byte with MyAge in it." As shown by these two directives, the name at the start of a directive line is optional.

Another important directive is EQU, which tells the assembler to give a name to a number. For instance, the following directive tells the assembler to use the number 62 wherever the word Retire is found in the program:

Retire EQU 62

Notice that the DB directive tells the assembler to put a certain value (29) in a given byte in memory, while the EQU directive tells it to remember to replace the word "Retire" with the value 62 as it is converting the program to machine language. In a typical use of the EQU directive, if the retirement age needed by the program changes, we can change the line to read:

Retire EQU 65

When the program is reassembled the number 65 will be used wherever the word Retire is found.

More information about directives can be found in the documentation for the assembler you're using, and this should be studied carefully. Among other functions, directives determine how programs are arranged in memory, and they can help give a program some of the structure of a high-level-language program.

#### Assembler Arithmetic

In both instructions and directives the assembler will evaluate expressions for us. That is, if it finds an expression (like RETIRE -3) where it expects a single number, it will do the math required and place the result in the machine language program. For instance, if we've used an EQU instruction to tell the assembler that Retire is equal to 65, then the following command will move Retire +5, or (65 + 5 =) 70 into AX:

MOV AX, Retire + 5

However, the work of deciding what "Retire + 5" equals is done when the program is assembled, so assembler math can only use numbers that have been specified before a given statement is assembled. Exact descriptions of math done by your assembler will be found in the appropriate documentation.

#### What Assembly Language Does

You might ask, "What's the difference between assembly language and a high-level language?" The structure of assembly statements is a little unusual, but even the brief examples seen so far demonstrate loops, transfers of control, conditional statements, and variables, all elements of high-level languages.

The most important feature of assembly language is that every instruction is translated by the assembler into one and only one machine language instruction. The machine language code for a MOV between two registers is slightly different than that for a MOV between two locations in RAM, but in both cases each assembly instruction translates into one instruction in machine language. In a high-level language each statement can be translated into any number of machine language instructions (sometimes just one, but often five or more depending on the statement and its context).

Another important feature of assembly language is that the programmer can directly name the microprocessor registers and exact memory locations to be used for storing and operating on data. When a BASIC programmer says LET A = B, he or she has no control over where the numbers end up. Writing MOV AX, BX in assembler, however, lets the programmer know exactly what he or she is doing.

The different forms taken by a MOV instruction depend on exactly what type of operands it has, and are rarely of concern to the programmer. The important thing is the overall effect, that a value is copied from one location to another. This book will give both the overall effect and the details of how it's achieved, because at those times when it becomes important to know an instruction's format the information needs to be quickly available and understandable.

It is often said that an assembly language program can do everything a high level language can do, and additional things besides. This is true from the computer's point of view, but not necessarily the programmer's. The sheer amount of detail that the assembler programmer must be concerned with—exactly where does this number go, will this loop always terminate—can cause the programmer to shy away from complicated control and data structures. Even a poorly written assembler program will generally execute faster than a well-written high-level-language program, but only the most carefully written assembler code approaches a high-level-language in clarity (to humans) and ease of maintenance.

#### Assembling an 80386 Instruction

Let's look at Listing 1-1 to see exactly what the assembler does with a very small piece of assembly language code.

The assembler will translate the code in Listing 1-1 into machine language for the 80386 to execute.

Line 1, the EQU statement, tells the assembler to substitute the number 8 wherever it sees the word "GenRegs."

Line 2, the DB statement, tells the assembler that a given byte in memory will be named RegsUsed, and will start out with the value 0.

Line 3 tells the processor to compare the value in RegsUsed, which may have been changed by the lines above it, to the number 8, which is

| GenRegs<br>RegsUsed |                 | ; 1. number of 80386 general registers<br>; 2. number of registers in use                              |                                                     |  |  |

|---------------------|-----------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|--|

| DoMore              | :               | ; code that stores data in general registers<br>; and increments RegsUsed when a register<br>; is used |                                                     |  |  |

|                     | :<br>CMP<br>JNE | gsUsed,GenRegs<br>More                                                                                 | ; 3. all registers in use?<br>; 4. if not, continue |  |  |

Listing 1-1. Assembly Process Example

represented by GenRegs. In hexadecimal (discussed later) the machine language produced by the assembler is:

80 3E ?? 08

This means compare (80) a byte at a specified location in memory (3E ??) to an immediate value (08, as defined by the EQU above). The Zero flag will be set to 1 if the two numbers are equal.

The trickiest part of this is the displacement (??), which is determined by the addressing mode used to find the byte in memory. This is discussed further in Chapter 4.

Line 4 tells the processor to continue executing at the label DoMore if the CMP on the line above showed that the two numbers were equal. The machine language is:

#### 75 XX

Here 75 indicates a "short jump," to a location within about +/-127bytes if the condition of "not equal" (the zero flag is 0) is met. XX is the number of bytes to the location, which would be the number of bytes between the instruction labeled DoMore and this INE instruction.

Listing 1-2 summarizes the assembly process by showing the assembly code next to the resulting machine-language output.

| Assembly | Langua | ge               | Machine Language |

|----------|--------|------------------|------------------|

| GenRegs  | EQU    | 8                |                  |

| RegsUsed | DB     | 0                | 0                |

| DoMore   | :      |                  |                  |

|          | :      |                  |                  |

|          | :      |                  |                  |

|          | CMP    | RegsUsed,GenRegs | 80 3E ?? 08      |

|          | JNE    | DoMore           | 75 XX            |

Listing 1-2. Assembly Process in Hexadecimal

This book gives the numeric equivalent of each 80386 instruction and addressing mode, while an assembler listing typically gives the machine-language output resulting from assembling a given program. Once you grasp the basic concept of how an instruction is translated to machine language, further study will let you learn as much as needed about the machine language code produced by your program.

#### COMPUTER NUMBERS

#### Representing What's in the Computer

In order to talk about what's going on inside the computer and command it to do exactly what we want, several different numbering systems are used. The most important is binary, the language used by the computer itself.

The insides of the computer can be seen as a series of toggle switches that can be set to either of two positions, 0 or 1, Off or On, False or True. Each switch is called a bit. To describe whether a series of bits is on or off, we write down their values in sequence (1001 or 10110 or 10001001001); each represents a series of bits in the computer, some of which are on (1) and some of which are off (0).

In order to organize all these bit values, we usually look at them in groups of 8, called bytes. The last binary number above would thus be written as 00000100 01001001, so we could talk about the value in the first byte or in the second byte.

We can describe exactly what's stored at each location in the computer, but writing a byte value (01101001 for instance) takes a lot of

space, so we use hexadecimal notation, which sums up in one symbol what's contained in a group or four bits. A symbol is assigned to each of the possible combinations of bits, as in Listing 1-3.

A single byte, then, can be represented by two hex digits, one for each four bits in the byte; 11000001 becomes C1, and 01001001 becomes 49. Since we can't tell at first glance whether 49 represents a decimal value or a hex value, we write it followed by an H; 49H means 49, hex. Although hex notation is prominently used in programming, it is really only a shorthand way to write out binary values.

Octal notation is commonly used in programming some computers. This notation looks at only three bits at a time, and translates each group of three bits into an octal digit, 0-7. Each character identifies one of eight patterns (not one of sixteen as with hex), and writing out the value in a byte takes three characters rather than two. Octal notation is not used in this book.

Many times we are interested in the number represented by a pattern of bits. To translate a binary pattern into a decimal number we start with the rightmost position in the binary number (the units position). A 1 in the units position has the value one. The position next to it is the

| Bit Pattern        | Decimal Equivalent | Hex Digit |

|--------------------|--------------------|-----------|

| Pos'n value : 8421 |                    |           |

| 0000               | 0                  | 0         |

| 0001               | 1                  | 1         |

| 0010               | 2                  | 2         |

| 0011               | 3                  | 3         |

| 0100               | 4                  | 4         |

| 0101               | 5                  | 5         |

| 0110               | 6                  | 6         |

| 0111               | 7                  | 7         |

| 1000               | 8                  | 8         |

| 1001               | 9                  | 9         |

| 1010               | 10                 | Α         |

| 1011               | 11                 | В         |

| 1100               | 12                 | С         |

| 1101               | 13                 | D         |

| 1110               | 14                 | Е         |

| 1111               | 15                 | F         |

Listing 1-3. Binary, decimal, and hex numbers

twos position; a 1 in the twos position has the value two. The next position is the fours position, and so on using a greater power of two for each position. Looked at in this way, every binary number can be translated into decimal by translating each position into a decimal number and adding the results. For instance, 1110 read from right to left means "0 ones, 1 two, 1 four, and 1 eight." Translating this into decimal is simple: 0 + 2 + 4 + 8 = 14.

Another way to look at the same thing is to think of the bit positions strictly as successive powers of 2. This is the system used in talking about bit positions in a byte.

| Binary number: | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | ı |

|----------------|---|---|---|---|---|---|---|---|---|

| Power of 2:    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | - |

The "0th" (or rightmost) bit position has the value  $2^0$ , the next position over has value  $2^1$ , and so on up through  $2^7$ , or 128. So "there's a 0 in bit position 4" means that the fifth position from the right has a 0 in it.

#### **Representing Numbers**

There are problems with representing numbers in pure binary form. For one thing, we've only talked about representing integers; no fractions or numbers with decimal points have been discussed. Also, most people don't work in binary, so numbers have to be converted back and forth on their way in and out of the computer.

One way to simplify number representation is to make the computer use base 10, as most people do. This is done using BCD (Binary Coded Decimal) notation. The 80386 includes hardware support for BCD arithmetic in a series of "ASCII Adjust" instructions that use the AL register to do BCD math two digits at a time.

In "packed BCD" four bits represent one digit, 0-9. As the figure above shows, four bits can hold sixteen different patterns (as in the hex digits 0-9 plus A-F), yet we only need ten of them (the decimal digits 0-9), so each BCD digit is wasting some of the available storage capability. An even worse problem comes when we try to do math with these numbers, because the computer automatically treats them as binary numbers, producing results that make no sense for BCD digits. Although we'll go into binary math in more detail below, let's add two BCD digits to illustrate this problem.

Binary math: 1000 (8 BCD) + 0100 (4 BCD) = 1100 (? BCD)

The sum of the two numbers is 12, but by the rules of BCD, 12 is too large a number to fit in a single, 4-bit BCD digit. What we want is for the computer to do a carry for us whenever the result of adding two BCD digits results in a number above 9 (which no longer fits in a single digit):

BCD math: 1000 (8 BCD) + 0100 (4 BCD) = 0001 0010 (12 BCD)

The ASCII Adjust instructions automatically note when an addition or other arithmetic operation has caused a discrepancy between binary rules and BCD rules, and make the needed adjustments. Note that two packed BCD digits fit in a single byte, so with BCD notation a single byte can express any number from 00 through 99; in binary the same byte can express any number from 0 through 255. BCD causes a loss of storage capability.

If enough RAM is available to make up for the wasted space caused by BCD digits, and if speed is not of the essence, BCD math is very effective for results that need to be in a human-understandable format. To store large numbers we can just use more BCD digits as needed, and to handle numbers with decimal points we simply agree on a convenient format that tells us where to place the decimal point for each number. BCD works well for dollars-and-cents applications, where it's unusual to find a number of much more than 15 digits and precision all the way down to the cents columns is very important.

However, for large numbers (as used in science and other applications) we need a format that stores very large numbers in a fixed number of bytes and doesn't just keep adding to the amount of storage needed as numbers get larger. The answer here is to use a floating-point format. Almost all floating-point math is done through prewritten software packages, and you'll need to learn the rules of any such package you wish to use. Floating-point numbers are an agreed-on format for storing large numbers in a limited number of bits. For instance, a 32-bit floating-point number might have this format:

First bit: sign bit of fraction Next 8 bits: exponent Next 23 bits: fraction

It is assumed that the number we're representing is in the form:

$(+/-1.fraction) \times (2^{+/-exponent})$

This is much like the scientific notation you might have learned in school. Since the "1" at the start of "1.fraction" and the "2" as the base for the exponent are always the same, they're not included in the floating-point number. Also, a trick involving the largest number that can fit in 8 bits allows the sign of the exponent to be deduced, so it's not explicitly stored in the number either.

The advantage of floating point numbers is that any number between about  $1/2^{128}$  and  $1*(2^{127})$  can be represented in a mere 32 bits, so we can express (if sometimes inexactly) numbers as small as about 1 over a 1 followed by 38 zeros, and as large as about 1 followed by 37 zeros. However, the floating-point representation is not precise since the fraction part of the number is 23 bits, not 128. Thus a floating-point number is usually a rounded number. Precision can be improved greatly by using 64 or 80 bits instead of 32, but precision loss remains in many cases. The adjustments needed to make a binary-based computer do floating-point arithmetic are so complicated that such math is almost always done through calls to prewritten software packages or math coprocessors.

#### Translating Large Binary Numbers

When working with computers we end up talking a lot about large binary numbers. The 80386, for example, handles data in 32-bit chunks, and the largest number we can express in 32 bits is:

#### 11111111 11111111 11111111 11111111

Reading right to left, this is:

$1 + 2 + 4 + \ldots + 1,073,741,824 + 2,147,483,648 = 4,294,967,295$  (4 billion bytes, or 4 Gb).

This number is also the number of bytes of RAM that the 80386 can address directly. When you read that the 80386 can directly address 4 gigabytes, you can see that it does so by using a 32-bit-long number to point to the byte that is being addressed.

For dealing with these large numbers and for doing math with smaller numbers, a programmer needs to have a feel for what a given power of 2 translates to in decimal. Listing 1-4 shows the number of bytes associated with the powers of 2 from  $2^{0}$  up through  $2^{31}$ .

These numbers are very handy when talking about the capabilities of the 80386. A good way to deal with the really large numbers, like  $2^{24}$  or  $2^{32}$ , is to note that  $2^{10}$  is just over a thousand (1 Kb),  $2^{20}$  is just over a million (1 Mb), and  $2^{30}$  is just over a billion (1 Gb). Powers in between fall into the same kind of progression (1, 2, 4, 8, 16, 32, 64, 128, 256, 512) that is found between  $2^1$  and  $2^9$ . So  $2^{16}$ , for example, is 64 (because of the 6) Kb (because of the 10).

#### **BINARY MATH**

The next few pages contain a reasonably complete description of binary math in very compact form, because many readers will already know some or all of the material. If any of the sections below are new to you, you'll save a lot of programming and debugging time in the future by working out the examples given and then constructing a few of your own until the principles involved are understood.

We can do binary math by simply following a set of rules, using the decimal values of the numbers only as a check. In adding two binary digits, we can run into four possible combinations:

0 + 0 = 00 + 1 = 1 1 + 0 = 11 + 1 = 0, carry of 1

We can add any two binary numbers just by repeatedly applying these rules for one pair of bits at a time, starting with the two rightmost digits

| Number of bytes | Decimal equivalent | Name                         |

|-----------------|--------------------|------------------------------|

| 2 <sup>0</sup>  | 1                  |                              |

| 2 <sup>1</sup>  | 2                  |                              |

| 2 <sup>2</sup>  | 4                  |                              |

| 2 <sup>3</sup>  | 8                  |                              |

| 2 <sup>4</sup>  | 16                 |                              |

| 2 <sup>5</sup>  | 32                 |                              |

| 2 <sup>6</sup>  | 64                 |                              |

| 27              | 128                |                              |

| 2 <sup>8</sup>  | 256                |                              |

| 2 <sup>9</sup>  | 512                |                              |

| 2 <sup>10</sup> | 1,024              | 1 kilobyte (kilo = thousand) |

| 211             | 2,048              | 2 Kb                         |

| 2 <sup>12</sup> | 4,096              | 4 Kb                         |

| 2 <sup>13</sup> | 8,192              | 8 Kb                         |

| 2 <sup>14</sup> | 16,384             | 16 Kb                        |

| 2 <sup>15</sup> | 32,768             | 32 Kb                        |

| 2 <sup>16</sup> | 65,536             | 64 Kb                        |

| 2 <sup>17</sup> | 131,072            | 128 Kb                       |

| 2 <sup>18</sup> | 262,144            | 256 Kb                       |

| 2 <sup>19</sup> | 524,288            | 512 Kb                       |

| 2 <sup>20</sup> | 1,048,576          | 1 megabyte (mega = million)  |

| 2 <sup>21</sup> | 2,097,152          | 2 Mb                         |

| 2 <sup>22</sup> | 4,194,304          | 4 Mb                         |

| 2 <sup>23</sup> | 8,388,608          | 8 Mb                         |

| 2 <sup>24</sup> | 16,777,216         | 16 Mb                        |

| 2 <sup>25</sup> | 33,554,432         | 32 Mb                        |

| 2 <sup>26</sup> | 67,108,864         | 64 Mb                        |

| 2 <sup>27</sup> | 134,217,728        | 128 Mb                       |

| 2 <sup>28</sup> | 268,435,456        | 256 Mb                       |

| 2 <sup>29</sup> | 536,870,912        | 512 Mb                       |

| 2 <sup>30</sup> | 1,073,741,824      | 1 gigabyte (giga = billion)  |

| 2 <sup>31</sup> | 2,147,483,648      | 2 Gb                         |

| 2 <sup>32</sup> | 4,294,967,296      | 4 Gb                         |

Listing 1-4. Powers of 2 and Bytes

and working left (just as with two decimal numbers). The only complication is the carry generated when we add two 1's; the trick is to make sure to add the two digits in the operands first, yielding a one-bit result, then add the carry to this result to determine the final value (and whether or not there's a further carry). Here's an example:

1100110 110111 10011101

This is the equivalent of adding (0 + 2 + 4 + 0 + 0 + 32 + 64 =) 102 and (1 + 2 + 4 + 0 + 16 + 32 =) 55, with a result of (1 + 0 + 4 + 8 + 16 + 128 =) 157, as expected.

#### Subtracting Binary Numbers

Subtraction is less intuitively obvious than addition. The four possibilities when subtracting one binary digit from another are:

0 - 0 = 0 0 - 1 = 1, borrow 1 1 - 0 = 11 - 1 = 0

We can subtract by repeatedly applying these rules to two binary numbers, starting at the rightmost end, just as in addition. Again, subtract the two bits in the operands first, then subtract any borrow from the result. When the result of subtracting two digits is a 1 and a borrow is applied, the result becomes 0; when the result of subtracting two digits is a 0 and a borrow is applied, the result is 1 and a further borrow is generated.

1100110 110001 110101 Here's how an internal dialogue of someone doing this subtraction in his or her head might go:

| "Ones position:       | 0 - 1 | = 1, borrow 1.                         |

|-----------------------|-------|----------------------------------------|

| Twos position:        | 1 - 0 | = 1, subtract borrow, result is 0.     |

| Fours position:       | 1 - 0 | = 1.                                   |

| Eights position:      | 0 - 0 | = 0.                                   |

| Sixteens position:    | 0 - 1 | = 1, borrow 1.                         |

| Thirty-twos position: | 1 – 1 | = 0, subtract borrow, result is 1 with |

|                       |       | a borrow of 1.                         |

| Sixty-fours position: | 1 - 0 | = 1, subtract borrow, result is 0."    |

|                       |       |                                        |

This is the equivalent of subtracting 49 from 102, with the result (32 + 16 + 0 + 4 + 0 + 1 =) 53, as expected. This process is complicated enough that people often do binary subtraction by converting both operands to decimal, doing the subtraction, then converting the result to binary again. Another technique is to convert the second operand to its opposite (negate it), then add the two numbers together, using the addition technique. This is the technique used inside the 80386 and other processors in its family.

#### **Negative Binary Numbers**

So far we've only dealt with positive numbers, and we've used as many bits to represent a number as it needed; the first bit is always 1, because it's useless to write leading zeros. In most systems which can handle positive and negative numbers, however, a leading 1 always indicates a negative number. In order to express both kinds of numbers, we agree in advance that all numbers will be (for example) eight bits long, and that leading zeros will be written out, as in 00000100 (the binary representation for 4 in decimal).

Several different ways exist to describe negative numbers. The simplest is to put an additional bit in front of each number to represent the sign of the number, a 0 bit for positive, a 1 bit for negative, with the bits after the first one representing the number's size. This is called "sign-magnitude representation," meaning "a sign bit in front, plus several bits to represent the magnitude." However, the addition and subtraction rules described above, which are the simplest possible, don't work for sign-magnitude numbers unless adjustments are made. Another problem is that there are two equivalent ways to represent zero: 00000000 (or 0), and 10000000 (or "negative zero"); both mean the same thing. The floating-point representation described above is a modified form of sign-magnitude representation; it's compact but difficult for doing arithmetic.

Inside the 80386, as in most computers, negative numbers are represented by a method called "two's complement" notation. We use this notation because the same simple math rules apply to both positive and negative two's complement numbers. Positive numbers in two's complement are exactly the same as in regular binary notation: 4 decimal is 00000100 binary; 11 decimal is 00001011 binary. Zero is 00000000.

To form a negative number we construct a positive number of the same magnitude and then flip (i.e., negate or invert) every bit, which yields "one's complement" notation, then add one to this result. Here are two examples of forming negative two's complement numbers:

| Start with decimal number:           | -4       | -11      |

|--------------------------------------|----------|----------|

| Write out positive number in binary: | 00000100 | 00001011 |

| Negate each bit (one's complement):  | 11111011 | 11110100 |

| Add 1 (two's complement):            | 11111100 | 11110101 |

There are a couple of things worth noting. Each negative number in two's complement starts with 1, so the lead bit serves as a sign bit; the negative numbers work fine for the computer but are hard for a person to convert to decimal. The simplest way to do this for negative two's complement numbers is to find the absolute value of them by reversing the process above: negate each bit and then add 1 to get the positive component (magnitude or absolute value) of the negative number. The resulting positive binary number is then easy to convert to decimal.

Here are two examples of arithmetic with two's complement numbers:

| 11001000 (56)            | 11101111 (—17)          |

|--------------------------|-------------------------|

| + <u>01101001 (</u> 105) | - <u>00000011 (</u> +3) |

| 00110001 (+49)           | 11101100 (—20)          |

Both follow the same arithmetic rules as the positive (i.e., unsigned) numbers we dealt with before. In the rest of this book a two's complement number will also be called a signed number, meaning a binary number in which the high-order (leftmost) bit serves as a sign bit.

#### **BINARY MATH APPLICATIONS**

#### **Overflow and Carry**

When the 80386 performs a math operation (like an add or subtract) it uses a special piece of hardware called an adder, which handles only a couple of different operations, but performs them very quickly. The 80386 can perform up to 8 million simple additions in a second.

However, sometimes even a simple operation like addition can get complicated. When we add two unsigned numbers the result can be too large to fit in the number of bits available. For example, 10000001 (129 decimal) + 01111111 (127 decimal) = 1 00000000 (256 decimal), which doesn't fit in eight bits. The adder will return a result of 00000000, which is not what we expect.

To communicate that a problem has occurred, the adder sets an extra bit inside the microprocessor (called the "carry flag"). This flag is set (to 1) if the result of an addition doesn't fit in the number of bits available for the result, and is cleared (to 0) otherwise.

In a signed number only the low-order (leftmost) seven bits contain a number's value; the high-order bit is reserved for the sign. The equivalent of a carry (magnitude too large to fit the representation) occurs when adding two seven-bit numbers gives a result that won't fit in seven bits. For example, 01111100 (124 decimal) + 00001111 (15 decimal) = 10001011 (-11 decimal), which is not right at all. This forced changing of the high-order bit, caused by the sum of the remaining bits being too large, is called an overflow. There's a flag in the 80386 (called the "overflow" flag) that is set any time the result in the first seven bits changes the eighth bit, and cleared otherwise. The overflow can be ignored when we're dealing with unsigned numbers. To summarize, a carry is caused by a carry out of the leftmost bit, and an overflow is caused by a forced change of the high-order bit.

The exact conditions under which each flag is set can be important, and there are other flags in the chip that depend on the results of

19

arithmetic, as do carry and overflow. These are discussed in detail in Chapter 2.

#### Sign Extension

So far all our examples of binary math have dealt with numbers that can be represented in an eight-bit byte. The 80386 also uses words (two bytes) and doublewords (four bytes) in its hardware. Often, we need to convert a byte to a word or doubleword (called a dword).

This is simple for positive numbers; just add zeroes to the left end of the number. The byte 00010011 (19 decimal) becomes the word 00000000 00010011 (19 decimal), for instance. Negative numbers in two's complement representation are a little more complicated. If we add zeroes to the left end of a negative number, it changes completely; 11101101 (-19) decimal) becomes 00000000 11101101 (237 decimal). Luckily, there is a simple rule called sign extension that fits smaller operands into larger ones while preserving both magnitude and sign. Just take the leftmost bit of the smaller data type (i.e., byte or word) and repeat it in the extra bits of the larger data type (i.e., word or dword). The byte 00010011 (19 decimal) still becomes 00000000 00010011 (19 decimal), but the byte 11101101 (-19 decimal) becomes 11111111 11101101 (-19 decimal) as a word. The 80386 allows you to either zero extend (the added bits become zeroes) or sign extend (the added bits are copies of the leftmost bit) when moving a byte into a word or a doubleword, or moving a word into a doubleword.

#### **Binary Logic**

Some words we use somewhat loosely in English (such as "and," "or," and "not") have precise meanings in computer math as logical operators on numbers. Listing 1-5 shows what different logical operators do when applied to different combinations of bits.

One way to remember these rules is to think of the 0's as representing false English statements (like "all hair is green") and the 1's as representing true statements (like "the earth is round"). Substitute these statements for the 0's and 1's on the left hand side of the equations in Listing 1-5 to make sentences. The equation is true if the resulting sentence is also true. For example, 0 AND 0 becomes "all hair is green AND the earth is round;" this is false because all hair isn't green. NOT 0 = 1 NOT 1 = 0(result is opposite of operand) 0 AND 0 = 0 0 AND 1 = 0 1 AND 0 = 0 1 AND 1 = 1(result is 1, or True, if and only if both operands are True) 0 OR 0 = 0 0 OR 1 = 1 1 OR 0 = 1 1 OR 1 = 1(result is 1, or True, if either operand is True) 0 XOR 0 = 0 0 XOR 1 = 1 1 XOR 0 = 1 1 XOR 1 = 0(result is 1, or True, if one and only one operand is True)

Listing 1-5. Binary Logic

This trick doesn't work as well for XOR, which is short for "eXclusive OR" and means "either one, but not both." As we start using non-English constructions like XOR and construct statements that combine two or more operators in one statement (NOT 0 OR 1), it becomes easier to simply memorize and apply rules like those in Listing 1-5 than to construct increasingly convoluted sentences as examples.

We can apply these logic rules to bytes as well as bits. Simply line the bytes up as if you were going to add them, then use the rules above on each pair of bits in turn. Since there is no carry, it doesn't matter whether the comparisons start with the two leftmost bits or the two rightmost bits. Listing 1-6 shows the results of applying the NOT, AND, OR, and XOR operators to byte operands.

These operators work the same way on operands of any number of bits as long as both operands are of the same length.

| NOT      | 11001010 AND    | 11001010 OR | 11001010 XOR    |

|----------|-----------------|-------------|-----------------|

| 01010110 | <u>01010110</u> | 01010110    | <u>01010110</u> |

| 10101001 | 01000010        | 11011110    | 10011100        |

Listing 1-6. Examples of NOT, AND, OR, XOR

# CHAPTER 2

### 80386 Applications Architecture

INTEL'S AND OTHER EARLY MICROPROCESSORS THE 8086 FAMILY MICROPROCESSOR BASICS THE FETCH-DECODE-EXECUTE CYCLE AND THE 80386 A BIT-BY-BIT LOOK AT EFLAGS FLAT AND SEGMENTED MEMORY

In this chapter we talk about the 80386's architecture, or the way its facilities look to the programmer trying to make the chip work. We start with a brief description of the history of the 80386, and an equally brief discussion of the functions of a typical microprocessor. This chapter concentrates on the facilities used by the applications programmer and describes each of the chip's registers, including those generally used only by operating systems. Also covered are interrupts and exceptions.

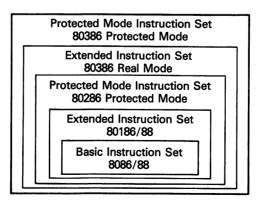

A program running in the 80386's Virtual 8086 Mode works almost exactly the same as one running in Real Mode, and both are well suited for bringing 8086 programs and operating systems, and 80286 Real Mode programs, onto the 80386. Programs running in Protected Mode have access to all the facilities in Real Mode (as described here) plus those available in Protected Mode. An understanding of the material here is necessary for using any of the modes and capabilities of the 80386.

We start with some background on the evolution leading up to the Intel 8086 family and the 80386. This gives some insight into why the 80386 works the way it does and what the future may hold. Next, we'll talk about what a microprocessor is and what parts make it up. Following this is the bulk of the chapter, which is about the 80386's internal organization, how it looks at memory, and the data types and addressing modes it uses in talking to memory. This chapter covers all registers and addressing modes except the ones only accessible through Protected Mode. Some of the material here, though, can be skimmed by the experienced 8086 and/or 80286 programmer, since much of the 80386 design is an extension of these earlier microprocessors.

#### INTEL'S AND OTHER EARLY MICROPROCESSORS

The 4004 from Intel (the first general-purpose microprocessor) appeared in 1971. Like the later examples of its type, it could execute any program made up of the right commands, bring data in, operate on it, and send data back out. All this was done by a concatenation of electrical components about the size of a quarter. The 4004 operated on four bits of data at a time, with each four bits encoding a single decimal digit, as in BCD math (Chapter 1). The 4004 was originally designed for use in calculators. It contained the equivalent of about 1,000 transistors and performed 8,000 operations in a second, easily fast enough for calculator use.

Within the next couple of years Intel introduced two new microprocessors, the 8008 (basically a 4004 which processed eight bits at a time) and the 8080 (the first chip powerful enough to run a small computer). The 8080 (which is still popular for process control and other applications) includes facilities for performing decimal and 16-bit math, making subroutine calls, and addressing memory up to 64 Kb. The 8080 uses an 8-bit data path and a 16-bit addressing bus, meaning it can handle numbers and addresses up to 64 K (2 to the 16th) easily.

A group of Intel engineers left their company to form Zilog (just as Intel itself was formed by ex-Fairchild Semiconductor people) and in

25

1976 introduced the popular Zilog Z80. This did everything the 8080 does and then some, adding additional instructions and registers. However, so many 8080-based computers existed by this time that most programs were still written to run unchanged on both the Z80 and the less powerful 8080, maximizing market share but sacrificing performance. Computers which run the once-popular CP/M operating system tend to have some version of the 8080 or Z80.

Other companies weren't oblivious to the progress and sales made by these new chips. In 1974 Motorola introduced the 6800, which was as powerful as the competition and added new ways to address data, speeding program development and execution. In 1975 some ex-Motorola engineers produced the first processor in the 6500 series, which was similar to but cheaper than the 6800. The MOS Technologies 6502 and its descendants are found in the Apple II series of computers.

In 1980 Motorola came out with the 68000, a 16/32 bit chip which mostly handled 16-bit values but had some ability to process 32 bits internally and used 32-bit addressing to directly address up to 4 billion bytes of memory. The 68000 could handle about 800,000 operations per second. Its descendants include the 68010, the 68020, and the brand new 68030; each of the chips in this family powers both microcomputers and minicomputers. The 68000 series is currently the main competition in sales and capability to the 8086 family.

In the decade between the 4004 and the 68000, microprocessors improved dramatically in most respects; about 70 times as many transistors could be found on a chip, the largest available word size had climbed from 4 bits to at least 16 bits, and the speed of operation was increased over 100 times. Although some physical limitations of chip construction were approached, the size of the market has increased enough to inspire a similar rate of improvement in this decade, as reflected by the 80386. What the future holds is anyone's guess.

### THE 8086 FAMILY

In 1978 Intel introduced the 8086, followed a year later by the 8088. The 8086 is a 16-bit chip (in the data sizes it processes internally and in the size of words its data bus brings in from memory). However, the address size used is 20 bits, so 1 megabyte (2 to the 20th power) can be addressed directly, but only in 64 Kb chunks. The 8088 works just like the 8086, but its data bus is only 8 bits wide. When the 8088 needs a 16-bit quantity it must get it in two 8-bit chunks, slowing operations. When processing data internally or working with byte-sized data, the 8088 is just as fast as the 8086 and has the advantage of being able to work with inexpensive 8-bit memory chips and other peripherals designed for older microprocessors. It is irritating to the experienced 8088 programmer to find repeated references to the "8086" or the "basic architecture" in technical documents and books. All this means is that the 8086 is the model which must be emulated by other members of its family to preserve compatability. The 8088 is identical to the 8086 in every way but the size of its data bus. Any reference to the 8086 mean "the 8086 and the 8088" unless specified otherwise.

In discussing the 80386's operations in Real Mode we will largely be talking about the capabilities of an 8086. The instruction set is somewhat extended on the 80386; several new registers have been added, as has 32-bit capability. However, the 8086 programmer has only a short learning curve to traverse before learning to program the 80386 in Real Mode.

## MICROPROCESSOR BASICS

Every computer has at its heart a central processing unit with the computer's arithmetic and logic control circuitry. A microprocessor is a central processing unit (CPU) fitted onto one (or at most a few) silicon chips. The small size of the microprocessor is less important than its low cost, which makes possible low computer prices and therefore the recent explosion in small computers.

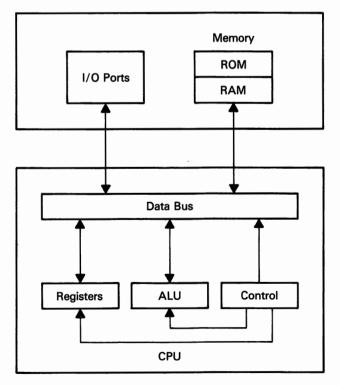

From a programmer's point of view the basic workings of a microprocessor are the same as the basic workings of any other CPU. The two necessary parts of a CPU are an arithmetic/logic unit (ALU) that performs arithmetic operations, and a control unit (CU) that brings data to the ALU and otherwise directs the moving of data within the computer. In order to speed up operations most CPUs contain registers, which are quickly accessible storage locations. Some of the registers are used mostly by programmers, while others are reserved for use by the control unit.

One of the two remaining parts of a computer is the memory, which holds programs and data. There are two types of memory we're concerned with on the 80386: random access memory (RAM), which the

27

programmer can both write data to and read data from, and read-only memory (ROM), which can only be read. RAM generally loses its contents when power is turned off or the computer is rebooted, while ROM keeps the same contents at all times. The other parts of a computer in which we are interested are its I/O ports, through which data is sent and received between the CPU and the outside world. Figure 2-1 depicts the relationship between these different parts of the computer.

The distinction between memory and I/O ports is becoming blurred because much I/O is memory-mapped; the contents of locations in RAM control what is output (memory-mapped video displays) or reflect what is input (memory-mapped keyboard input). In these cases I/O is handled just by reading and writing values in memory put there automatically by an input device or transferred automatically to an output device. The only other use of I/O by many programs is to write to and read from a disk. This is largely accomplished by calls to the operating system, which accesses code in ROM to make the transfers.

Figure 2-1. The CPU plus I/O and memory

28

Data movement inside the computer is done at the command of the control unit on the CPU, and goes through the data bus (which is like a parallel port between the CPU and the memory and I/O ports). The computer's registers and ALU are each connected directly to one end of the data bus, while memory and I/O are connected to the other. The control unit directs the placing of data on (and reading of data from) the bus by the CPU.

When a computer is referred to as a 16-bit or 32-bit computer, this refers to the number of bits which fit in its internal registers. Almost as important as the register size is the width of the data bus. When the 8088 is referred to as an 8/16-bit computer, this means it has an 8-bit data bus and a 16-bit internal register size. The 80386 is a "true 32-bit" computer, meaning that its registers and data bus are all 32 bits wide. The 80386 also has a 32-bit address bus, making address calculation much easier, because a single register can hold a complete address.

The 80386 is highly integrated; it has its CPU (including ALU and registers) and memory management unit (discussed in detail below) all on a single chip. This is a real achievement for a 32-bit processor. Main memory (RAM and ROM) and I/O ports are not on the microprocessor chip.

There is much we haven't discussed here: the timing of the different signals that control data movement and other chip functions, how the 80386 communicates with memory, and how a computer is physically organized into circuit boards, buses, and so on. Many of the hardware details are covered in Chapter 7. Communications with memory are covered below; the other chips found in a typical 80386-based computer aren't discussed here, because they change as new, more highly integrated support chips become available.

## THE FETCH-DECODE-EXECUTE CYCLE AND THE 80386

Most computers in current use execute one instruction at a time. A regular order of events is repeated for each instruction: an instruction is fetched from memory, the instruction is decoded (translated from 0s and 1s into the microcode used inside the CPU itself), and then the microcode is executed. This is called the fetch-decode-execute cycle.

There are a couple of additional considerations on most computers. During fetching a register called the Program Counter is automatically incremented. The Program Counter tells the computer where to look for its next instruction. As the counter is incremented by the same amount for each fetch, instructions are executed in the order in which they're stored in memory. This only changes when a "jump" instruction or a "call" to a subroutine forces a brand new value into the Program Counter, causing the program to get its next instruction from some new location.

The other consideration is that many instructions have operands that are stored in memory when the instruction is brought into the CPU. For instance, an ADD instruction might add two numbers, one of which is in memory. The value in memory must be brought into the ALU so it can be operated on. Thus, the fetch-decode-execute cycle comes to look more like a fetch-increment program counter-decode-get operand from memoryexecute cycle. Instructions with an operand in memory can start taking a long time to complete.

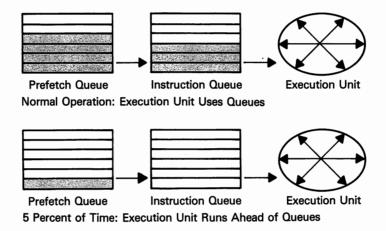

The 80386 gets around this complication by using a technique called "pipelining." While one instruction is being fetched another is being decoded and a third is being executed. Five or six instructions are typically in one or another of these stages at any given time. Pipelining is discussed in great detail in Chapter 7; the important thing to understand for now is that most of the time the 80386 finishes executing one instruction and then immediately starts executing a new one that has already been fetched and decoded.

## The 80386 Processor

The 80386 processor is divided up into functional pieces called "units." The only one the programmer has direct control over is the Execution Unit, which contains the chip's onboard storage registers and arithmetic hardware, plus the controller that actually causes instructions to execute. Besides the chip the most important element of the computer is main memory, usually in the form of RAM. In the rest of this chapter we're going to talk a little bit about the 80386's ALU, and a lot about its registers and communications with memory. The areas talked about the most are the ones that an applications programmer has the most control over.

The 80386's Execution Unit includes a fast adder, which works with 32-bit values, and a 64-bit barrel shifter, which can shift or rotate a 32-bit operand by up to 31 bits in either direction. The important thing to know for programming purposes is that adds and shifts are among the fastest instructions, especially if the operands are in registers.

## The 80386's Applications Register Set

The 80386 has many registers; most are accessible to applications programmers, a few are used only by systems programs. The applications register set includes the general registers, the segment registers, the flags register, and the instruction pointer. These are discussed below.

"Base register set" is another term used to describe some of the registers found on the 80386. The base register set is a core group of registers that are found on each and every member of the 8086 family. These include the lower 16 bits of the applications registers along with the machine status word (covered in Chapter 6).

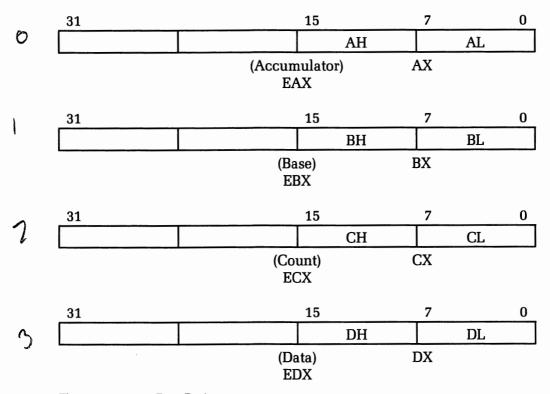

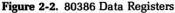

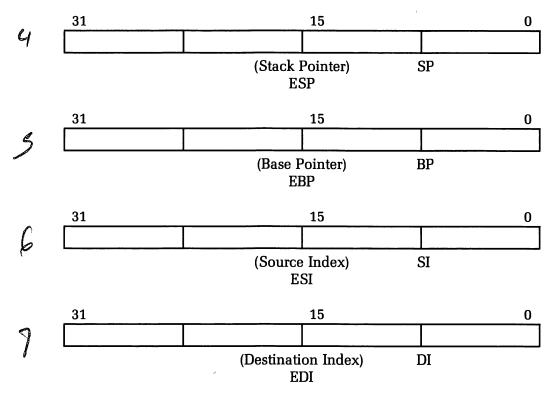

The 80386 has eight general registers. The registers are each 32 bits wide. The full 32-bit registers have names starting with E (for Extended): EAX, EDX, ECX, EBX, EBP, ESI, EDI, and ESP (Figures 2-2 and 2-3). The lower 16 bits of each of these registers can be addressed using the same

Figure 2-3. 80386 Pointer and Index Registers

names as on earlier 8086-family chips: AX, DX, CX, BX, BP, SI, DI, and SP (the same names without the E). Finally, the first four 16-bit registers can each be addressed pairs of byte-sized registers: AH and AL name the high (bits 8 through 15) and low (bits 0 through 8) halves of AX; the same pattern is used for DH and DL, CH and CL, and BH and BL, each naming one of the two bytes in the corresponding 16-bit register.

All of the registers are doubleword addressable (names starting with E, for Extended); they are accessible as full-sized 32-bit registers. For a register to be "dword addressable" means that a single command (for example, MOV EAX, 1) affects a whole doubleword (or dword). The lower half of each register is word addressable (accessible as a 16-bit register). A dword-sized register that is "word addressable" can have values put in its lower word without affecting the upper 16 bits of the dword. When we wish to refer to a register in either its 32-bit or 16-bit form (whichever is more convenient for the programmer) we put the E in the name in

Ň

parentheses: (E)AX means "EAX or AX, whichever is needed." The first four registers are "byte addressable" in their first two bytes.

Despite the fact that these are general registers, each has specific uses. Operations like ADD allow the programmer to name any two registers as operands. Operations like PUSH, for instance, assume that the location in the stack which the operand will be pushed to is pointed at by SP. Because of this type of assumed use, each register is reserved for certain purposes when needed:

(E)AX, or the Accumulator register, is used for BCD math.

(E)BX, or the Base register, is used as a base for address calculations.

(E)CX, or the Count register, is used as a counter for string operations.

(E)DX, or the Data register, holds data for any of several different kinds of operations.

(E)SP, or the Stack Pointer, has the current offset of the top of the stack.

(E)BP, or the Base Pointer, can point to the base of a data area.

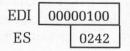

(E)SI and (E)DI, or the Source and Destination Index, are used when moving strings to point to the source string and the destination string.

Further details on the uses of each register are given in chapter 4.

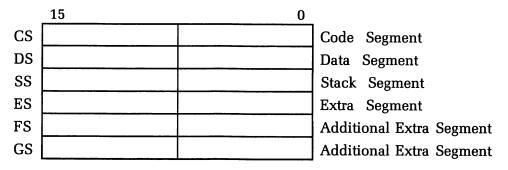

The segment registers on the 80386 are used to name the starting points in memory of different pieces of code and data (Figure 2-4). There are six segment registers, each with a different purpose. CS is the starting address of a program's code, DS of its data, and SS of its stack. ES, FS and GS are all extra segments for additional data structures; of these only ES is used specifically by certain instructions.

An applications program often doesn't need to modify the segment registers, which can be completely controlled by the operating system.

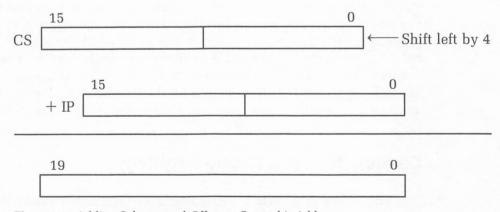

The contents of the segment registers are combined with other registers to tell the program where to get its next instruction (CS plus the Instruction Pointer), where the top of the stack is (SS plus ESP, the Stack Pointer), and so on. The exact way the two registers are combined varies depending on what mode your program is operating in, as explained below.

The final two registers of interest are EFlags, which controls some operations and indicates the current status of the 80386, and the Instruction Pointer, which is combined with the CS (Code Segment) register to point to the next instruction to be executed. Only some of the bits in EFlags (each of which has a different meaning) can be directly set by the applications programmer, and the Instruction Pointer can only be changed as a side effect of operations like jumps and calls.

## A BIT-BY-BIT LOOK AT EFLAGS

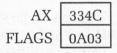

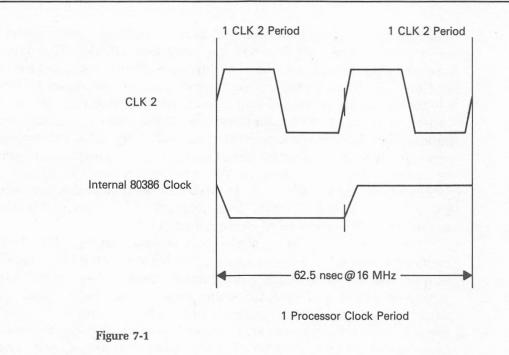

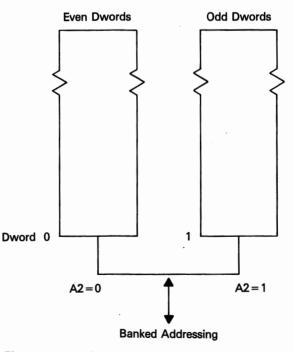

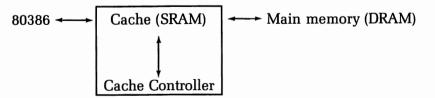

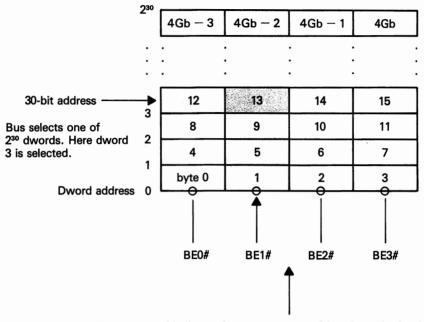

EFlags is the 80386's 32-bit-wide flags register. Applications deal only with the lower 16 bits of this, which are collectively called the Flags register. The bits in EFlags reflect the status of the 80386 and control the way some operations are performed.