# THE SOSSIBLE SOSS

**Russell Rector - George Alexy**

# THE 8086 BOOK

Russell Rector - George Alexy

OSBORNE/McGraw-Hill Berkeley, California

Published by OSBORNE/McGraw-Hill 630 Bancroft Way Berkeley, California 94710 U. S. A

For information on translations and book distributors outside of the U. S. A., please write OSBORNE/McGraw-Hill at the above address.

#### The 8086 Book

Copyright © 1980 McGraw-Hill, Inc. All rights reserved. Printed in the United States of America. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise without the prior written permission of the publishers.

1234567890 DODO 89876543210

ISBN 0-931988-29-2

Cover design by Joseph Mauro.

## Contents

#### Introduction

#### 1. Programming

Assembly Language 1-1

Programming Tasks 1-4

Specification of the System 1-5

Program Design 1-8

Implementation 1-9

Testing 1-12

Documentation 1-13

Maintenance 1-14

#### 2. Some Program Examples

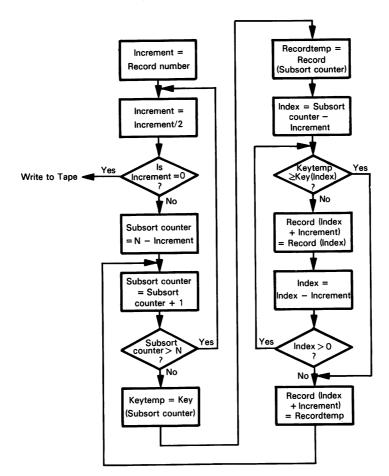

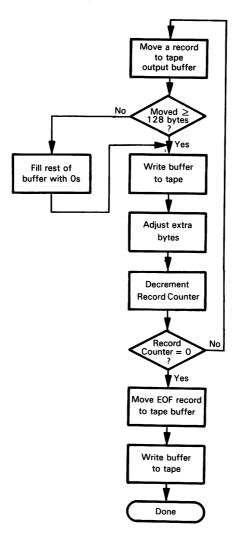

A Sort Program 2-1

Inputs 2-3

Computation 2-3

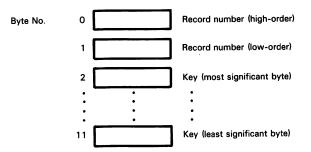

Input Record Format 2-3

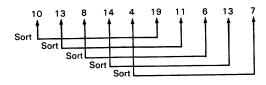

Sort Method 2-4

Output Record Format 2-6

Outputs 2-6

Error Processing 2-7

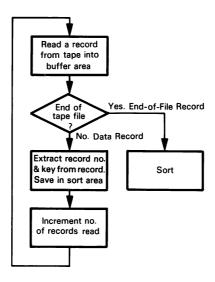

Program Design 2-7

#### 3. The 8086 Assembly Language Instruction Set

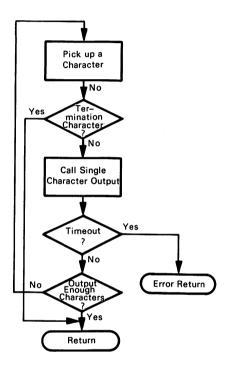

An I/O Driver 3-4

Computation 3-11

Outputs 3-11

Program Design 3-12

The 8086 Instruction Set 3-18

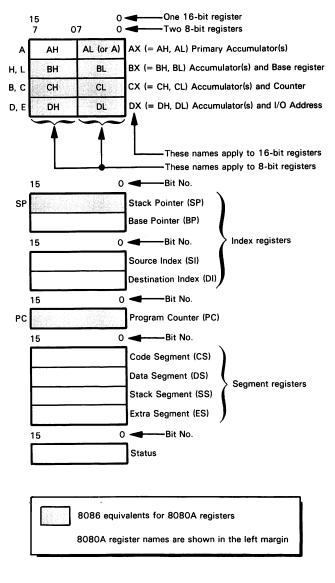

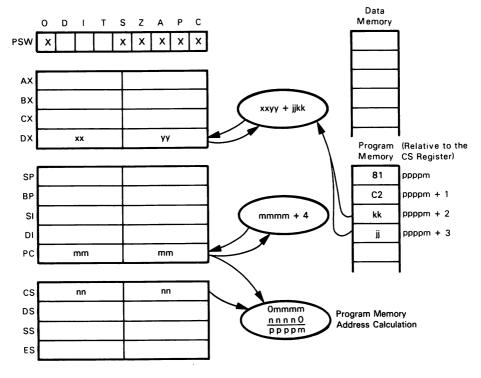

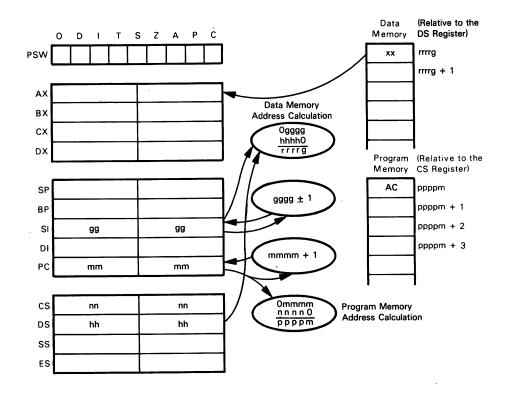

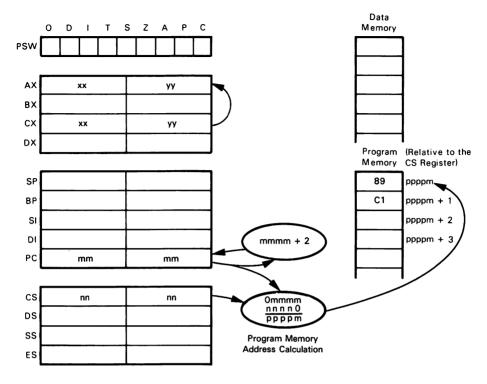

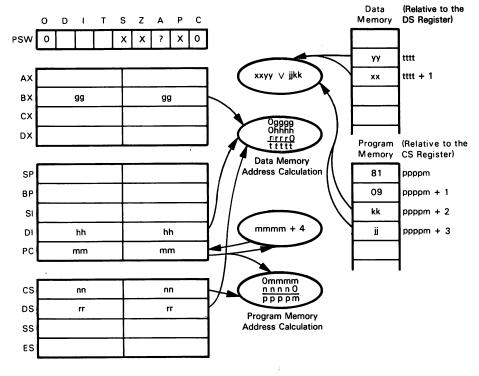

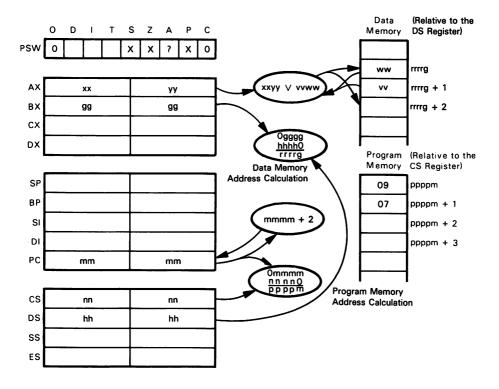

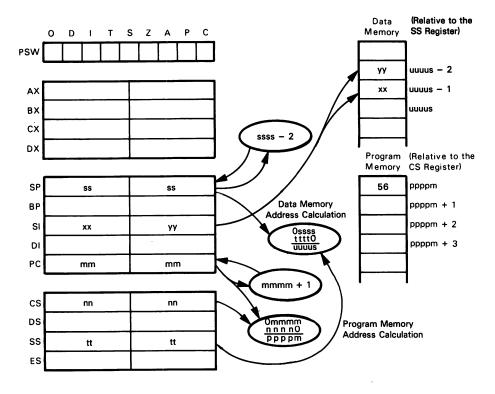

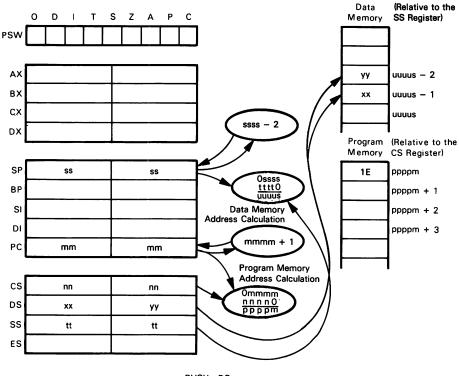

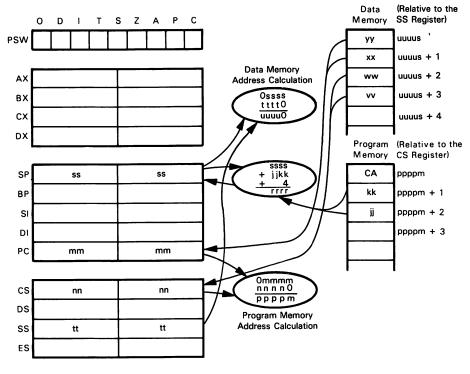

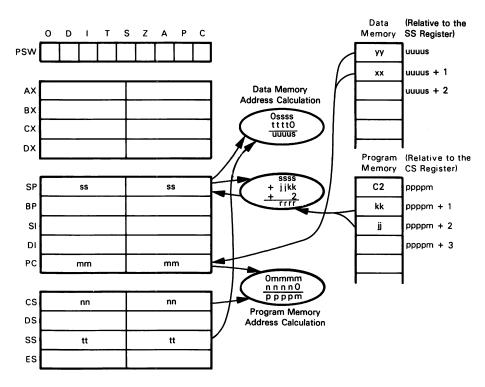

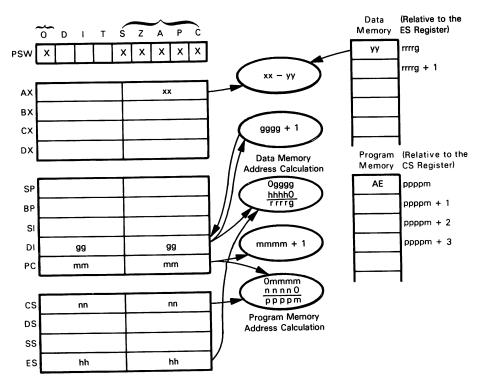

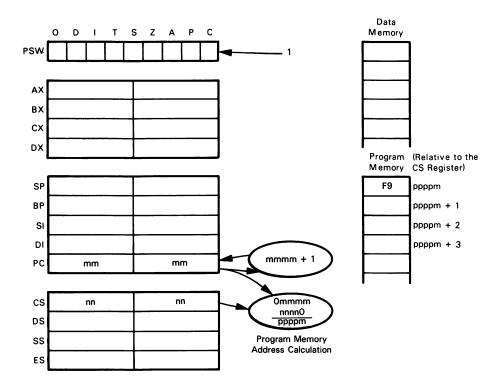

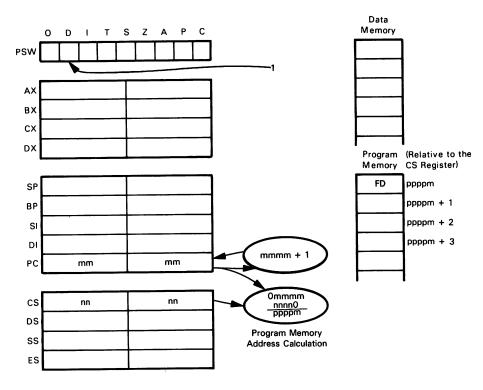

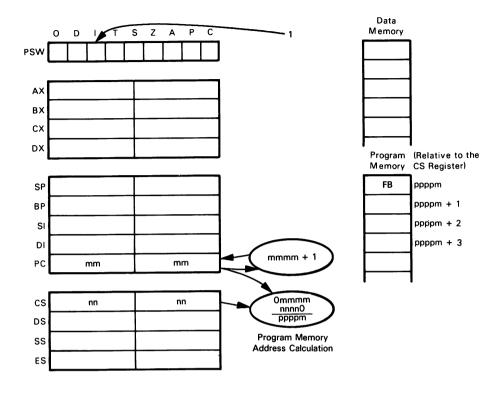

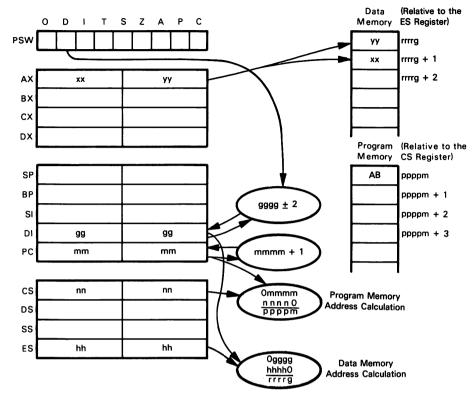

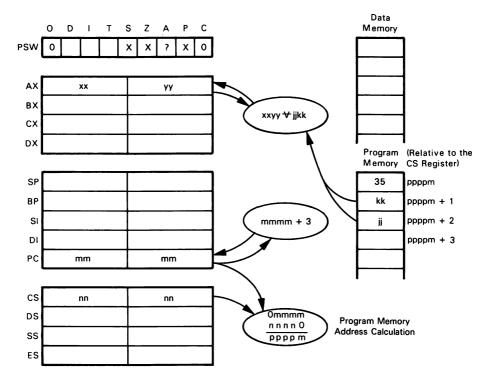

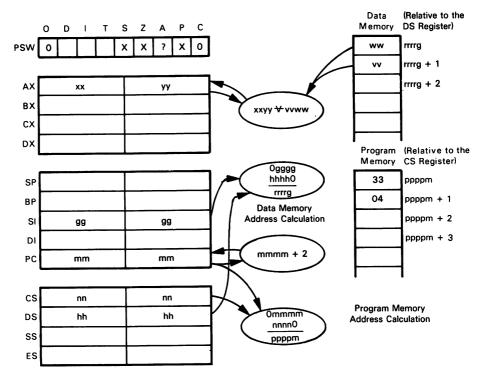

The 8086 Registers and Flags 3-20

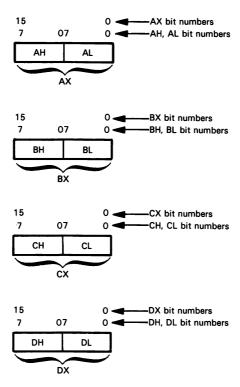

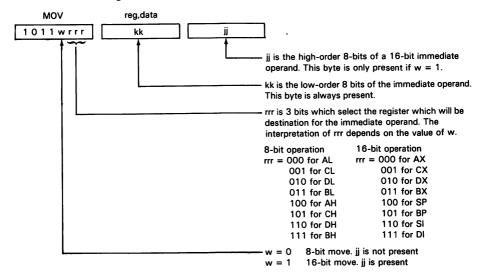

General Purpose Registers 3-21

Pointer Registers 3-22

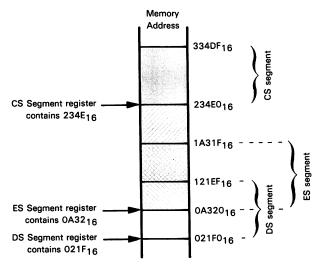

Index Registers 3-22 Segment Registers 3-22

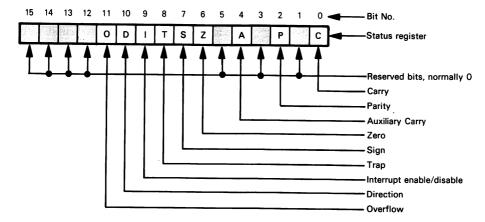

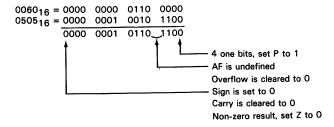

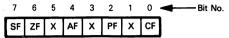

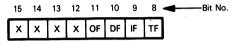

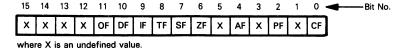

Flags Register 3-23

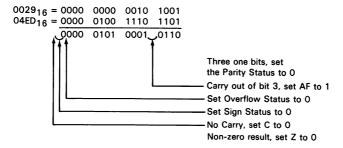

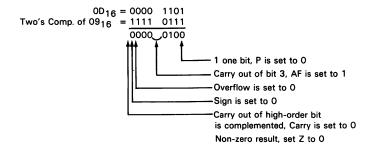

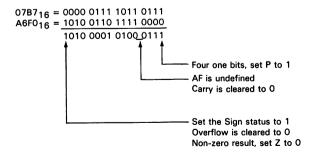

How Instructions Affect the Flags Register 3-25

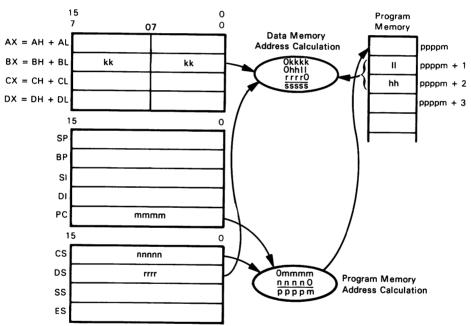

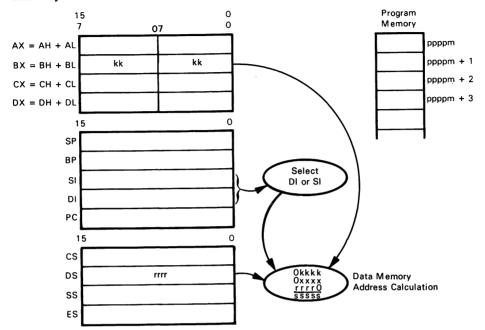

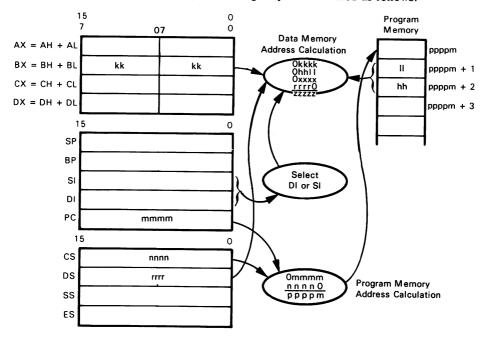

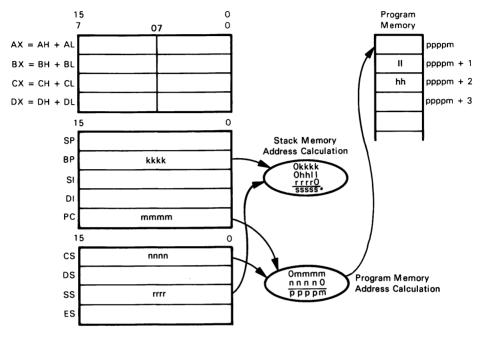

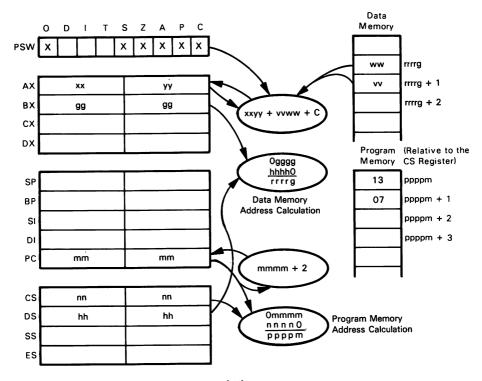

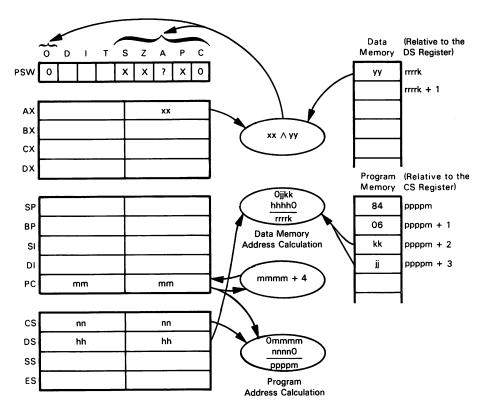

8086 Addressing Modes 3-30

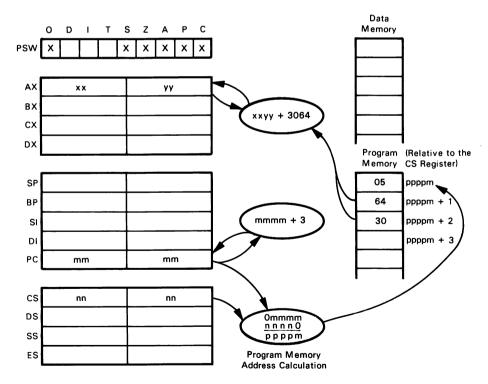

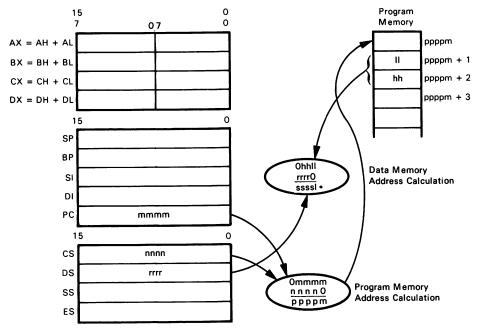

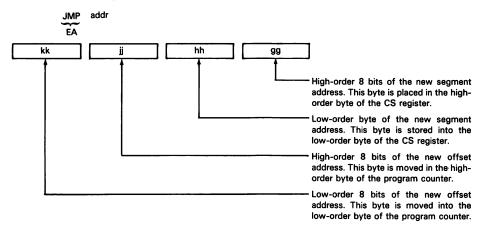

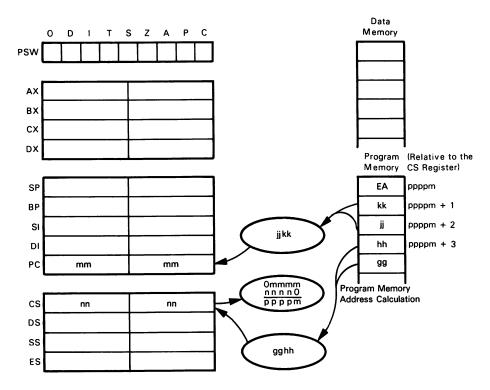

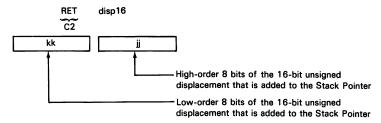

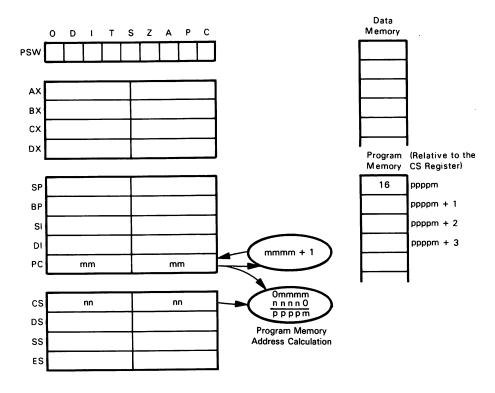

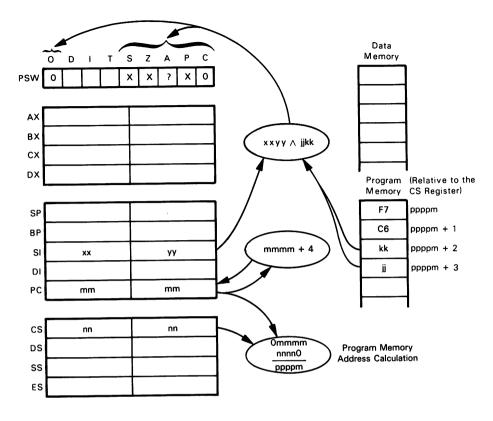

Program Memory Addressing Modes 3-31

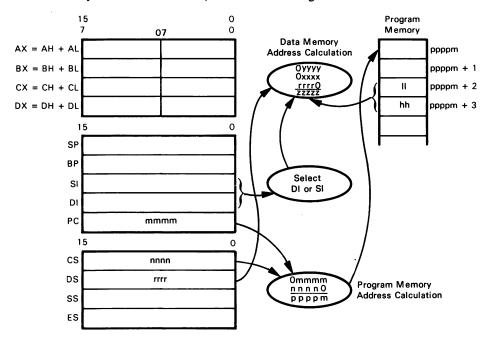

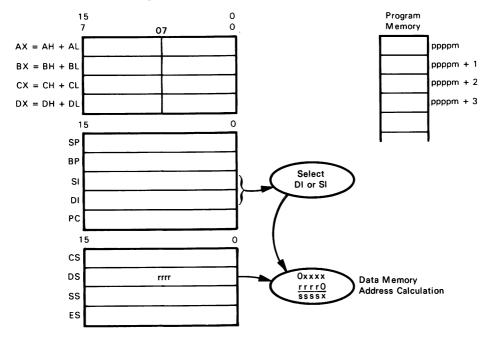

Data Memory Addressing Modes 3-32

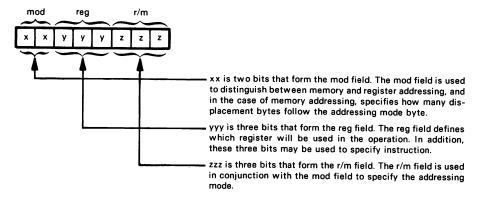

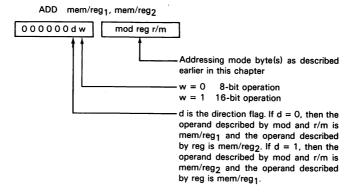

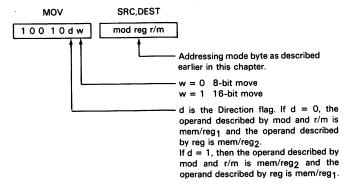

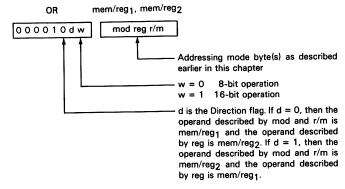

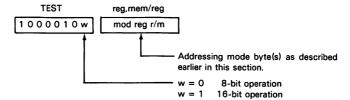

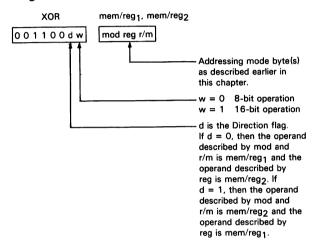

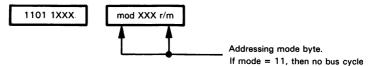

Addressing Mode Byte 3-41

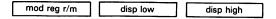

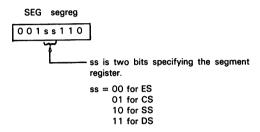

Segment Override 3-43

Memory Addressing Tables 3-44

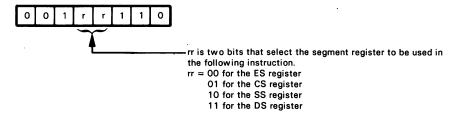

Instruction Set Mnemonics 3-45

Abbreviations 3-45

8086 Assembly Language Instructions Organized Alphabetically 3-49

Assembler-Dependent Mnemonics 3-285

#### 4. 8086 Instruction Groups

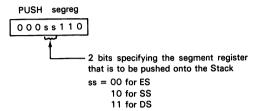

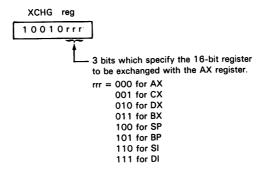

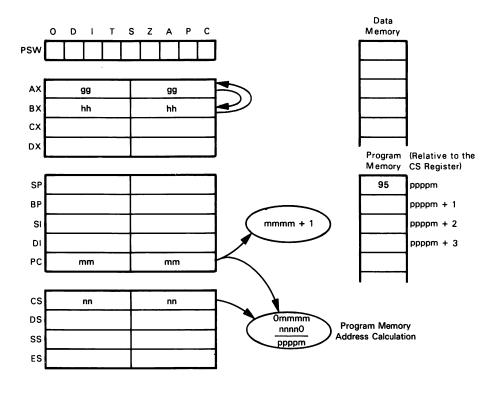

Data Movement Instructions 4-2

Buffer-to-Buffer Move Routines 4-6

Saving the State of the Machine 4-14

Segment Register Initialization 4-16

Arithmetic Instructions 4-17

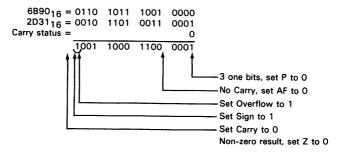

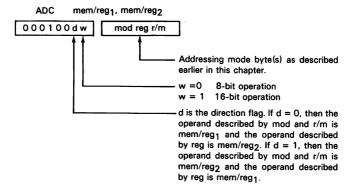

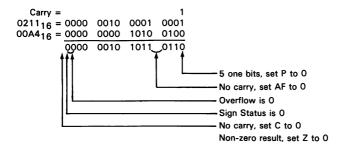

Addition Instructions 4-17

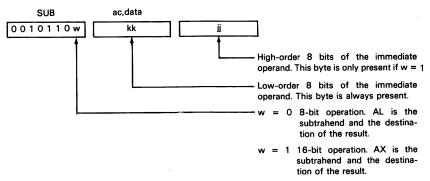

Subtraction Instructions 4-21

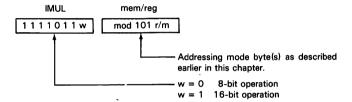

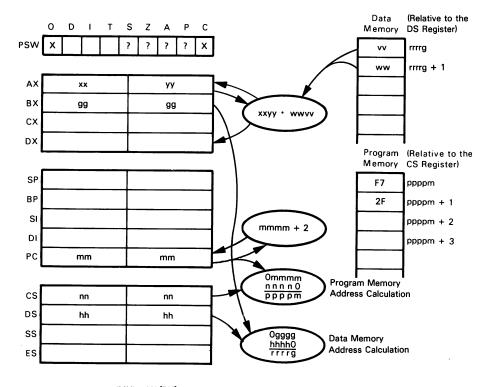

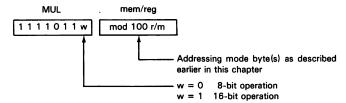

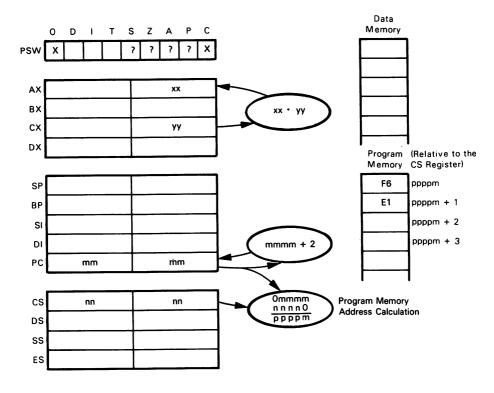

Multiplication Instructions 4-24

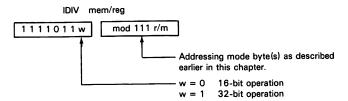

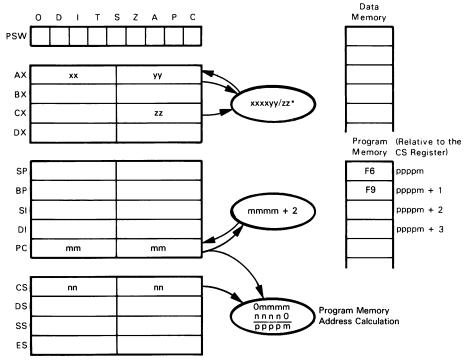

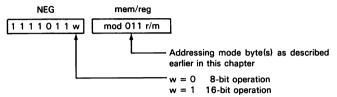

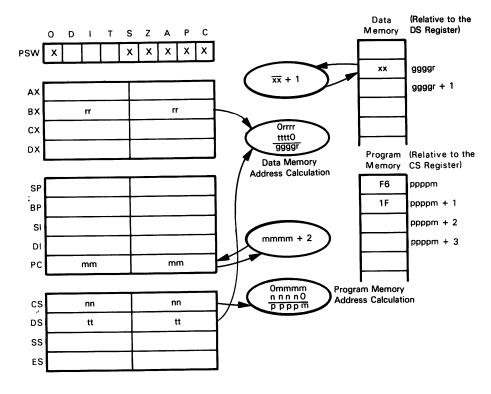

Division Instructions 4-28

Compare Instructions 4-31

Logical Instructions 4-35

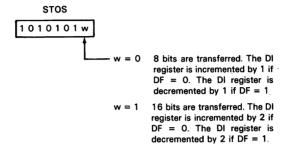

String Primitive Instructions 4-44

The REP Prefix 4-46

Program Counter Control Instructions 4-48

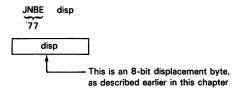

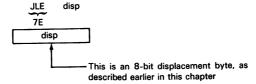

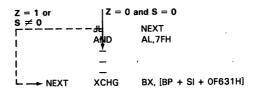

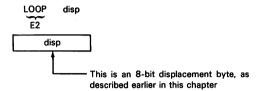

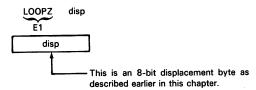

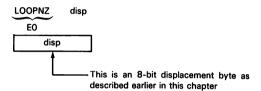

Jump-on-Condition Instructions 4-52

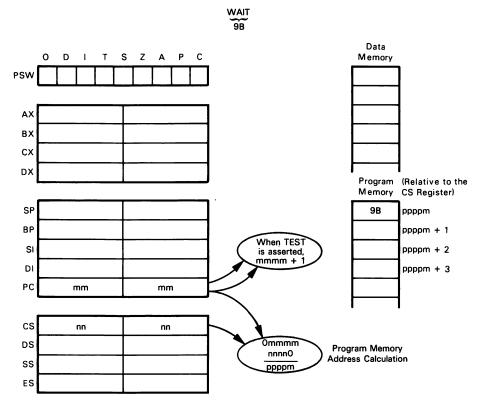

Processor Control Instructions 4-57

I/O Instructions 4-57

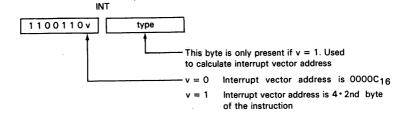

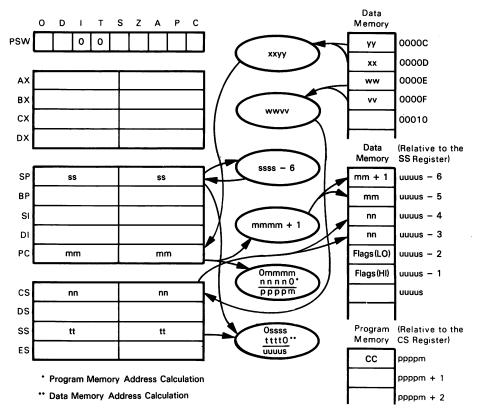

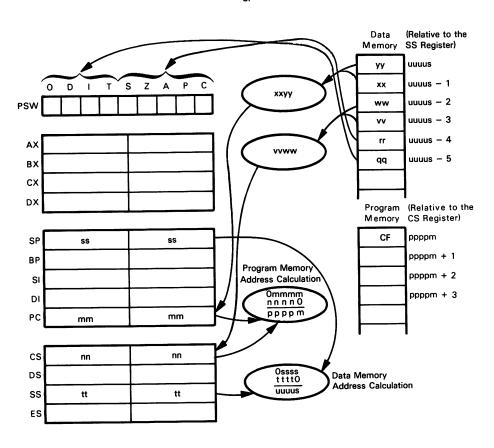

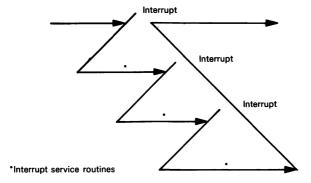

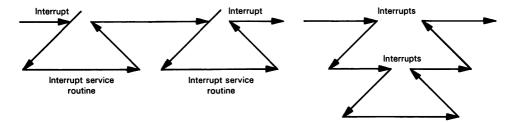

Interrupt Instructions 4-60

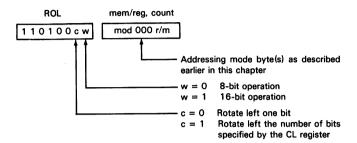

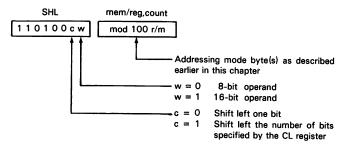

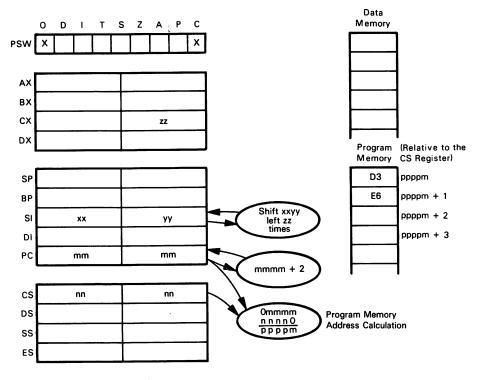

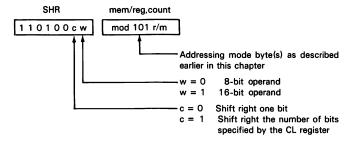

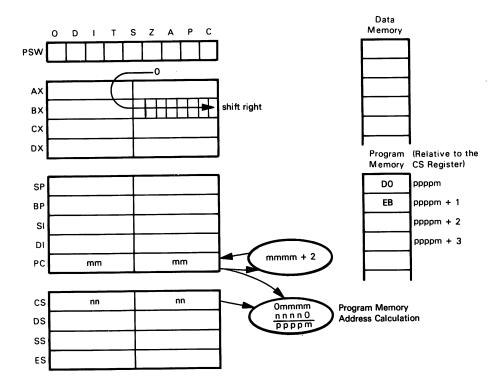

Rotate and Shift Instructions 4-62

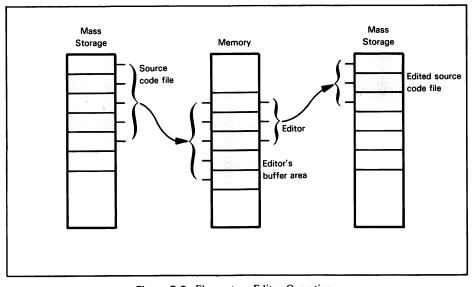

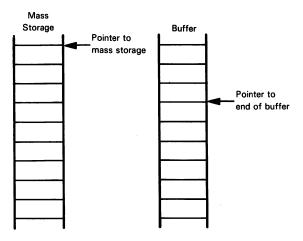

Editors 5-3

Editor Functions 5-4

System Commands 5-10

5. Software Development

Assemblers 5-11

Debuggers 5-13

#### 6. Examples of 8086 Assembly Language Programming

Sort Program 6-1 I/O Driver 6-9

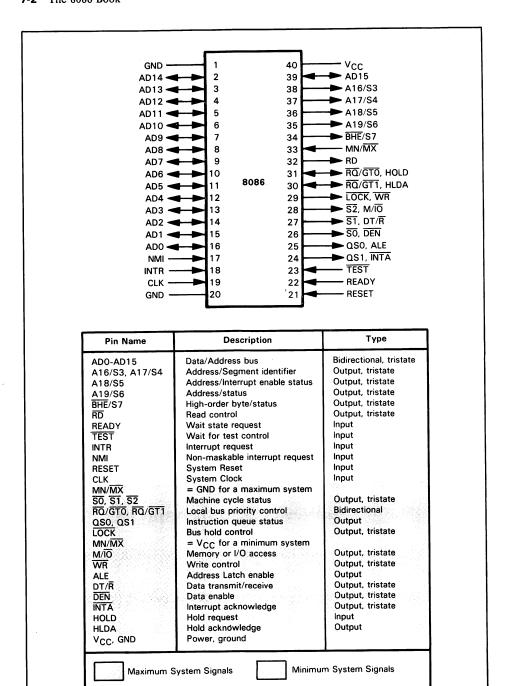

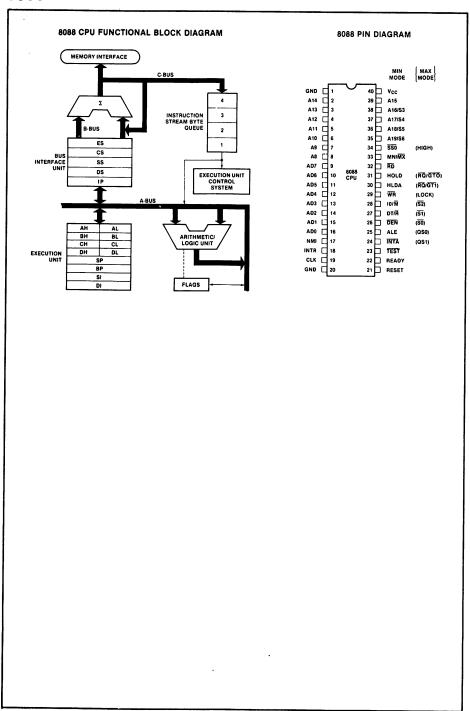

#### 7. 8086 Microprocessor Description

8086 CPU Pins and Signals 7-1

Address and Data Lines 7-3

Control and Status Lines 7-4

Power and Timing Lines 7-7

8086 Overview and Basic System Concepts 7-8

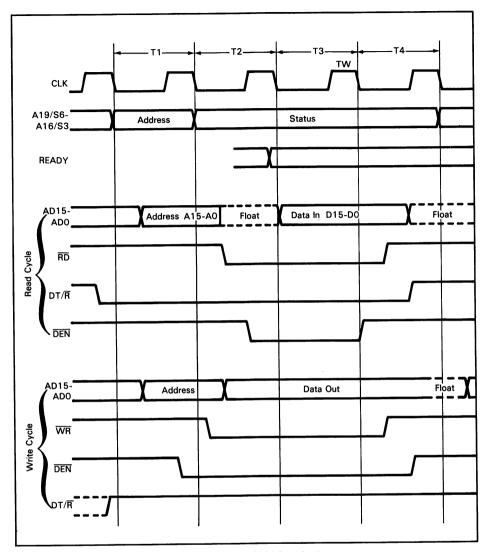

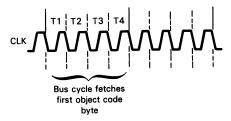

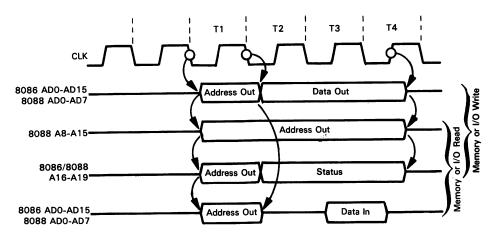

8086 Bus Cycle Definition 7-8

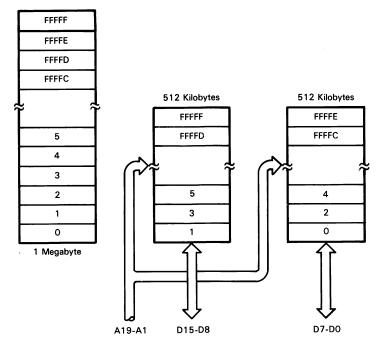

8086 Address and Data Bus Concepts 7-10

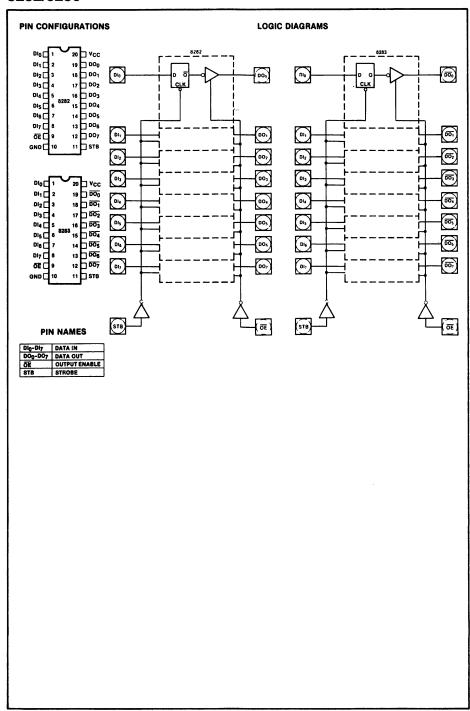

System Data Bus Concepts 7-16

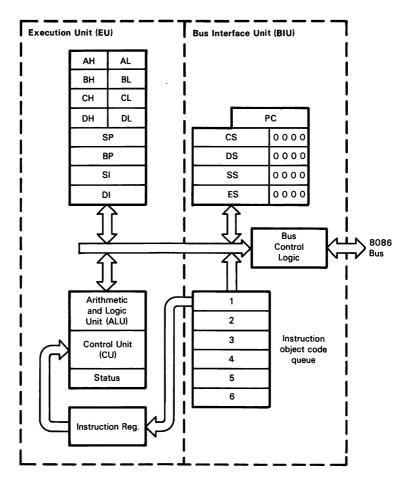

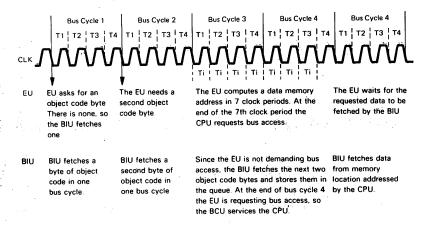

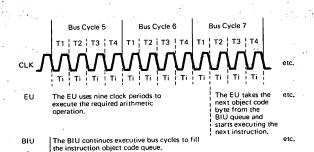

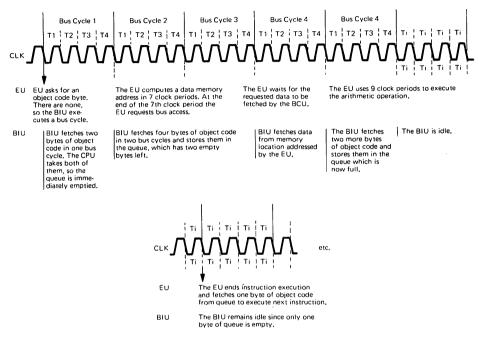

8086 Execution Unit and Bus Interface Unit 7-28

8086 Instruction Queue 7-29

#### 8. Basic 8086 Design Single CPU

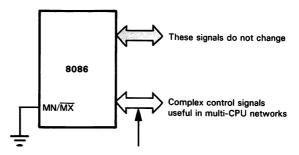

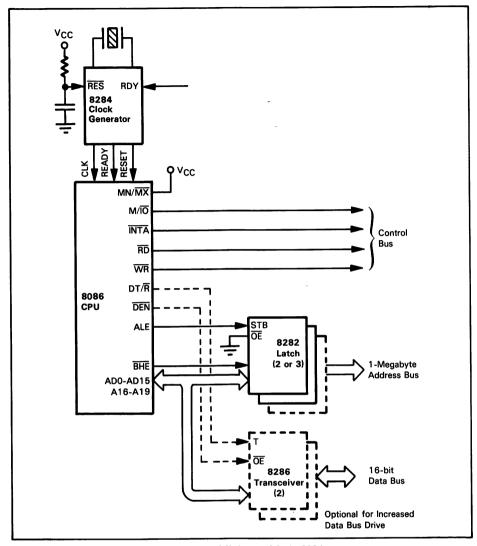

Operating Modes 8-1

Minimum Mode 8-1

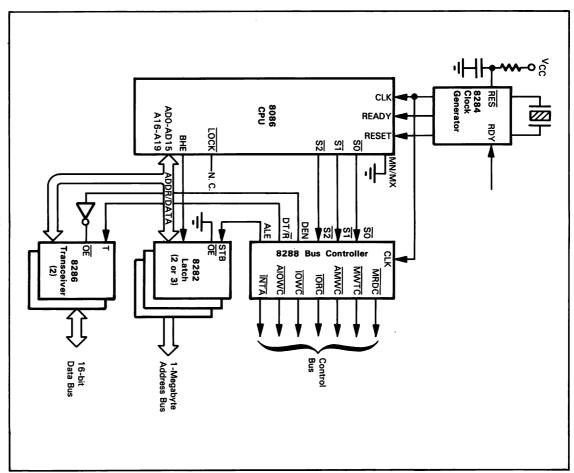

Maximum Mode 8-3

Clock Generation 8-11

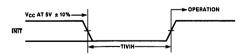

Reset 8-19

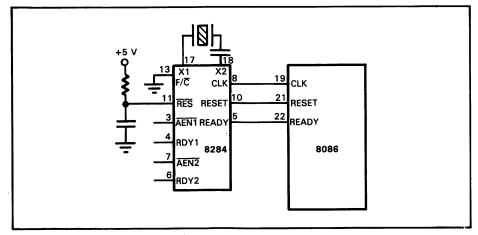

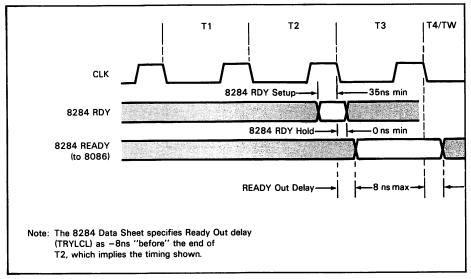

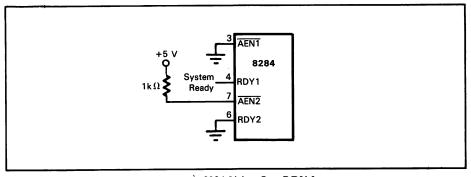

READY Implementation and Timing 8-24

Interrupt Structure 8-30

Predefined Interrupts 8-30

User-Defined Software Interrupts 8-33

User-Defined Hardware Interrupts 8-33

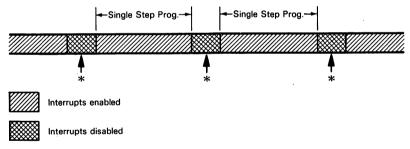

The Interrupt Acknowledge Sequence 8-34

System Interrupt Configurations 8-38

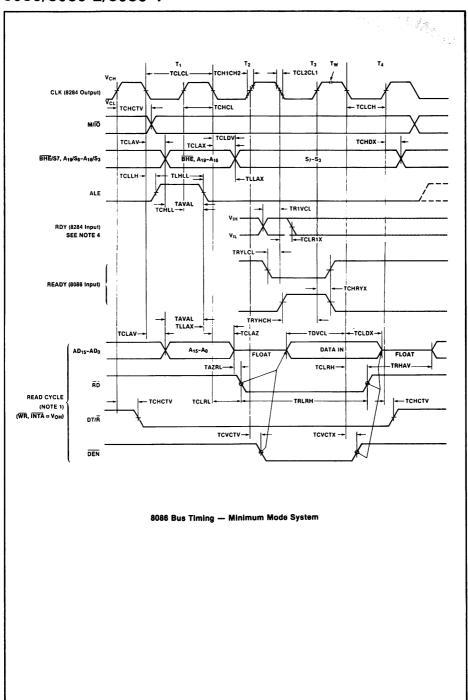

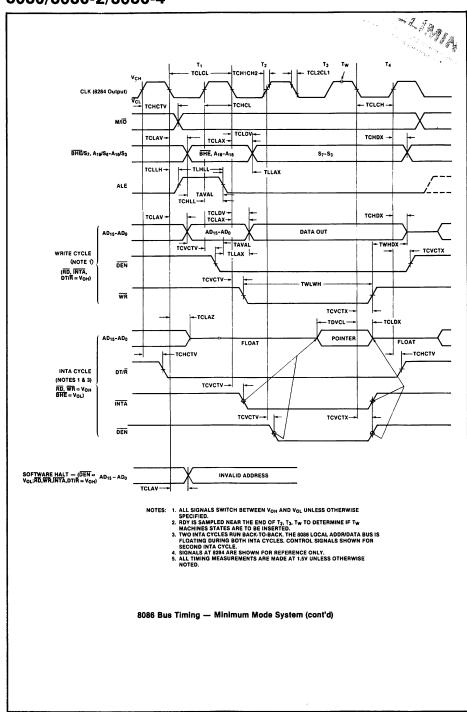

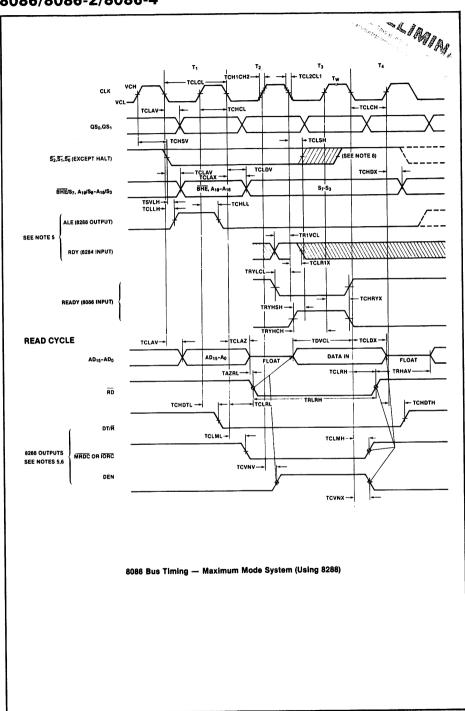

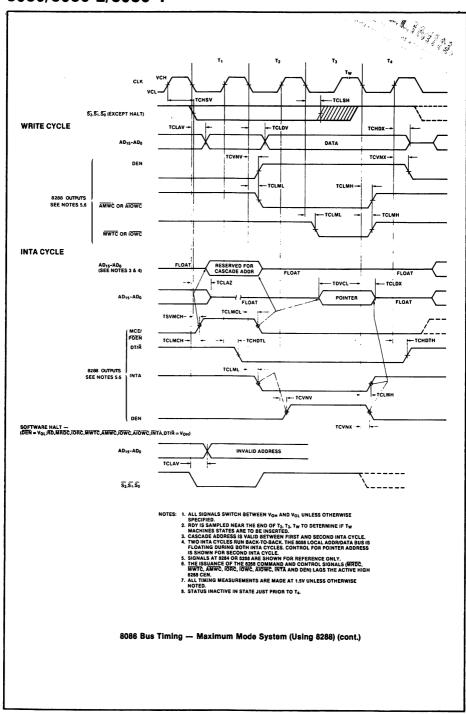

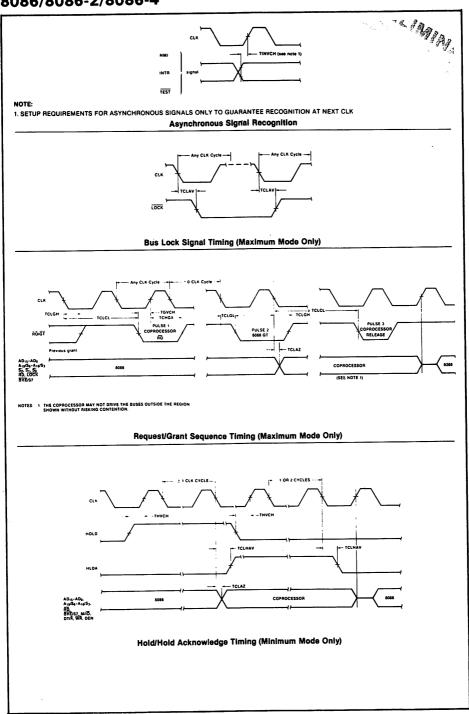

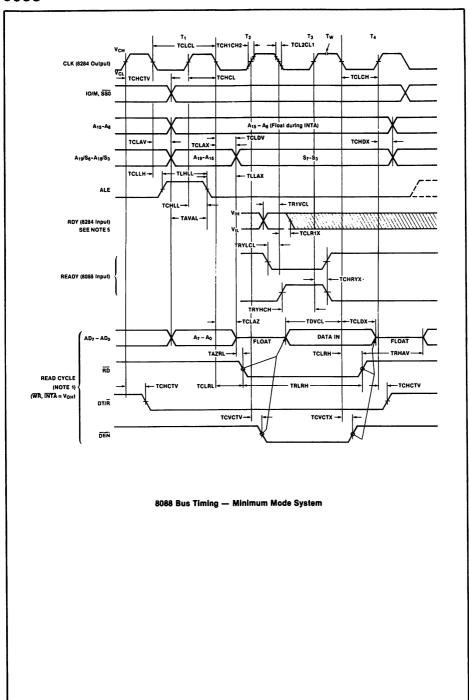

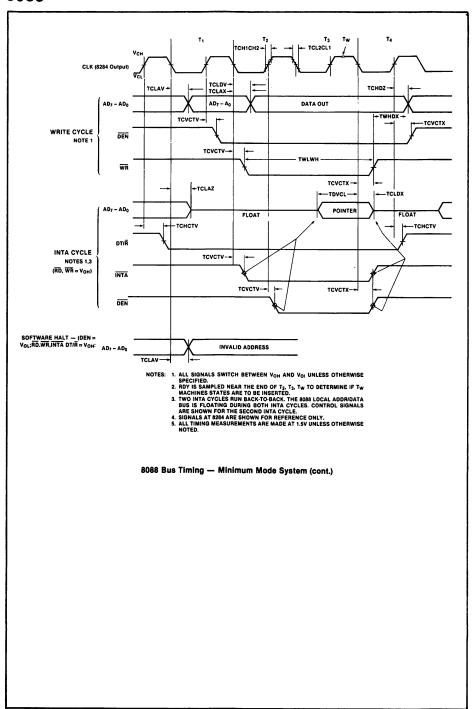

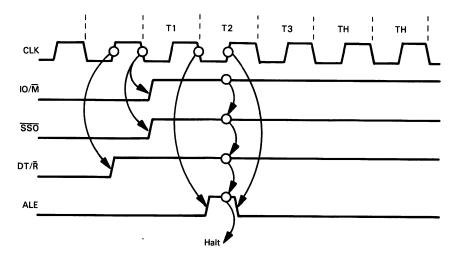

Interpreting the 8086 Bus Timing Diagrams 8-43

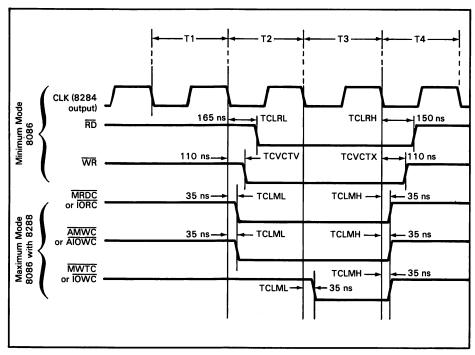

Minimum Mode Bus Timing 8-44

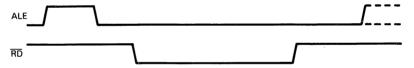

Address and ALE 8-44

Read Cycle Timing 8-45

Write Cycle Timing 8-46

Interrupt Acknowledge Timing 8-47

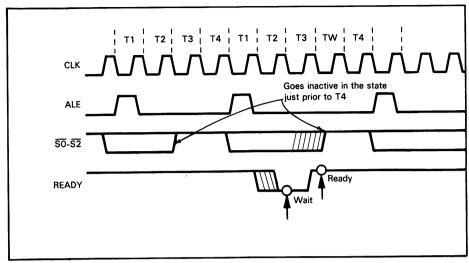

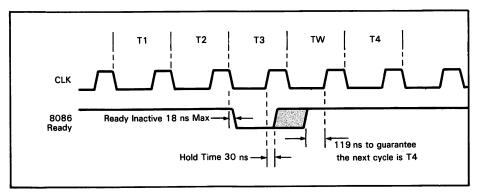

Ready Timing 8-48

Bus Control Transfer Timing 8-48

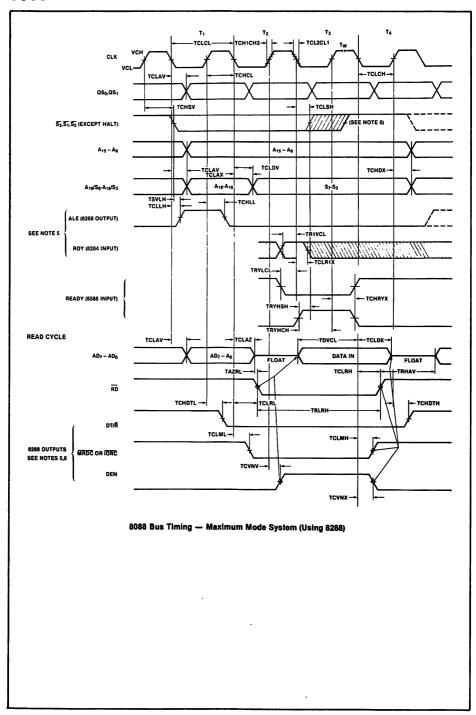

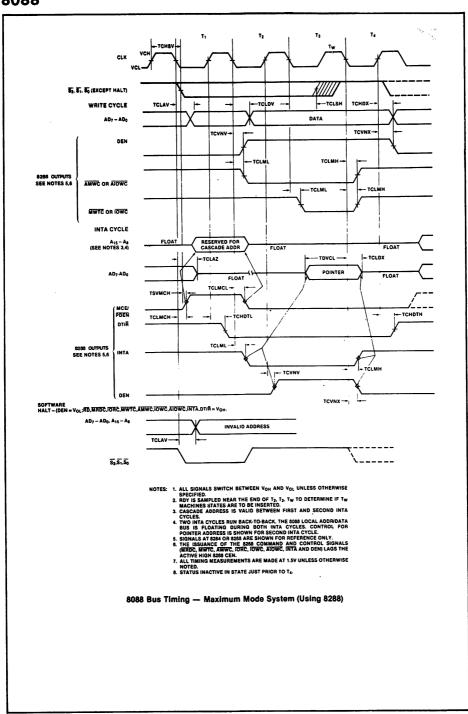

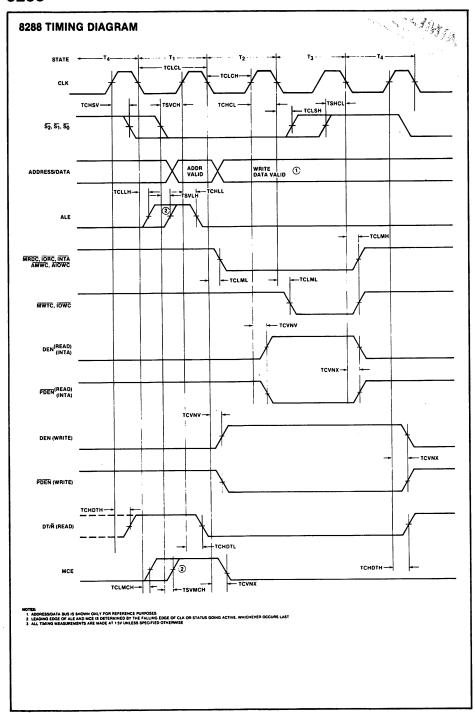

Maximum Mode Bus Timing 8-49

Address and ALE 8-49

Read Cycle Timing 8-50

Write Cycle Timing 8-51

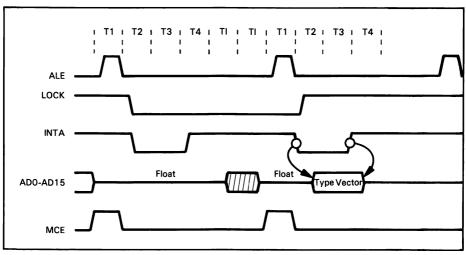

Interrupt Acknowledge Timing 8-51

Ready Timing 8-52

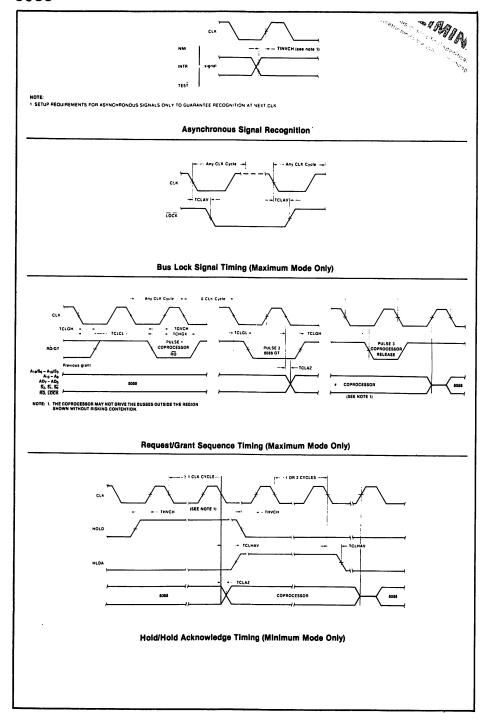

Other Considerations 8-53

Bus Control Transfer (HOLD/HLDA and RQ/GT) 8-53

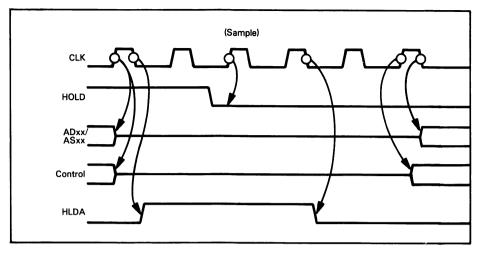

Minimum Mode 8-53

Maximum Mode 8-61

#### 9. The Multibus

Initialization Signal Line 9-3

Address and Inhibit Lines 9-3

Data Lines 9-4

Bus Contention Resolution Lines 9-4

Information Transfer Protocol Lines 9-5

Asynchronous Interrupt Lines 9-6

Power Supply Lines 9-7

Reserved Lines 9-7

Multibus Architectural Concepts 9-11

#### 10. Multiprocessor Configurations for the 8086

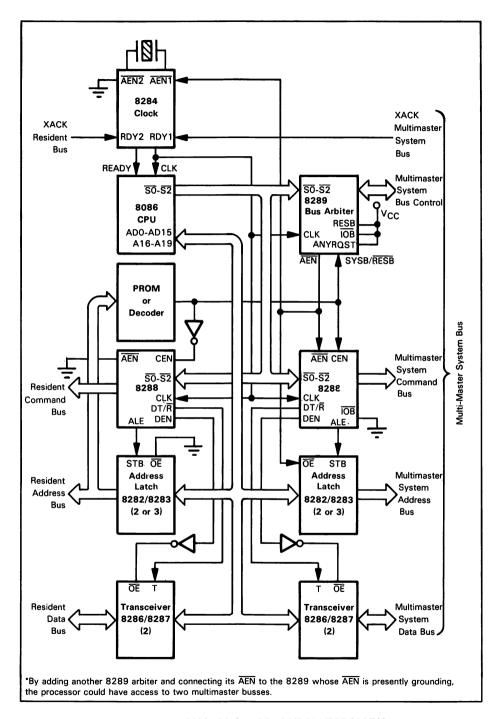

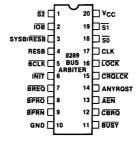

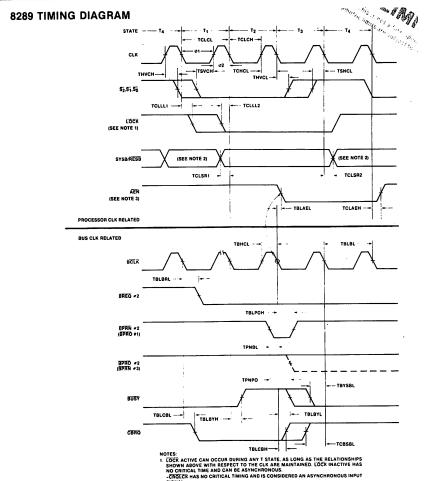

Co-processor 10-2 Multiprocessing on a Shared System Bus 10-4 Bus Access and Release Options for the 8289 10-11

#### **Appendices**

- A. 8086 Instruction Set Ordered Alphabetically

- B. 8086 Instruction Set Object Codes in Ascending Numeric Sequence

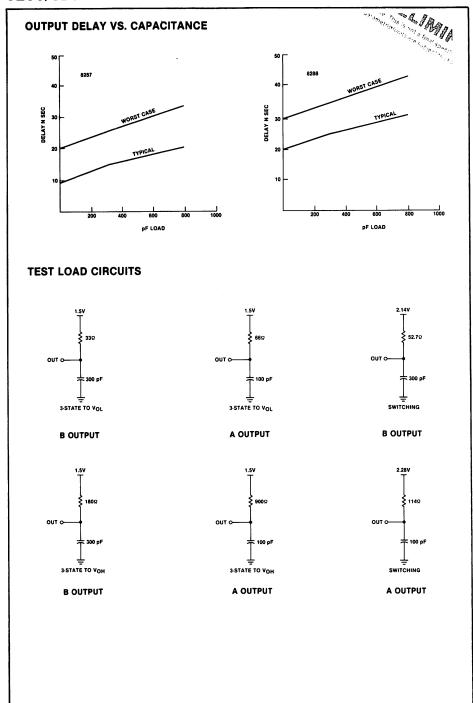

- C. 8086 and 8088 Family AC and DC Characteristics and Signal Waveforms

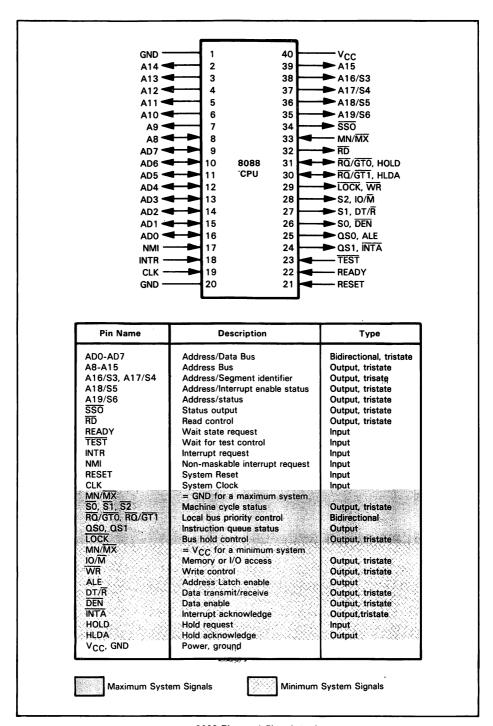

- D. The 8088 CPU

8088 Programmable Registers and Addressing Modes D-1 8088 CPU Pins and Signals D-1 8088 Timing and Instruction Execution D-3 8088 Memory and I/O Device Access Bus Cycles D-3 The 8088 Halt State D-4 Other 8086-Compatible 8088 Logic D-4 The 8088 Instruction Set D-5

#### Index

# **Figures**

| 4-1        | 8-Bit Buffer-to-Buffer Move 4-6                                                  |

|------------|----------------------------------------------------------------------------------|

| 4-2        | 16-Bit Buffer-to-Buffer Move 4-6                                                 |

| 4-3        | Buffer Move Register Initialization 4-7                                          |

| 4-4        | Alternate Buffer Move Register Initialization 4-8                                |

| 4-5        | Buffer Move Register Initialization using Immediate Data 4-8                     |

| 4-6        | Buffer Move Register Initialization via Stack and Pop Instructions 4-10          |

| 4-4        | Buffer Move Register Initialization via Stack and Indirect Addressing 4-10       |

| 4-8        | Buffer Move Register Initialization using LEA Instruction 4-10                   |

| 4-9        | Buffer Intialization (8-Bit Data Elements) 4-12                                  |

| 4-10       | Buffer Intialization (16-Bit Data Elements) 4-12                                 |

| 4-11       | Buffer Translation 4-13                                                          |

| 4-12       | Translation of 16-Bit Data Elements 4-13                                         |

| 4-13       | Buffer-to-Buffer Translation 4-14                                                |

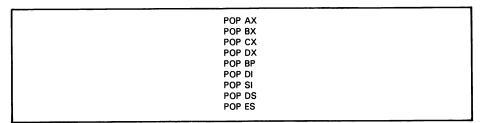

| 4-14       | Saving the 8086 Registers 4-15                                                   |

| 4-15       | Restoring the 8086 Registers 4-15                                                |

| 4-16       | Initializing the ES Register via Immediate Data 4-16                             |

| 4-17       | Initializing the ES Register via Code Segment Locations 4-16                     |

| 4-18       | Multiword Addition 4-17                                                          |

| 4-19       | Multibyte BCD Addition 4-20                                                      |

| 4-20       | Multibyte ASCII Addition 4-20                                                    |

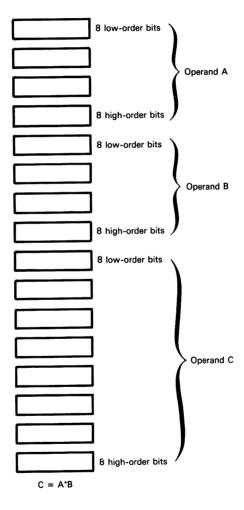

| 4-21       | 32-Bit by 32-Bit Multiplication 4-25                                             |

| 4-22       | ASCII Multiplication 4-27                                                        |

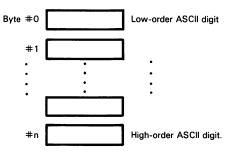

| 4-23       | ASCII Division 4-31                                                              |

| 4-24       | Calculate the Length of a String 4-33                                            |

| 4-25       | Find the Largest 8-Bit Number 4-33                                               |

| 4-26       | Find the Largest 16-Bit Number 4-34                                              |

| 4-27       | Buffer Translation with Range Checking 4-34                                      |

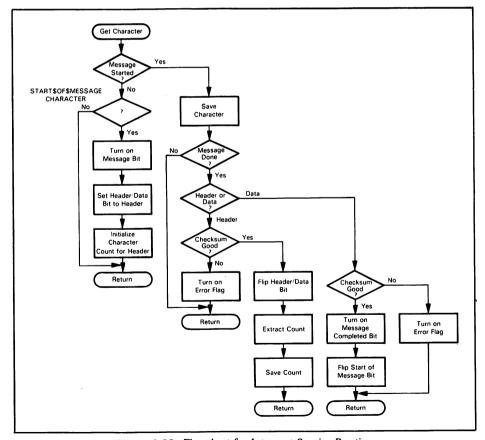

| 4-28       | Flowchart for Interrupt Service Routine 4-38                                     |

| 4-29       | Interrupt Service Routine 4-41                                                   |

| 4-30       | 8-Bit Buffer-to-Buffer Compare 4-47                                              |

| 4-31       | Alternate 8-Bit Buffer-to-Buffer Compare 4-48                                    |

| 4-32       | Block I/O via I/O Port Addressing 4-57                                           |

| 4-33       | Block I/O via Memory Mapped Addressing 4-57                                      |

| 4-34       | Routine to Convert Two ASCII Digits to their Hex Equivalents 4-63                |

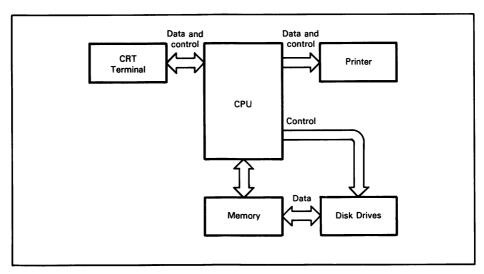

| 5-1        | Hypothetical Development System 5-2                                              |

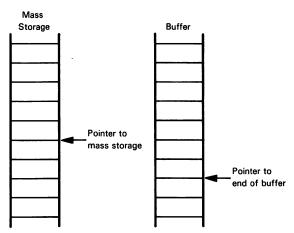

| 5-2        | Elementary Editor Operation 5-3                                                  |

|            |                                                                                  |

| 7-1        | 8086 Pins and Signal Assignments 7-2                                             |

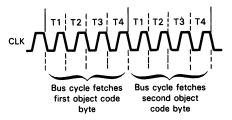

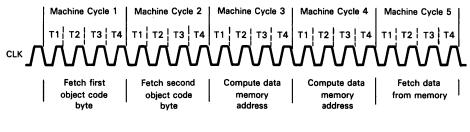

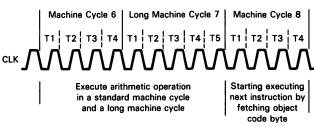

| 7-2        | Basic 8086 Bus Cycles 7-9                                                        |

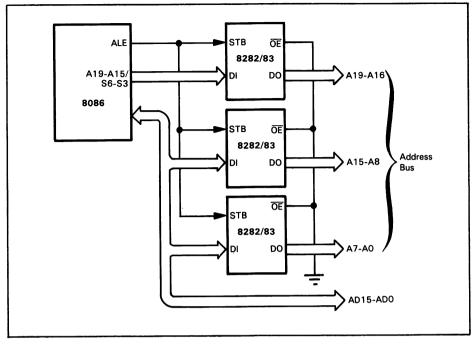

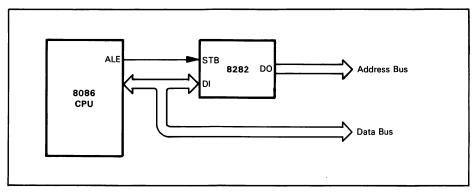

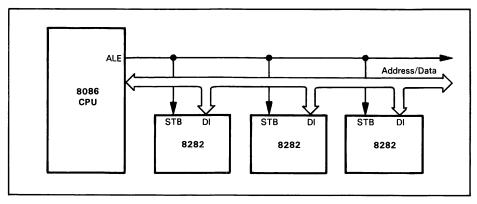

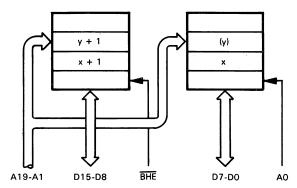

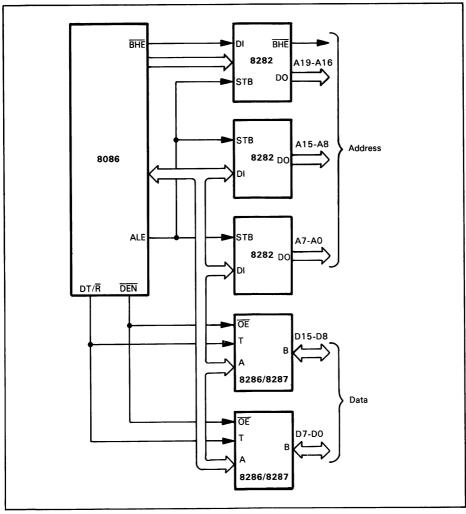

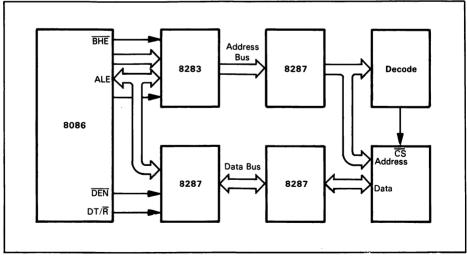

| 7-3        | Demultiplexing the Address/Data Bus 7-11                                         |

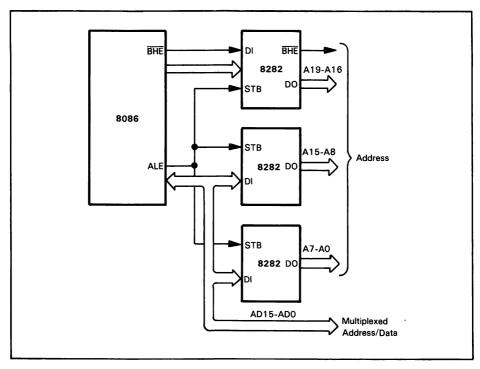

| 7-4        | Separate Address and Data Busses 7-12                                            |

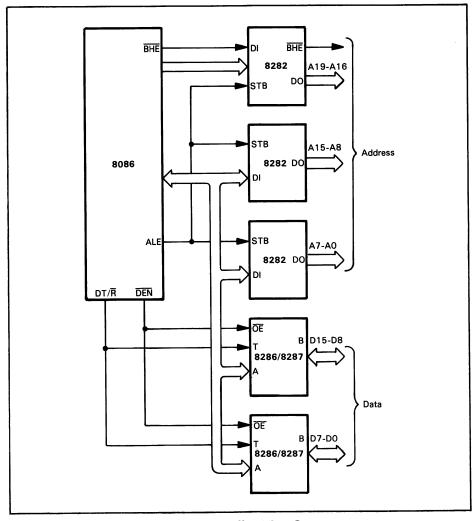

| 7-5        | Multiplexed Bus with Local Address Demultiplexing 7-12                           |

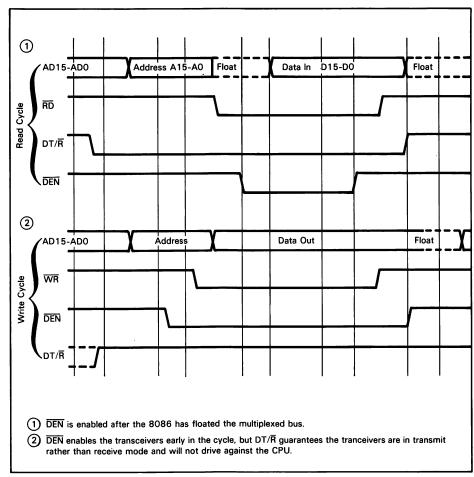

| 7-6        | Multiplexed Data Bus 7-16                                                        |

| 7-7        | Buffered Data Bus 7-17                                                           |

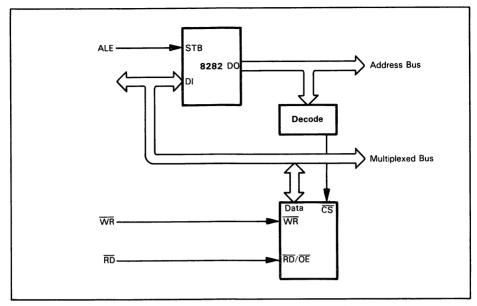

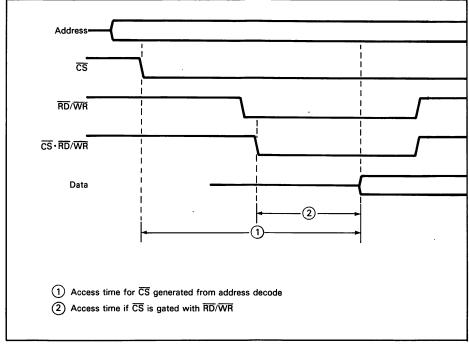

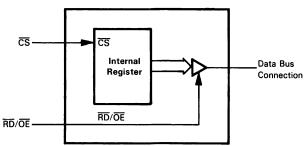

| 7-8<br>7-9 | Devices with Output Enables on the Multiplexed Bus 7-18 CS Gated with RD/WR 7-19 |

# Figures (Continued)

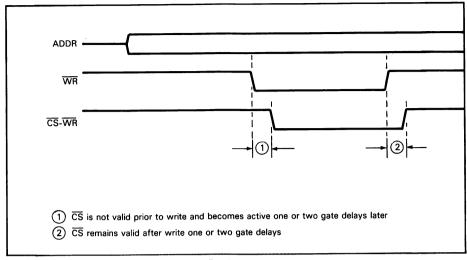

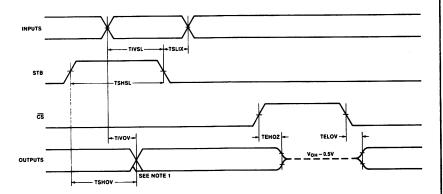

| 7-10         | CS to WR Set-up and Hold 7-20                                                                                                                             |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

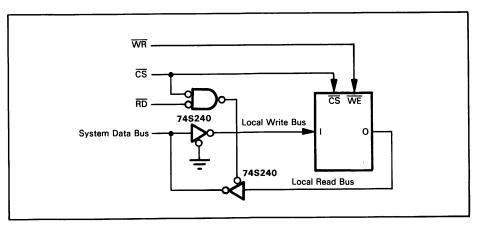

| 7-10<br>7-11 | Buffered Data Bus 7-21                                                                                                                                    |

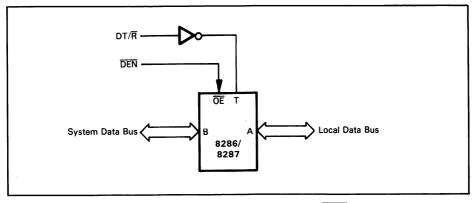

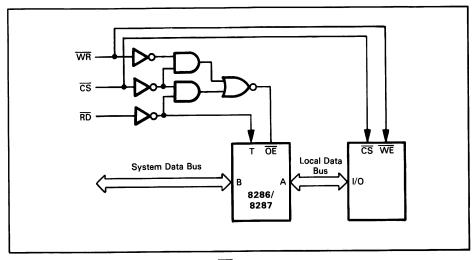

| 7-12         | Bus Transceiver Control 7-22                                                                                                                              |

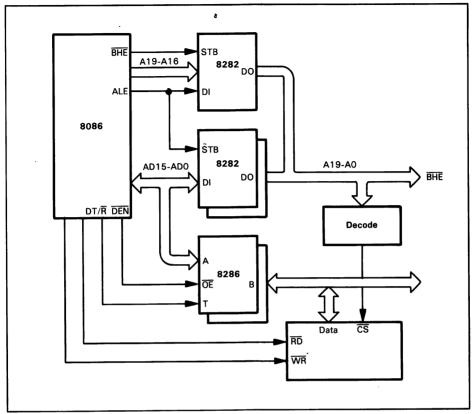

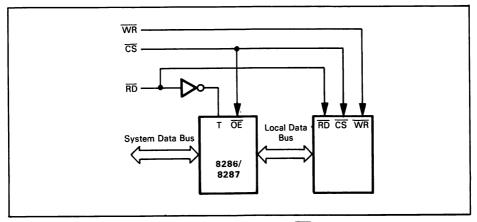

| 7-13         | Devices with Output Enables on the System Bus 7-23                                                                                                        |

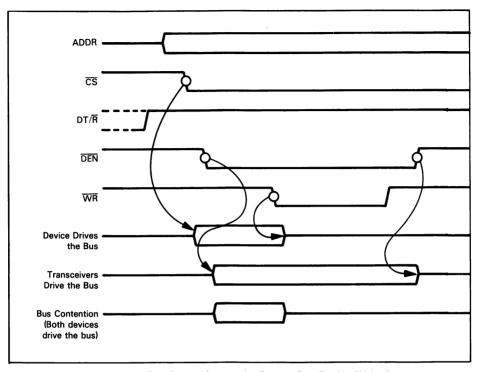

| 7-14         | Bus Contention on the System Bus During Write                                                                                                             |

| , 14         | for Devices without Output Enables 7-24                                                                                                                   |

| 7-15         | Fully Buffered System 7-24                                                                                                                                |

| 7-16         | Controlling System Transceivers with DEN and DT/R 7-25                                                                                                    |

| 7-17         | Devices with $\overline{OE}$ 7-25                                                                                                                         |

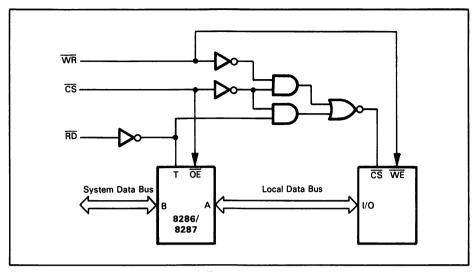

| 7-18         | Devices without $\overline{OE}$ . Common or Separate Input/Output<br>Limited Read Access. Limited $\overline{CS}$ to $\overline{WE}$ Hold and Set-up 7-26 |

| 7-19         | Devices without $\overline{OE}$ . Common or Separate Input/Output<br>Full Read Access. Limited Write Data Set-up and Hold 7-27                            |

| 7-20         | Devices without OE. Separate Input/Output 7-27                                                                                                            |

| 8-1          | Minimum Mode 8086 8-2                                                                                                                                     |

| 8-2          | Maximum Mode 8086 8-4                                                                                                                                     |

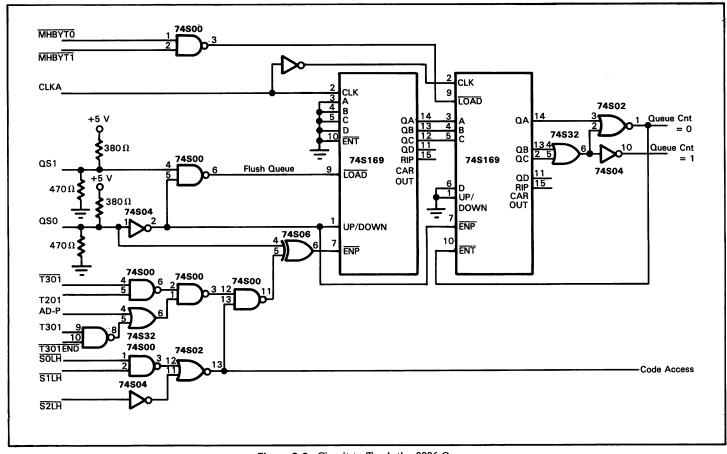

| 8-3          | Circuit to Track the 8086 Queue 8-5                                                                                                                       |

| 8-4          | Status Line Activation and Termination 8-7                                                                                                                |

| 8-5          | Minimum and Maximum Bus Transfer Timing 8-8                                                                                                               |

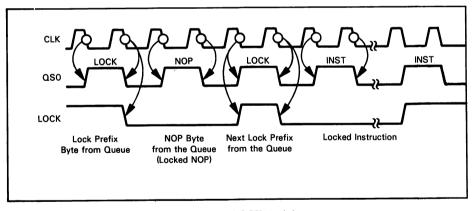

| 8-6          | LOCK Activity 8-9                                                                                                                                         |

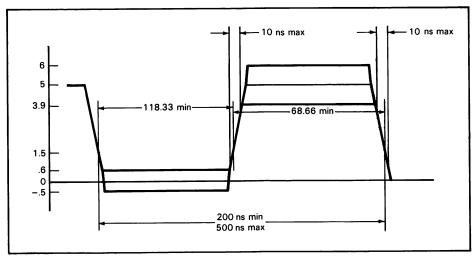

| 8-7          | Timing and Voltage Requirements for the 8086 CPU 8-11                                                                                                     |

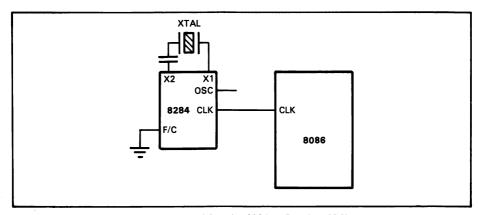

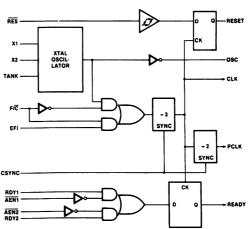

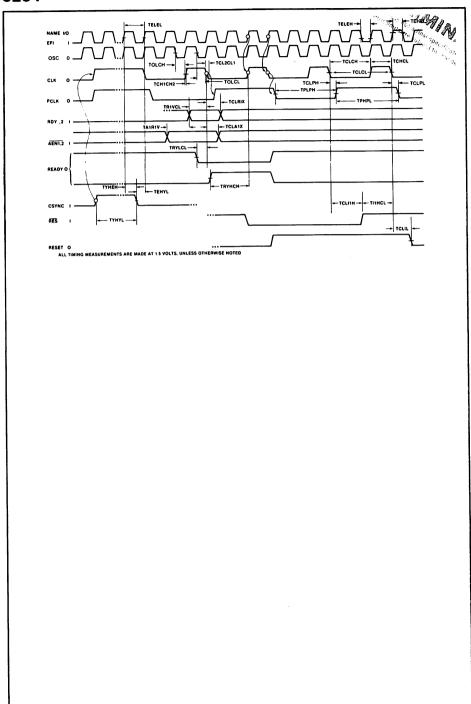

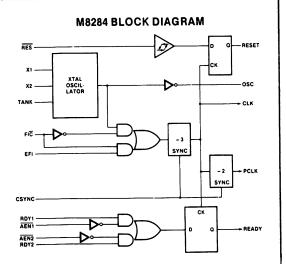

| 8-8          | Using the 8284 to Provide CLK 8-12                                                                                                                        |

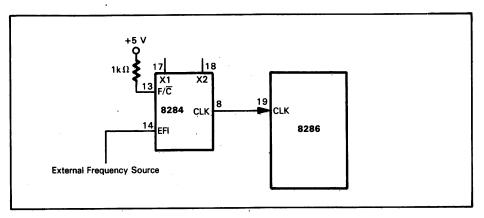

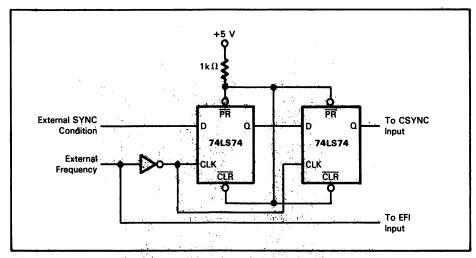

| 8-9          | Using an External Frequency Source 8-13                                                                                                                   |

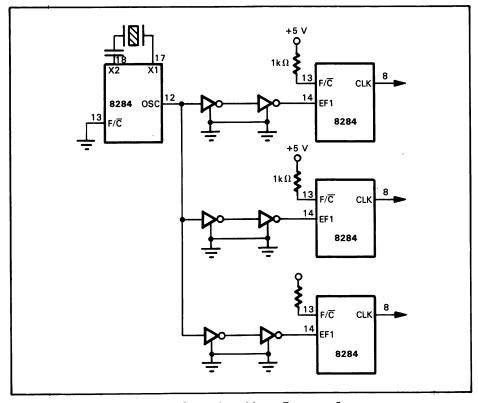

| 8-10         | Generating a Master Frequency Source 8-15                                                                                                                 |

| 8-11         | Synchronizing CSYNC 8-16                                                                                                                                  |

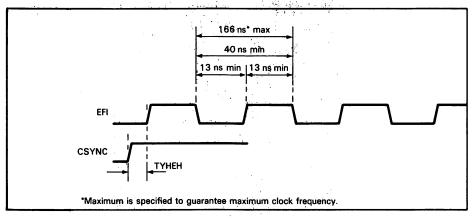

| 8-12         | CSYNC Timing 8-16                                                                                                                                         |

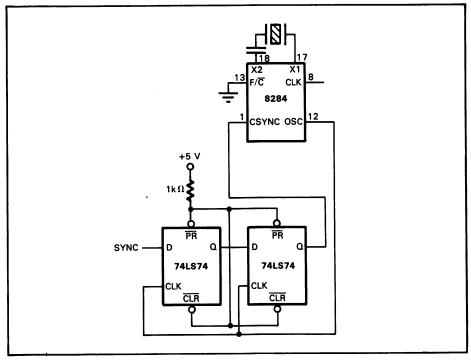

| 8-13         | Synchronizing CSYNC using OSC 8-17                                                                                                                        |

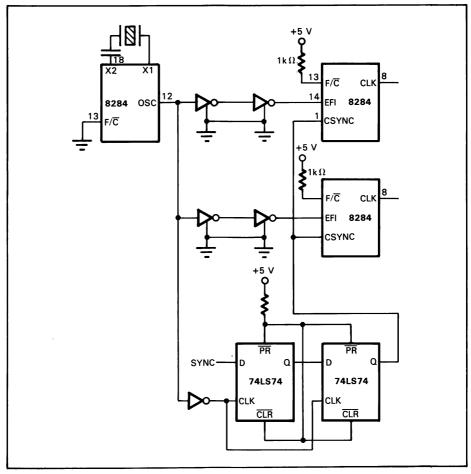

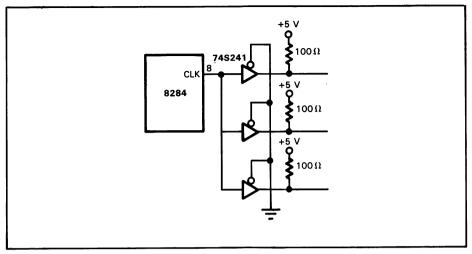

| 8-14         | Delivering CSYNC to Multiple 8284s 8-18  Buffering CLK with a High-Drive Device 8-19                                                                      |

| 8-15         | Duffering CER with a ringh 21110 201100                                                                                                                   |

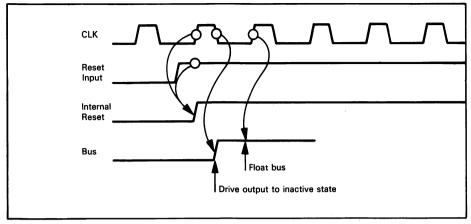

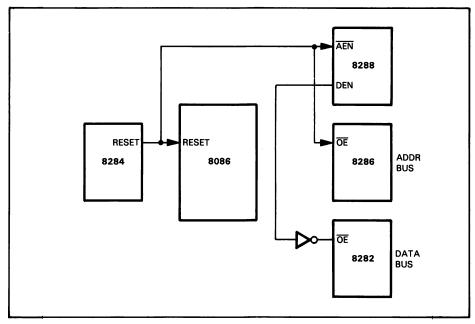

| 8-16         | 8086 Bus Condition on Reset 8-20 Reset Disable for Maximum Mode 8086 Bus Interface 8-21                                                                   |

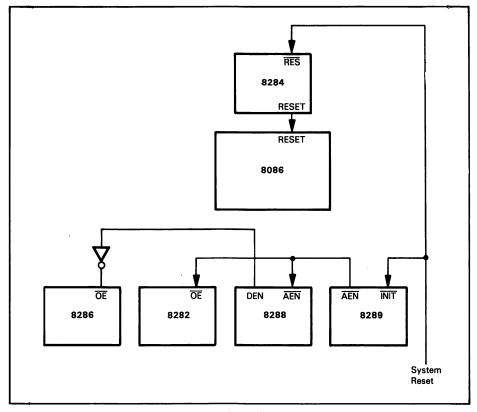

| 8-17         | Reset Disable for Maximum Mode 8086 Bus Interface in                                                                                                      |

| 8-18         | Multi-CPU System 8-22                                                                                                                                     |

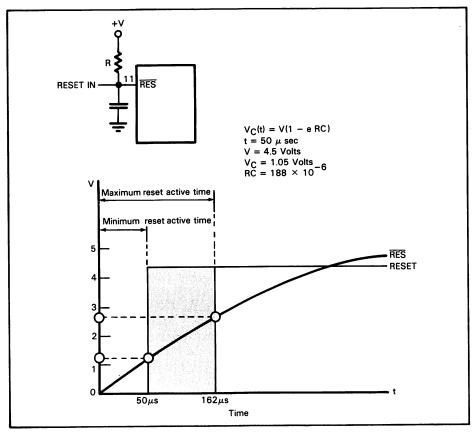

| 8-19         | 8284 Reset Circuit 8-23                                                                                                                                   |

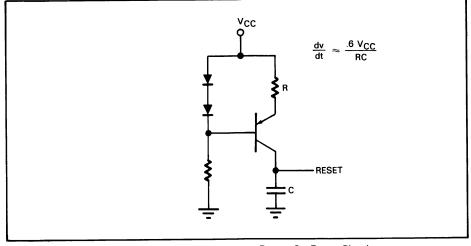

| 8-20         | Constant Current Power-On Reset Circuit 8-23                                                                                                              |

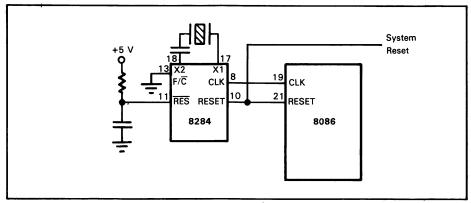

| 8-21         | 8086 Reset 8-24                                                                                                                                           |

| 8-22         | Normally Not Ready System Avoiding a Wait State 8-25                                                                                                      |

| 8-23         | Normally Ready System Inserting a Wait State 8-26                                                                                                         |

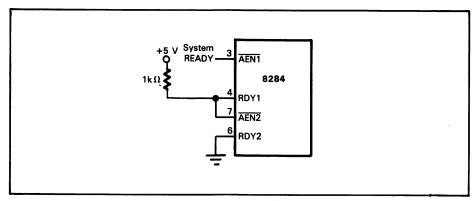

| 8-24         | 8284-8086 Ready Connection 8-26                                                                                                                           |

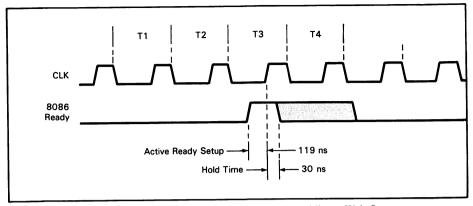

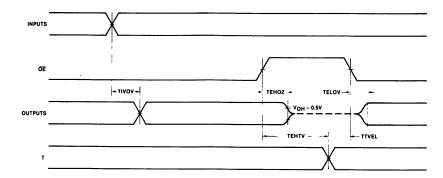

| 8-25         | 8284 with 8086 Ready Timing 8-27                                                                                                                          |

| 8-26         | 8284 using One RDY Input 8-27                                                                                                                             |

| 8-27         | 8284 with SYSTEM READY Driving Access Enable 8-28                                                                                                         |

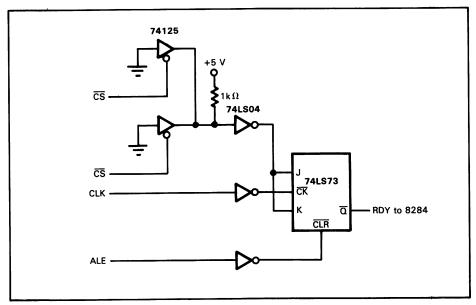

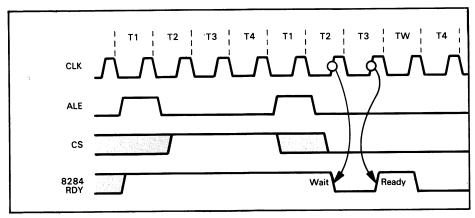

| 8-28         | Single Wait State Generator 8-29 Timing for Single Wait State Generator 8-29                                                                              |

|              |                                                                                                                                                           |

# Figures (Continued)

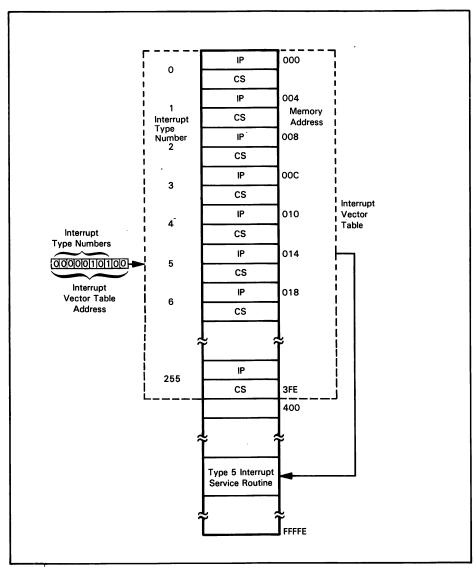

| 8-30  | Obtaining the Interrupt Service Routine from the Interrupt Vector Table 8-31 |

|-------|------------------------------------------------------------------------------|

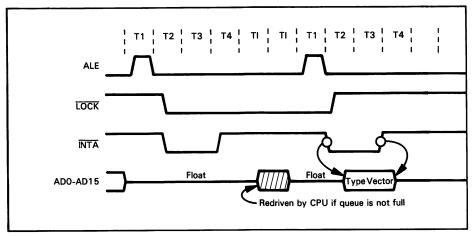

| 8-31  | Interrupt Acknowledge Sequence in Minimum Mode 8-35                          |

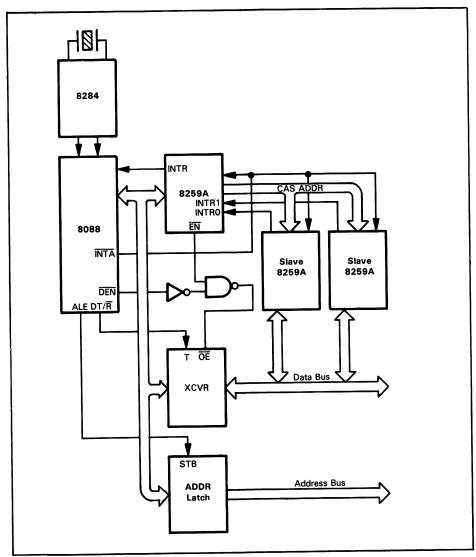

| 8-32a | 8259s Connected to a Minimum Mode 8086 —                                     |

|       | Multiplexed Bus 8-39                                                         |

| 8-32b | 8259s Connected to a Minimum Mode 8086 —                                     |

|       | Demultiplexed Bus 8-40                                                       |

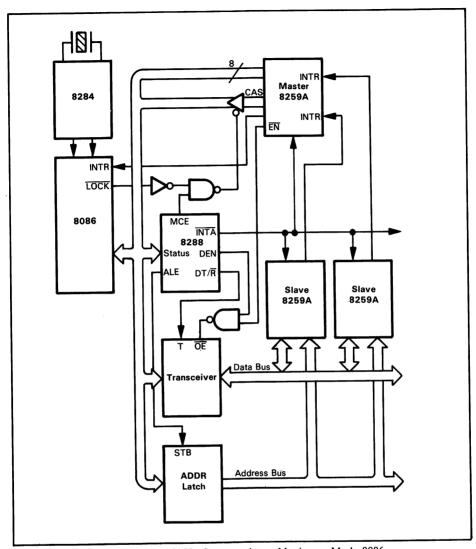

| 8-33  | 8259s Connected to a Maximum Mode 8086 8-41                                  |

| 8-34  | Timing to Gate 8259A CAS Address onto the 8086                               |

|       | Local Bus 8-42                                                               |

| 8-35  | HOLD/HLDA Sequence 8-54                                                      |

| 8-36  | DMA using Minimum Mode 8-58                                                  |

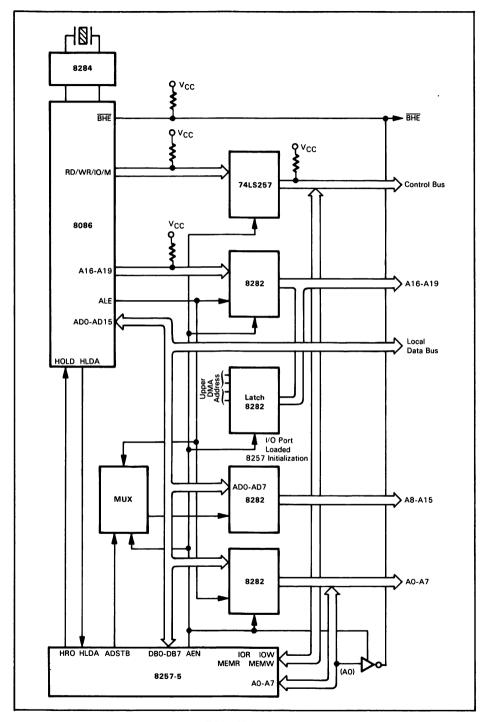

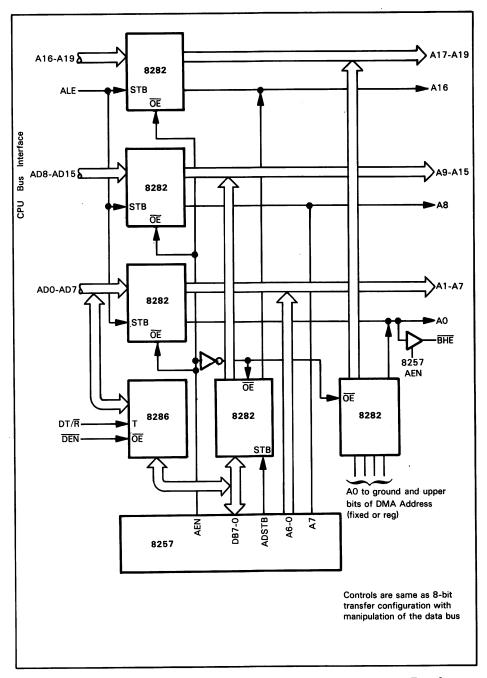

| 8-37  | 8257 on System Bus 8086 Minimum Mode System                                  |

|       | 16-Bit Data Transfers 8-59                                                   |

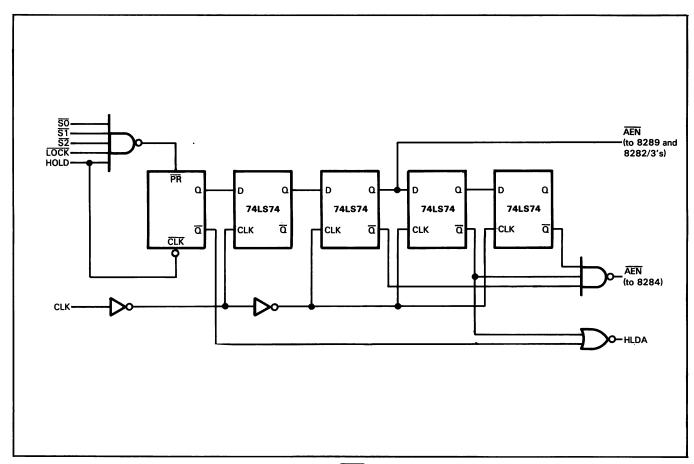

| 8-38  | Translating HOLD into AEN Disable for Maximum Mode 8086 8-60                 |

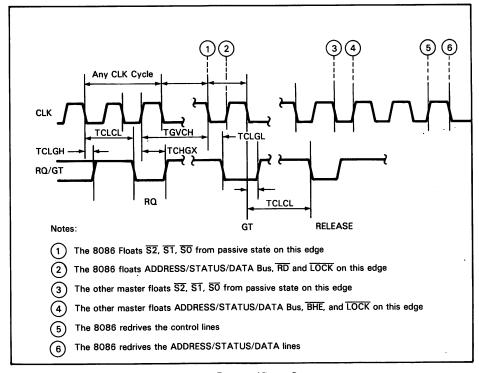

| 8-39  | Request/Grant Sequnce 8-64                                                   |

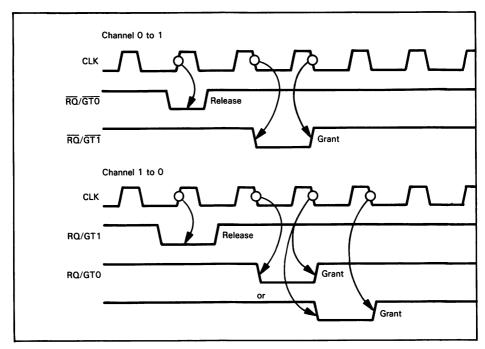

| 8-40  | Channel Transfer Delay 8-66                                                  |

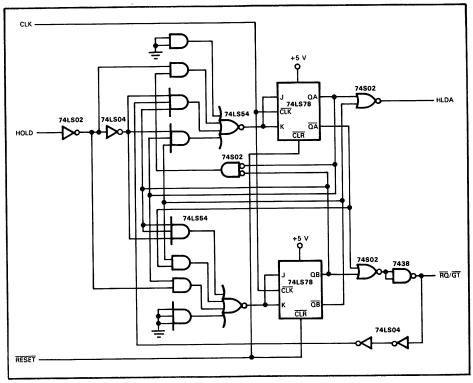

| 8-41  | HOLD/HLDA to RQ/GT Conversion Circuit 8-67                                   |

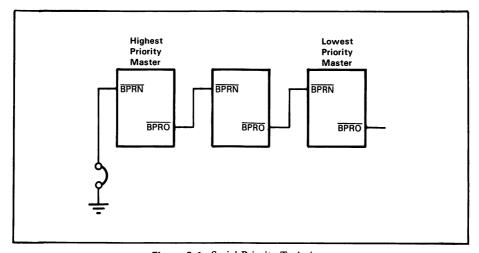

| 9-1   | Serial Priority Technique 9-8                                                |

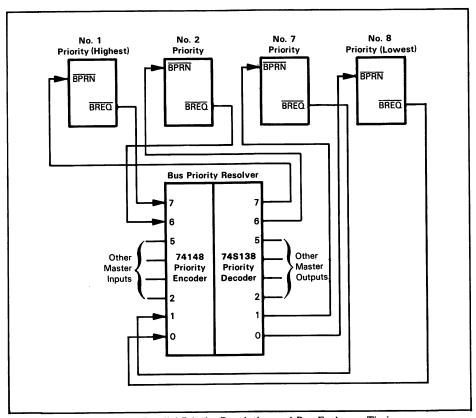

| 9-2   | Parallel Priority Resolution and Bus Exchange Timing 9-9                     |

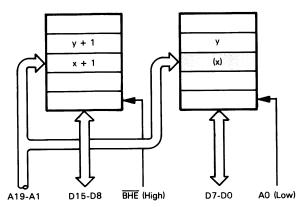

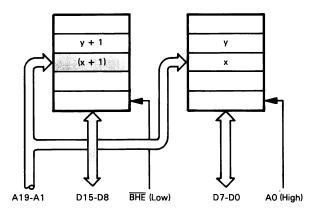

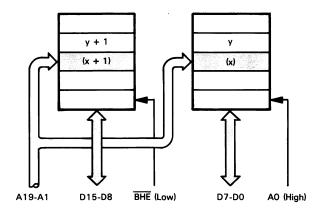

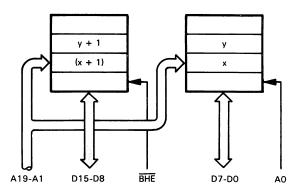

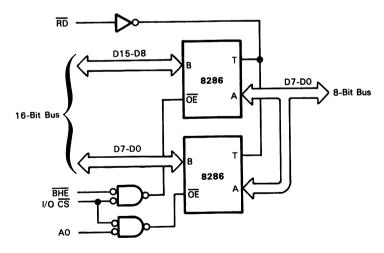

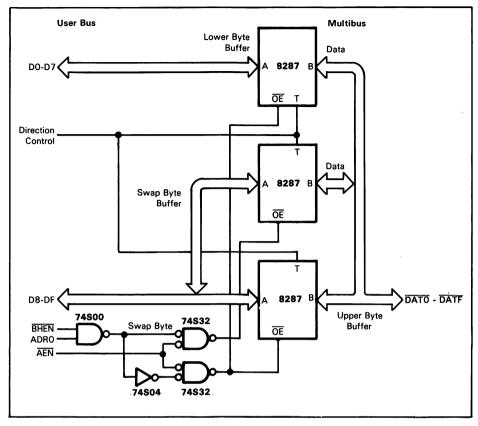

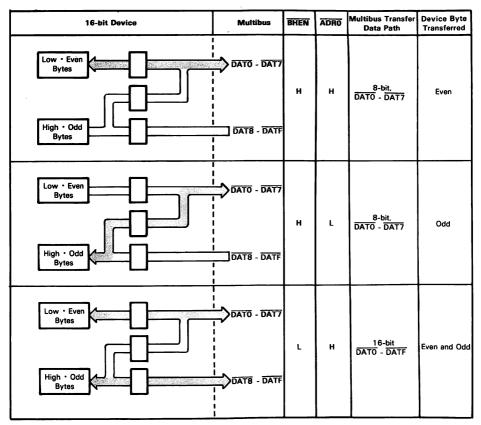

| 9-3   | 8/16-Bit Device Transfer Operations 9-12                                     |

|       | -                                                                            |

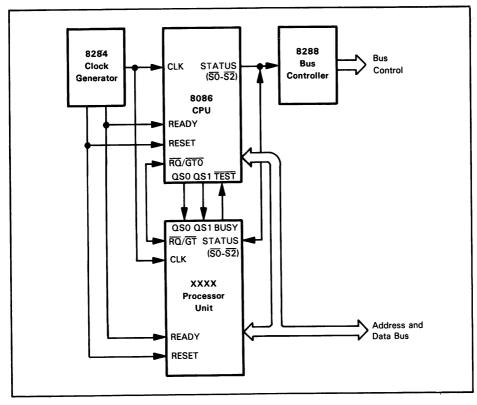

| 10-1  | 8086 Maximum Mode Multiple Processors 10-3                                   |

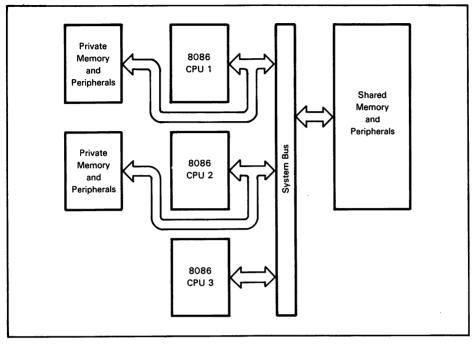

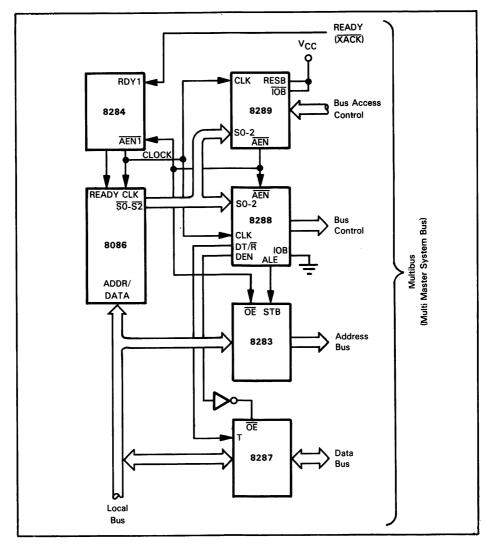

| 10-2  | Multiprocessor Configuration 10-5                                            |

| 10-3  | CPU with no Local Resources 10-6                                             |

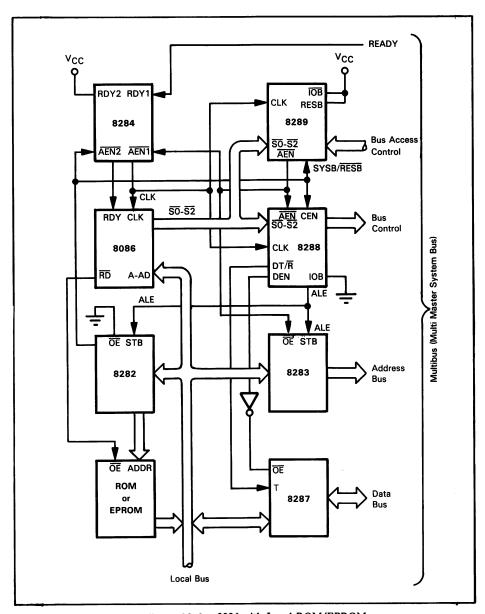

| 10-4a | 8086 with Local ROM/EPROM 10-9                                               |

| 10-4b | 8086 with Local ROM/EPROM and I/O 10-10                                      |

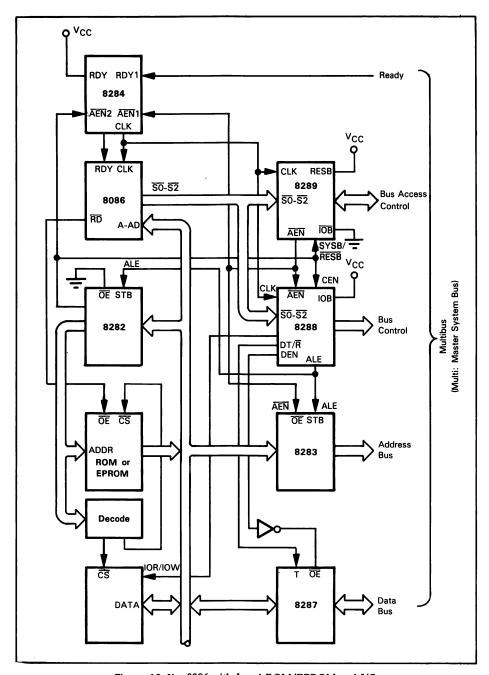

| 10-4c | 8086 with Local RAM/ROM/EPROM/I/O 10-12                                      |

| D-1   | 8088 Pins and Signal Assignments D-2                                         |

# Tables

| <ul> <li>Instructions that Affect All 8086 Arithmetic Flags 3-26</li> <li>Instructions that Affect All 8086 Arithmetic Flags Except Carry 3-</li> <li>Instructions that Affect AF and CF 3-27</li> <li>Instructions that Leave Overflow Undefined 3-27</li> <li>Instructions that Affect All Arithmetic Flags,</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| <ul> <li>3-4 Instructions that Affect AF and CF 3-27</li> <li>3-5 Instructions that Leave Overflow Undefined 3-27</li> <li>3-6 Instructions that Affect All Arithmetic Flags, Leaving CF and OF Meaningful 3-27</li> <li>3-7 Instructions that Affect All Arithmetic Flags, Leaving AF Undefined 3-28</li> <li>3-8 Instructions that Affect Carry and Overflow Flags Only 3-28</li> <li>3-9 Instructions that Affect Specific Flags 3-28</li> <li>3-10 Instructions that Affect Parity, Sign and Zero Flags 3-29</li> <li>3-11 Instructions that Scramble the Flags 3-29</li> <li>3-12 Instructions that Restore All the 8086 Flags from the Stack 3-29</li> <li>3-13 Instructions that Clear the Interrupt and Trap Flags 3-29</li> <li>4-1 8086 Data Movement Instructions 4-3</li> <li>4-2 8086 Addition Instructions 4-18</li> <li>4-3 8086 Subtraction Instructions 4-26</li> <li>4-5 8086 Multiplication Instructions 4-26</li> <li>4-6 8086 Comparison Instructions 4-36</li> <li>4-8 String Primitive Instructions 4-36</li> <li>4-8 String Primitive Instructions 4-45</li> <li>4-9 Program Counter Control Instructions 4-50</li> <li>4-10 Jump-on-Condition 4-54</li> <li>4-11 Signed vs. Unsigned Comparison Instructions 4-55</li> <li>4-12 Loop Instructions 4-56</li> <li>4-13 Processor Control Instructions 4-58</li> <li>4-14 8086 I/O Instructions 4-59</li> <li>4-15 8086 Interrupt Instructions 4-59</li> <li>4-16 8086 Interrupt Instructions 4-51</li> </ul> |     |

| <ul> <li>3-5 Instructions that Leave Overflow Undefined 3-27</li> <li>3-6 Instructions that Affect All Arithmetic Flags, Leaving CF and OF Meaningful 3-27</li> <li>3-7 Instructions that Affect All Arithmetic Flags, Leaving AF Undefined 3-28</li> <li>3-8 Instructions that Affect Carry and Overflow Flags Only 3-28</li> <li>3-9 Instructions that Affect Specific Flags 3-28</li> <li>3-10 Instructions that Affect Parity, Sign and Zero Flags 3-29</li> <li>3-11 Instructions that Scramble the Flags 3-29</li> <li>3-12 Instructions that Restore All the 8086 Flags from the Stack 3-29</li> <li>3-13 Instructions that Clear the Interrupt and Trap Flags 3-29</li> <li>4-1 8086 Data Movement Instructions 4-3</li> <li>4-2 8086 Addition Instructions 4-18</li> <li>4-3 8086 Subtraction Instructions 4-26</li> <li>4-5 8086 Multiplication Instructions 4-26</li> <li>4-5 8086 Division Instructions 4-36</li> <li>4-8 String Primitive Instructions 4-36</li> <li>4-8 String Primitive Instructions 4-45</li> <li>4-9 Program Counter Control Instructions 4-50</li> <li>4-10 Jump-on-Condition 4-54</li> <li>4-11 Signed vs. Unsigned Comparison Instructions 4-55</li> <li>4-12 Loop Instructions 4-56</li> <li>4-13 Processor Control Instructions 4-58</li> <li>4-14 8086 I/O Instructions 4-59</li> <li>4-15 8086 Interrupt Instructions 4-59</li> <li>4-16 8086 Interrupt Instructions 4-59</li> </ul>                                                        | 26  |

| 3-6 Instructions that Affect All Arithmetic Flags, Leaving CF and OF Meaningful 3-27  3-7 Instructions that Affect All Arithmetic Flags, Leaving AF Undefined 3-28  3-8 Instructions that Affect Carry and Overflow Flags Only 3-28  3-9 Instructions that Affect Specific Flags 3-28  3-10 Instructions that Affect Parity, Sign and Zero Flags 3-29  3-11 Instructions that Scramble the Flags 3-29  3-12 Instructions that Restore All the 8086 Flags from the Stack 3-29  3-13 Instructions that Clear the Interrupt and Trap Flags 3-29  4-1 8086 Data Movement Instructions 4-3  4-2 8086 Addition Instructions 4-18  4-3 8086 Subtraction Instructions 4-22  4-4 8086 Multiplication Instructions 4-26  4-5 8086 Division Instructions 4-29  4-6 8086 Comparison Instructions 4-36  4-7 8086 Logical Instructions 4-36  4-8 String Primitive Instructions 4-45  4-9 Program Counter Control Instructions 4-50  4-10 Jump-on-Condition 4-54  4-11 Signed vs. Unsigned Comparison Instructions 4-55  4-12 Loop Instructions 4-56  4-13 Processor Control Instructions 4-58  4-14 8086 I/O Instructions 4-59  4-15 8086 Interrupt Instructions 4-61                                                                                                                                                                                                                                                                                                                             |     |

| Leaving CF and OF Meaningful 3-27  Instructions that Affect All Arithmetic Flags, Leaving AF Undefined 3-28  Instructions that Affect Carry and Overflow Flags Only 3-28  Instructions that Affect Specific Flags 3-28  Instructions that Affect Parity, Sign and Zero Flags 3-29  Instructions that Scramble the Flags 3-29  Instructions that Restore All the 8086 Flags from the Stack 3-29  Instructions that Clear the Interrupt and Trap Flags 3-29  Instructions that Clear the Interrupt and Trap Flags 3-29  4-1 8086 Data Movement Instructions 4-3  8086 Subtraction Instructions 4-18  4-2 8086 Addition Instructions 4-18  4-3 8086 Subtraction Instructions 4-22  4-4 8086 Multiplication Instructions 4-26  4-5 8086 Division Instructions 4-29  4-6 8086 Comparison Instructions 4-36  4-7 8086 Logical Instructions 4-36  4-8 String Primitive Instructions 4-45  4-9 Program Counter Control Instructions 4-50  4-10 Jump-on-Condition 4-54  4-11 Signed vs. Unsigned Comparison Instructions 4-55  4-12 Loop Instructions 4-56  4-13 Processor Control Instructions 4-58  4-14 8086 I/O Instructions 4-59  4-15 8086 Interrupt Instructions 4-61                                                                                                                                                                                                                                                                                                                 |     |

| 3-7 Instructions that Affect All Arithmetic Flags, Leaving AF Undefined 3-28  3-8 Instructions that Affect Carry and Overflow Flags Only 3-28  3-9 Instructions that Affect Specific Flags 3-28  3-10 Instructions that Affect Parity, Sign and Zero Flags 3-29  3-11 Instructions that Scramble the Flags 3-29  3-12 Instructions that Restore All the 8086 Flags from the Stack 3-29  3-13 Instructions that Clear the Interrupt and Trap Flags 3-29  4-1 8086 Data Movement Instructions 4-3  4-2 8086 Addition Instructions 4-18  4-3 8086 Subtraction Instructions 4-22  4-4 8086 Multiplication Instructions 4-26  4-5 8086 Division Instructions 4-29  4-6 8086 Comparison Instructions 4-32  4-7 8086 Logical Instructions 4-36  4-8 String Primitive Instructions 4-45  4-9 Program Counter Control Instructions 4-50  4-10 Jump-on-Condition 4-54  4-11 Signed vs. Unsigned Comparison Instructions 4-55  4-12 Loop Instructions 4-56  4-13 Processor Control Instructions 4-58  4-14 8086 I/O Instructions 4-59  4-15 8086 Interrupt Instructions 4-61                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| Leaving AF Undefined 3-28  Instructions that Affect Carry and Overflow Flags Only 3-28  Instructions that Affect Specific Flags 3-28  Instructions that Affect Parity, Sign and Zero Flags 3-29  Instructions that Scramble the Flags 3-29  Instructions that Restore All the 8086 Flags from the Stack 3-29  Instructions that Clear the Interrupt and Trap Flags 3-29  Instructions that Clear the Interrupt and Trap Flags 3-29  Instructions that Clear the Interrupt and Trap Flags 3-29  Instructions 4-18  4-2 8086 Addition Instructions 4-18  4-3 8086 Subtraction Instructions 4-22  4-4 8086 Multiplication Instructions 4-26  4-5 8086 Division Instructions 4-29  4-6 8086 Comparison Instructions 4-32  4-7 8086 Logical Instructions 4-36  4-8 String Primitive Instructions 4-45  4-9 Program Counter Control Instructions 4-50  4-10 Jump-on-Condition 4-54  4-11 Signed vs. Unsigned Comparison Instructions 4-55  4-12 Loop Instructions 4-56  4-13 Processor Control Instructions 4-58  4-14 8086 I/O Instructions 4-59  4-15 8086 Interrupt Instructions 4-61                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| <ul> <li>Instructions that Affect Carry and Overflow Flags Only 3-28</li> <li>Instructions that Affect Specific Flags 3-28</li> <li>Instructions that Affect Parity, Sign and Zero Flags 3-29</li> <li>Instructions that Scramble the Flags 3-29</li> <li>Instructions that Restore All the 8086 Flags from the Stack 3-29</li> <li>Instructions that Clear the Interrupt and Trap Flags 3-29</li> <li>8086 Data Movement Instructions 4-3</li> <li>8086 Subtraction Instructions 4-18</li> <li>8086 Subtraction Instructions 4-22</li> <li>8086 Multiplication Instructions 4-26</li> <li>8086 Division Instructions 4-29</li> <li>8086 Comparison Instructions 4-32</li> <li>8086 Logical Instructions 4-36</li> <li>String Primitive Instructions 4-45</li> <li>Program Counter Control Instructions 4-50</li> <li>Jump-on-Condition 4-54</li> <li>Signed vs. Unsigned Comparison Instructions 4-55</li> <li>Loop Instructions 4-56</li> <li>Processor Control Instructions 4-58</li> <li>8086 I/O Instructions 4-59</li> <li>8086 Interrupt Instructions 4-61</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| <ul> <li>3-9 Instructions that Affect Specific Flags 3-28</li> <li>3-10 Instructions that Affect Parity, Sign and Zero Flags 3-29</li> <li>3-11 Instructions that Scramble the Flags 3-29</li> <li>3-12 Instructions that Restore All the 8086 Flags from the Stack 3-29</li> <li>3-13 Instructions that Clear the Interrupt and Trap Flags 3-29</li> <li>4-1 8086 Data Movement Instructions 4-3</li> <li>4-2 8086 Addition Instructions 4-18</li> <li>4-3 8086 Subtraction Instructions 4-22</li> <li>4-4 8086 Multiplication Instructions 4-26</li> <li>4-5 8086 Division Instructions 4-29</li> <li>4-6 8086 Comparison Instructions 4-32</li> <li>4-7 8086 Logical Instructions 4-36</li> <li>4-8 String Primitive Instructions 4-45</li> <li>4-9 Program Counter Control Instructions 4-50</li> <li>4-10 Jump-on-Condition 4-54</li> <li>4-11 Signed vs. Unsigned Comparison Instructions 4-55</li> <li>4-12 Loop Instructions 4-56</li> <li>4-13 Processor Control Instructions 4-58</li> <li>4-14 8086 I/O Instructions 4-59</li> <li>4-15 8086 Interrupt Instructions 4-61</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                      |     |

| <ul> <li>3-10 Instructions that Affect Parity, Sign and Zero Flags 3-29</li> <li>3-11 Instructions that Scramble the Flags 3-29</li> <li>3-12 Instructions that Restore All the 8086 Flags from the Stack 3-29</li> <li>3-13 Instructions that Clear the Interrupt and Trap Flags 3-29</li> <li>4-1 8086 Data Movement Instructions 4-3</li> <li>4-2 8086 Addition Instructions 4-18</li> <li>4-3 8086 Subtraction Instructions 4-22</li> <li>4-4 8086 Multiplication Instructions 4-26</li> <li>4-5 8086 Division Instructions 4-29</li> <li>4-6 8086 Comparison Instructions 4-36</li> <li>4-7 8086 Logical Instructions 4-36</li> <li>4-8 String Primitive Instructions 4-45</li> <li>4-9 Program Counter Control Instructions 4-50</li> <li>4-10 Jump-on-Condition 4-54</li> <li>4-11 Signed vs. Unsigned Comparison Instructions 4-55</li> <li>4-12 Loop Instructions 4-56</li> <li>4-13 Processor Control Instructions 4-58</li> <li>4-14 8086 I/O Instructions 4-59</li> <li>4-15 8086 Interrupt Instructions 4-61</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| <ul> <li>3-11 Instructions that Scramble the Flags 3-29</li> <li>3-12 Instructions that Restore All the 8086 Flags from the Stack 3-29</li> <li>3-13 Instructions that Clear the Interrupt and Trap Flags 3-29</li> <li>4-1 8086 Data Movement Instructions 4-3</li> <li>4-2 8086 Addition Instructions 4-18</li> <li>4-3 8086 Subtraction Instructions 4-22</li> <li>4-4 8086 Multiplication Instructions 4-26</li> <li>4-5 8086 Division Instructions 4-29</li> <li>4-6 8086 Comparison Instructions 4-32</li> <li>4-7 8086 Logical Instructions 4-36</li> <li>4-8 String Primitive Instructions 4-45</li> <li>4-9 Program Counter Control Instructions 4-50</li> <li>4-10 Jump-on-Condition 4-54</li> <li>4-11 Signed vs. Unsigned Comparison Instructions 4-55</li> <li>4-12 Loop Instructions 4-56</li> <li>4-13 Processor Control Instructions 4-58</li> <li>4-14 8086 I/O Instructions 4-59</li> <li>4-15 8086 Interrupt Instructions 4-61</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 3-12 Instructions that Restore All the 8086 Flags from the Stack 3-29  3-13 Instructions that Clear the Interrupt and Trap Flags 3-29  4-1 8086 Data Movement Instructions 4-3  4-2 8086 Addition Instructions 4-18  4-3 8086 Subtraction Instructions 4-22  4-4 8086 Multiplication Instructions 4-26  4-5 8086 Division Instructions 4-29  4-6 8086 Comparison Instructions 4-32  4-7 8086 Logical Instructions 4-36  4-8 String Primitive Instructions 4-45  4-9 Program Counter Control Instructions 4-50  4-10 Jump-on-Condition 4-54  4-11 Signed vs. Unsigned Comparison Instructions 4-55  4-12 Loop Instructions 4-56  4-13 Processor Control Instructions 4-58  4-14 8086 I/O Instructions 4-59  4-15 8086 Interrupt Instructions 4-61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| the Stack 3-29  3-13 Instructions that Clear the Interrupt and Trap Flags 3-29  4-1 8086 Data Movement Instructions 4-3  4-2 8086 Addition Instructions 4-18  4-3 8086 Subtraction Instructions 4-22  4-4 8086 Multiplication Instructions 4-26  4-5 8086 Division Instructions 4-29  4-6 8086 Comparison Instructions 4-32  4-7 8086 Logical Instructions 4-36  4-8 String Primitive Instructions 4-45  4-9 Program Counter Control Instructions 4-50  4-10 Jump-on-Condition 4-54  4-11 Signed vs. Unsigned Comparison Instructions 4-55  4-12 Loop Instructions 4-56  4-13 Processor Control Instructions 4-58  4-14 8086 I/O Instructions 4-59  4-15 8086 Interrupt Instructions 4-61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| 3-13 Instructions that Clear the Interrupt and Trap Flags 3-29 4-1 8086 Data Movement Instructions 4-3 4-2 8086 Addition Instructions 4-18 4-3 8086 Subtraction Instructions 4-22 4-4 8086 Multiplication Instructions 4-26 4-5 8086 Division Instructions 4-29 4-6 8086 Comparison Instructions 4-32 4-7 8086 Logical Instructions 4-36 4-8 String Primitive Instructions 4-45 4-9 Program Counter Control Instructions 4-50 4-10 Jump-on-Condition 4-54 4-11 Signed vs. Unsigned Comparison Instructions 4-55 4-12 Loop Instructions 4-56 4-13 Processor Control Instructions 4-58 4-14 8086 I/O Instructions 4-59 4-15 8086 Interrupt Instructions 4-61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 4-1 8086 Data Movement Instructions 4-3 4-2 8086 Addition Instructions 4-18 4-3 8086 Subtraction Instructions 4-22 4-4 8086 Multiplication Instructions 4-26 4-5 8086 Division Instructions 4-29 4-6 8086 Comparison Instructions 4-32 4-7 8086 Logical Instructions 4-36 4-8 String Primitive Instructions 4-45 4-9 Program Counter Control Instructions 4-50 4-10 Jump-on-Condition 4-54 4-11 Signed vs. Unsigned Comparison Instructions 4-55 4-12 Loop Instructions 4-56 4-13 Processor Control Instructions 4-58 4-14 8086 I/O Instructions 4-59 4-15 8086 Interrupt Instructions 4-61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| 4-2 8086 Addition Instructions 4-18 4-3 8086 Subtraction Instructions 4-22 4-4 8086 Multiplication Instructions 4-26 4-5 8086 Division Instructions 4-29 4-6 8086 Comparison Instructions 4-32 4-7 8086 Logical Instructions 4-36 4-8 String Primitive Instructions 4-45 4-9 Program Counter Control Instructions 4-50 4-10 Jump-on-Condition 4-54 4-11 Signed vs. Unsigned Comparison Instructions 4-55 4-12 Loop Instructions 4-56 4-13 Processor Control Instructions 4-58 4-14 8086 I/O Instructions 4-59 4-15 8086 Interrupt Instructions 4-61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| 4-2 8086 Addition Instructions 4-18 4-3 8086 Subtraction Instructions 4-22 4-4 8086 Multiplication Instructions 4-26 4-5 8086 Division Instructions 4-29 4-6 8086 Comparison Instructions 4-32 4-7 8086 Logical Instructions 4-36 4-8 String Primitive Instructions 4-45 4-9 Program Counter Control Instructions 4-50 4-10 Jump-on-Condition 4-54 4-11 Signed vs. Unsigned Comparison Instructions 4-55 4-12 Loop Instructions 4-56 4-13 Processor Control Instructions 4-58 4-14 8086 I/O Instructions 4-59 4-15 8086 Interrupt Instructions 4-61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| 4-4 8086 Multiplication Instructions 4-26 4-5 8086 Division Instructions 4-29 4-6 8086 Comparison Instructions 4-32 4-7 8086 Logical Instructions 4-36 4-8 String Primitive Instructions 4-45 4-9 Program Counter Control Instructions 4-50 4-10 Jump-on-Condition 4-54 4-11 Signed vs. Unsigned Comparison Instructions 4-55 4-12 Loop Instructions 4-56 4-13 Processor Control Instructions 4-58 4-14 8086 I/O Instructions 4-59 4-15 8086 Interrupt Instructions 4-61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| 4-5 8086 Division Instructions 4-29 4-6 8086 Comparison Instructions 4-32 4-7 8086 Logical Instructions 4-36 4-8 String Primitive Instructions 4-45 4-9 Program Counter Control Instructions 4-50 4-10 Jump-on-Condition 4-54 4-11 Signed vs. Unsigned Comparison Instructions 4-55 4-12 Loop Instructions 4-56 4-13 Processor Control Instructions 4-58 4-14 8086 I/O Instructions 4-59 4-15 8086 Interrupt Instructions 4-61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 4-6 8086 Comparison Instructions 4-32 4-7 8086 Logical Instructions 4-36 4-8 String Primitive Instructions 4-45 4-9 Program Counter Control Instructions 4-50 4-10 Jump-on-Condition 4-54 4-11 Signed vs. Unsigned Comparison Instructions 4-55 4-12 Loop Instructions 4-56 4-13 Processor Control Instructions 4-58 4-14 8086 I/O Instructions 4-59 4-15 8086 Interrupt Instructions 4-61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 4-7 8086 Logical Instructions 4-36 4-8 String Primitive Instructions 4-45 4-9 Program Counter Control Instructions 4-50 4-10 Jump-on-Condition 4-54 4-11 Signed vs. Unsigned Comparison Instructions 4-55 4-12 Loop Instructions 4-56 4-13 Processor Control Instructions 4-58 4-14 8086 I/O Instructions 4-59 4-15 8086 Interrupt Instructions 4-61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 4-8 String Primitive Instructions 4-45 4-9 Program Counter Control Instructions 4-50 4-10 Jump-on-Condition 4-54 4-11 Signed vs. Unsigned Comparison Instructions 4-55 4-12 Loop Instructions 4-56 4-13 Processor Control Instructions 4-58 4-14 8086 I/O Instructions 4-59 4-15 8086 Interrupt Instructions 4-61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| 4-9 Program Counter Control Instructions 4-50 4-10 Jump-on-Condition 4-54 4-11 Signed vs. Unsigned Comparison Instructions 4-55 4-12 Loop Instructions 4-56 4-13 Processor Control Instructions 4-58 4-14 8086 I/O Instructions 4-59 4-15 8086 Interrupt Instructions 4-61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 4-10 Jump-on-Condition 4-54 4-11 Signed vs. Unsigned Comparison Instructions 4-55 4-12 Loop Instructions 4-56 4-13 Processor Control Instructions 4-58 4-14 8086 I/O Instructions 4-59 4-15 8086 Interrupt Instructions 4-61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 4-11 Signed vs. Unsigned Comparison Instructions 4-55 4-12 Loop Instructions 4-56 4-13 Processor Control Instructions 4-58 4-14 8086 I/O Instructions 4-59 4-15 8086 Interrupt Instructions 4-61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 4-12 Loop Instructions 4-56 4-13 Processor Control Instructions 4-58 4-14 8086 I/O Instructions 4-59 4-15 8086 Interrupt Instructions 4-61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 4-13 Processor Control Instructions 4-58 4-14 8086 I/O Instructions 4-59 4-15 8086 Interrupt Instructions 4-61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 4-14 8086 I/O Instructions 4-59 4-15 8086 Interrupt Instructions 4-61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| 4-15 8086 Interrupt Instructions 4-61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| 4-15 8086 Interrupt Instructions 4-64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| 4-16 8086 Shift and Rotate Instructions 4-64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 8-1 Queue Status Outputs 8-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 8-2 Status Line Outputs 8-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| 8-3 Crystal Vendors 8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| 8-4 8086 Bus Signals during Reset 8-19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| 8-5 8288 Outputs during Passive State 8-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 9-1 Pin Assignment of Bus Signals on Multibus Board P1 Connector 9-2 P2 Connector Pin Assignment of Optional Bus Signals 9-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9-2 |

# Introduction

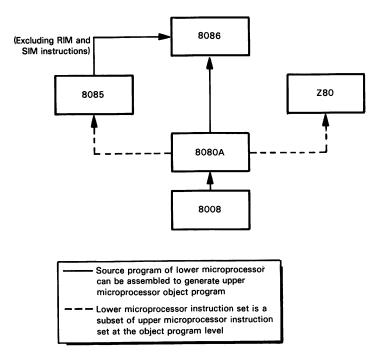

This book focuses on three topics: general programming concepts and practices, the 8086 microprocessor with its assembly language, and logic design using the 8086 microprocessor. The discussion of general programming concepts and practices is relevant to any microprocessor, but the rest of the book is specific to the 8086. As such, this book becomes a how-to text for the 8086.

The prime source for the 8086 microprocessor is:

INTEL CORPORATION 3065 Bowers Avenue Santa Clara, California 95051

The second source is:

MOSTEK, INC. 1215 West Crosby Road Carrollton, Texas 75006

The discussion of general programming concepts and practices begins by looking at the relationship between the programmer and a computer, since this is ultimately what determines the nature of any design project. Why do some programmers work with machine language while others program in assembly language or perhaps higher level languages? Different types of applications call for different types of programming. In each case good programming practices should be cultivated. A set of rules is described to achieve this goal, and two examples are used to illustrate programming projects.

The description of the 8086 microprocessor itself covers assembly language programming and hardware design.

For the assembly language programmer, the 8086 CPU architecture and the microprocessor's assembly language instruction set are described in detail.

For the hardware designer, timing and bus considerations are described for all signals normally input to the microprocessor or output by it. Single-bus and multi-bus architectures are covered. The standard Intel Multibus is described in detail.

### WHAT THIS BOOK ASSUMES YOU KNOW

This book assumes that you have a working knowledge of general microprocessor concepts, and the ideas presented in An Introduction to Microcomputers: Volume l-Basic Concepts, 2nd Revision, by A. Osborne, Osborne/McGraw-Hill, 1980. Accordingly, this book does not cover any elementary material such as binary arithmetic, buffers, or CPU architecture fundamentals.

The 8086 microprocessor and its immediate support parts are described in great detail within this book. The 8089 I/O Processor is referred to, but it is not described in detail. For a detailed description of this part, see *The 8089 I/O Processor Handbook*, by A. Osborne, Osborne/McGraw-Hill, 1980.

1

# **Programming**

#### **ASSEMBLY LANGUAGE**

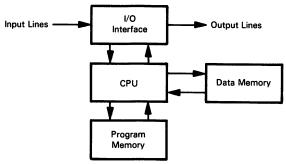

What is the function of assembly language in a microcomputer system? How does it differ from machine language or higher level language programming? This chapter will answer these questions by assessing the various roles that assembly language plays. In a very general sense, all microcomputer systems take the following form: