305-490 Issue 2

# **AT&T 3B2** Computer Technical Reference Manual

# NOTICE

The information in this document is subject to change without notice. AT&T assumes no responsibility for any errors that may appear in this document.

Copyright<sup>©</sup> 1990 AT&T All Rights Reserved Printed in U.S.A.

# TRADEMARKS

The following is a listing of the trademarks that are used in this manual:

- CENTRONICS Registered trademark of Centronics Data Computer Corp.

- Datakit Registered trademark of AT&T

- FUJITSU Registered trademark of FUJITSU Limited, Nakahara-Ku, Kawasaki, Japan

- INTEL Registered trademark of Intel Corp.

- MS-DOS Registered trademark of Microsoft Corp.

- Teletype Registered trademark of AT&T

- UNIX Registered trademark of AT&T

- WE Registered trademark of AT&T

- WREN Trademark of Control Data Corp.

# **ORDERING INFORMATION**

Additional copies of this document can be ordered by calling

| Toll free: | 1-800-432-6600 | In the U.S.A. |

|------------|----------------|---------------|

|            | 1-800-255-1242 | In Canada     |

| Toll:      | 1-317-352-8557 | Worldwide     |

OR by writing to:

AT&T Customer Information Center Attn: Customer Service Representative P.O. Box 19901 Indianapolis, IN 46219

# TRAINING INFORMATION

The *AT&T Education and Training Catalogue of Courses* and course schedules are free and can be ordered by contacting your account executive or by calling toll free:

1-800-554-6400 (extension 7150)

Training information can also be accessed electronically through our computerized catalogue:

DIAL: 1-800-662-0662 or 1-614-764-5566 LOGIN: comcats PASSWORD: 88cat

# **Table of Contents**

C

\_

| 1. | INTRODUCTION                                |

|----|---------------------------------------------|

|    | INTRODUCTION                                |

|    | PURPOSE OF TECHNICAL REFERENCE MANUAL 1-1   |

|    | MANUAL ORGANIZATION                         |

|    | RELATED DOCUMENTATION                       |

|    |                                             |

| 2. | EQUIPMENT DESCRIPTION                       |

|    | EQUIPMENT DESCRIPTION                       |

|    | SYSTEM (EQUIPMENT) CONFIGURATIONS           |

|    | HARDWARE OVERVIEW                           |

|    | SYSTEM BOARDS                               |

|    | RANDOM ACCESS MEMORY CARDS                  |

|    | BACKPLANE BOARDS                            |

|    | AUXILIARY DISK INTERFACE (ED-4C632-30)      |

|    | DUART CONNECTOR-2 INTERFACE (ED-4C492-35,G5 |

|    | and ED-4C631-35,G2)                         |

|    | CM195A NETWORK INTERFACE CARD               |

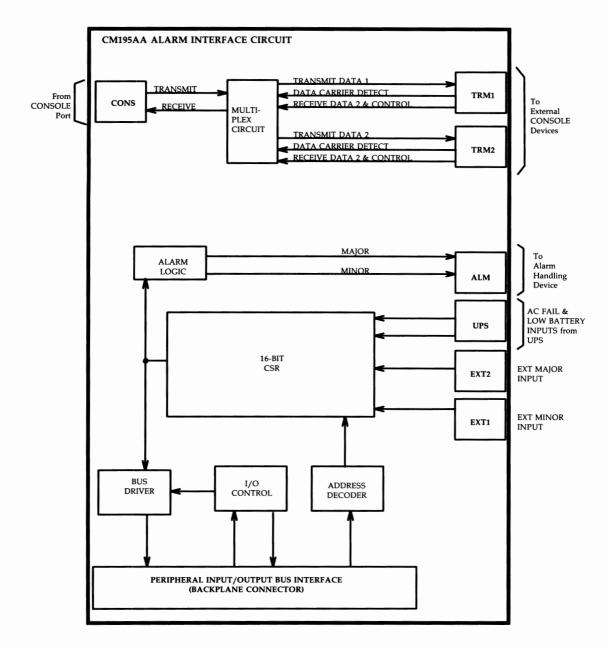

|    | CM195AA ALARM INTERFACE CIRCUIT CARD 2-143  |

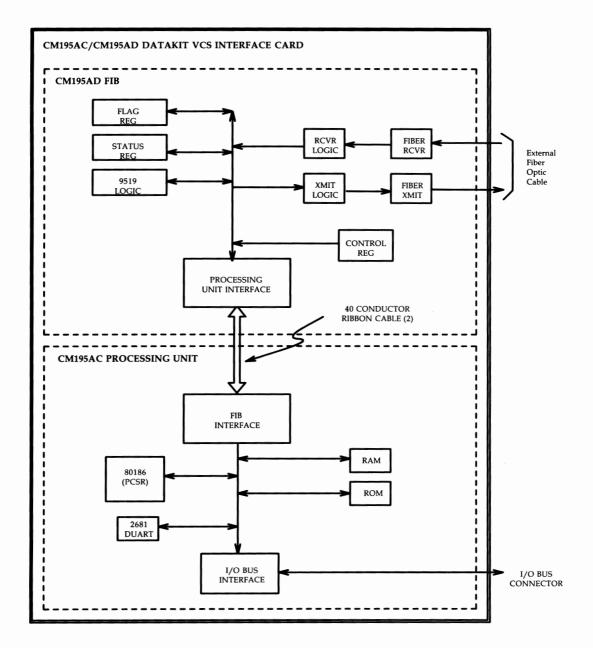

|    | CM195AC/CM195AD "DATAKIT" VCS INTERFACE     |

|    | CARD                                        |

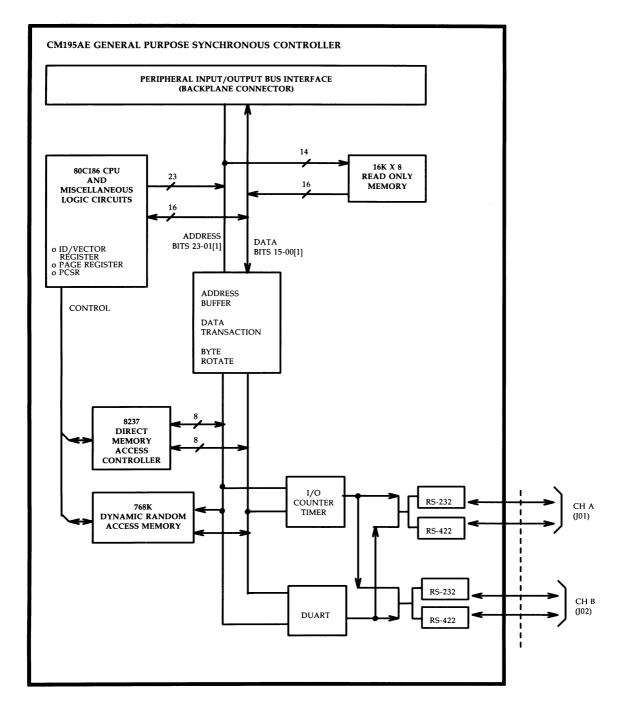

|    | CM195AE GPSC CARD PACKAGE                   |

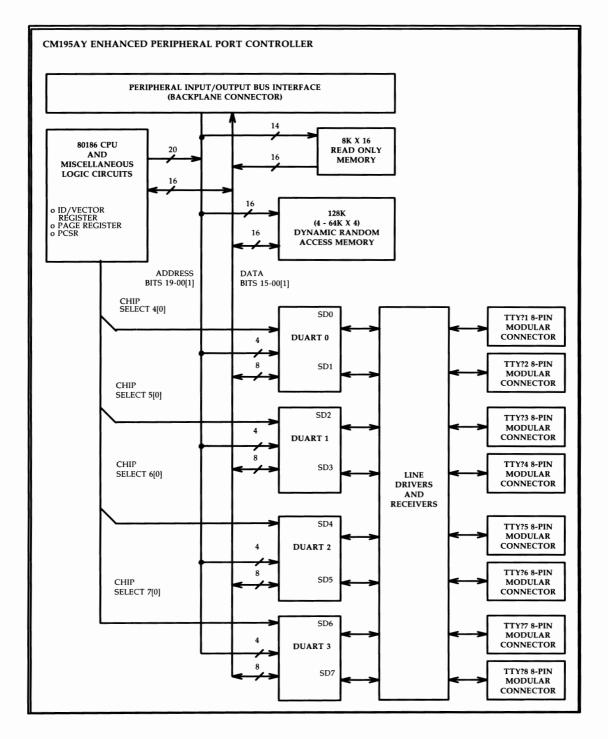

|    | CM195AY EPORTS CARD                         |

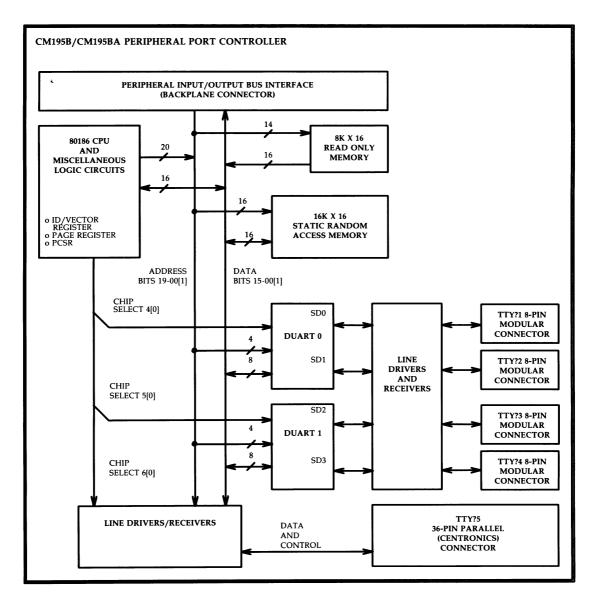

|    | CM195B PORTS CARD                           |

|    | CM195BA PORTS CARD                          |

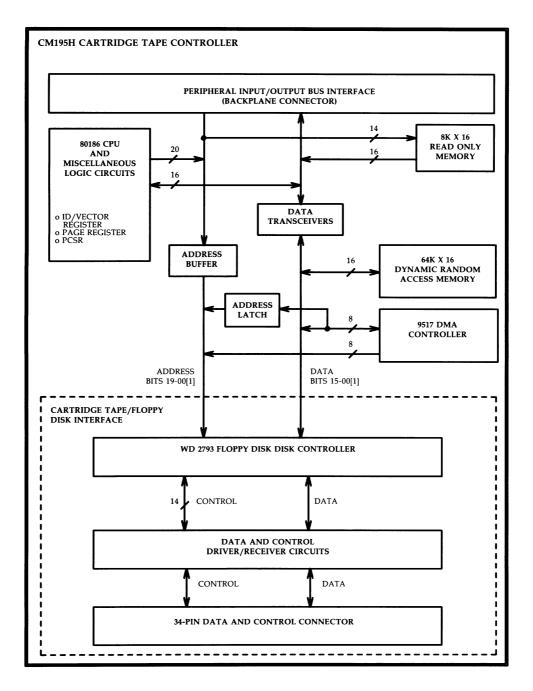

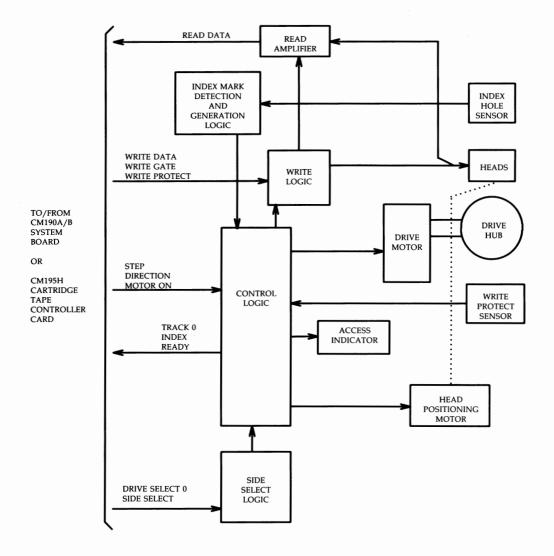

|    | CM195H CARTRIDGE TAPE CONTROLLER CARD 2-157 |

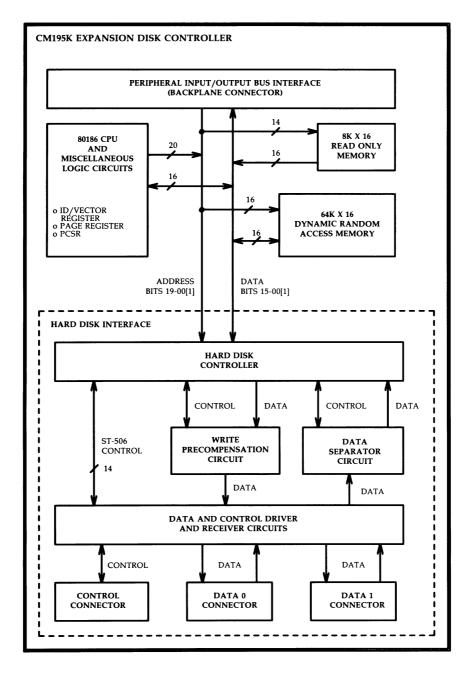

|    | CM195K EXPANSION DISK CONTROLLER CARD 2-159 |

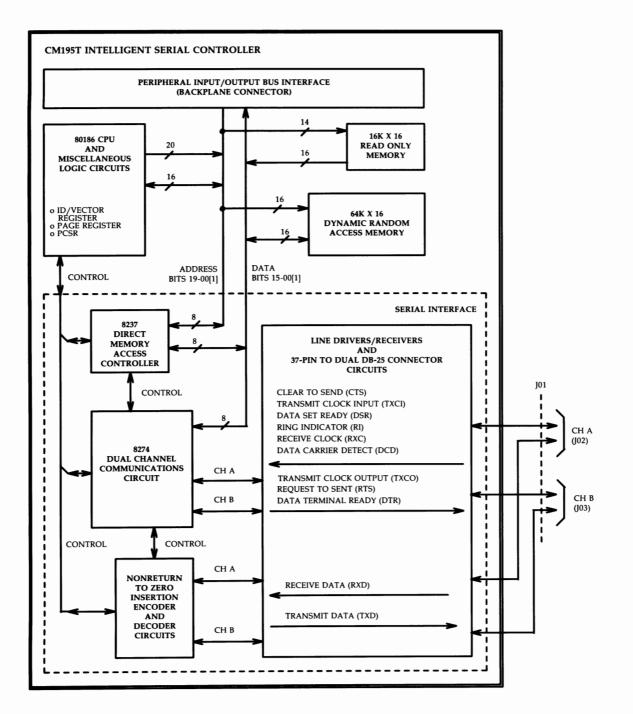

|    | CM195T INTELLIGENT SERIAL CONTROLLER        |

|    | CARD                                        |

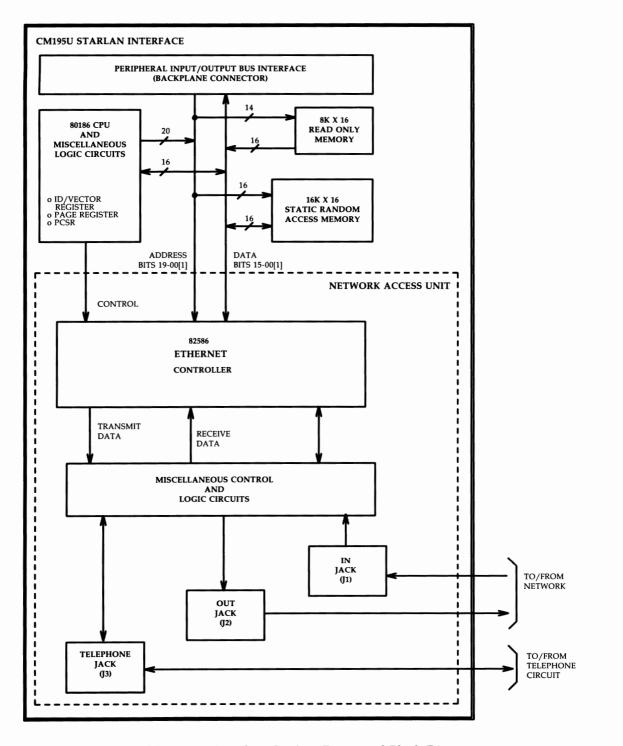

|    | CM195U STARLAN INTERFACE CARD               |

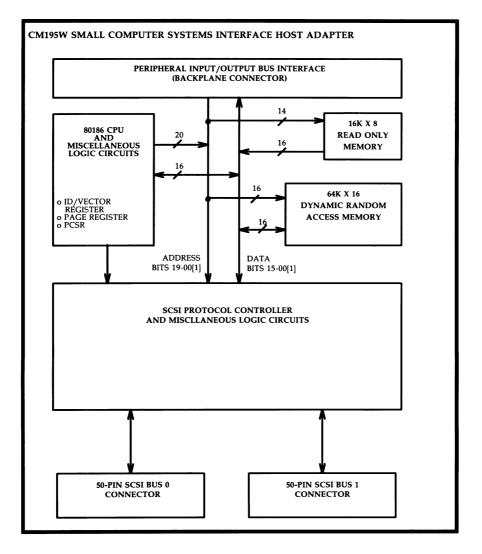

|    | CM195W SCSI HOST ADAPTER CARD               |

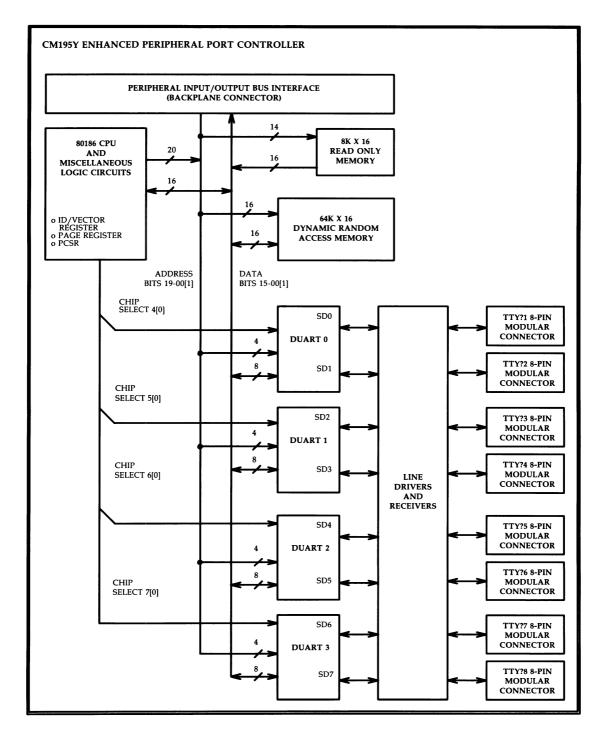

|    | CM195Y EPORTS CARD                          |

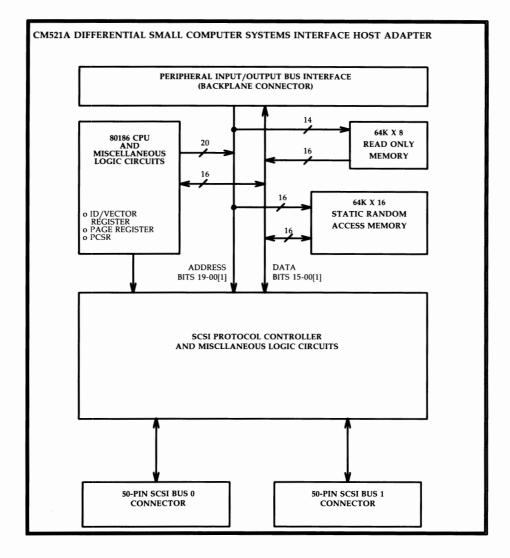

|    | CM521A DIFFERENTIAL SCSI HOST ADAPTER       |

|    | CARD                                        |

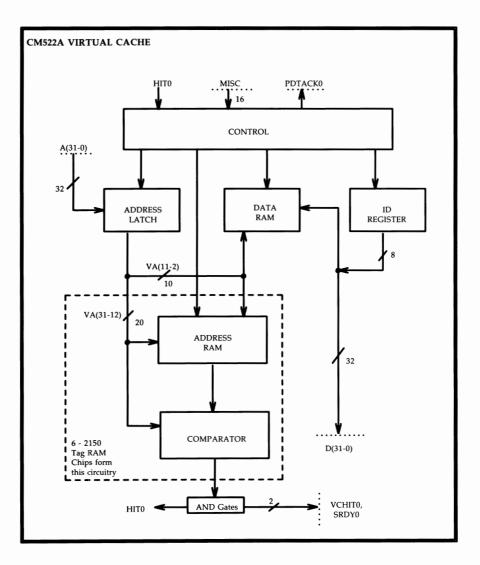

|    | CM522A VCACHE CARD                          |

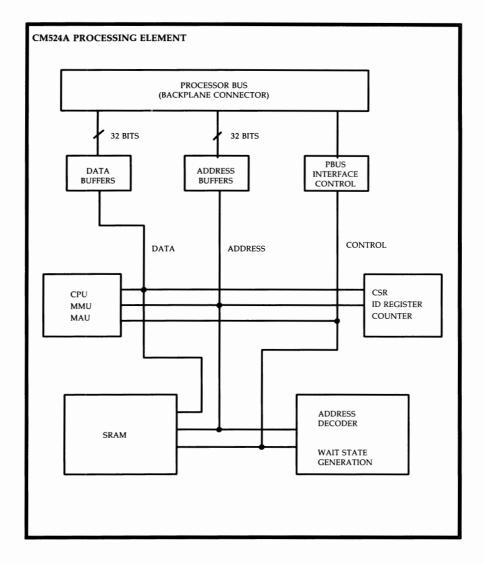

|    | CM524A PROCESSING ELEMENT CARD              |

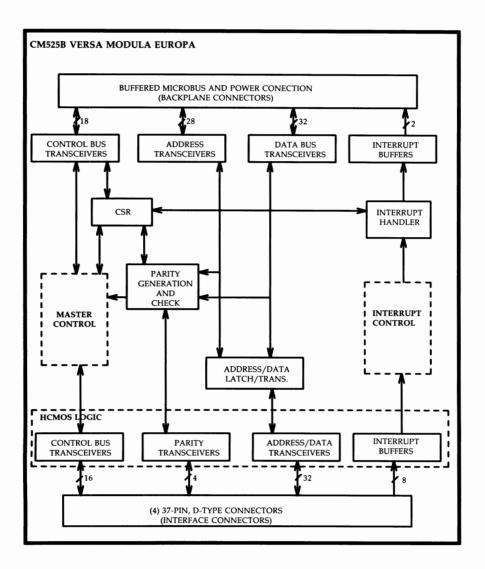

|    | CM525B VMEbus CARD                          |

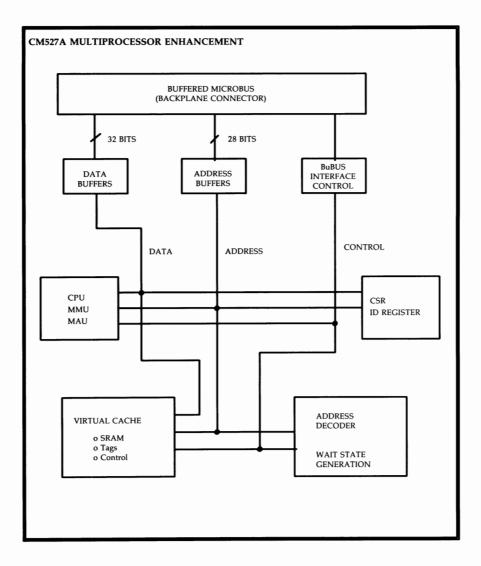

|    | CM527A MULTIPROCESSOR ENHANCEMENT                                                | 0.455 |

|----|----------------------------------------------------------------------------------|-------|

|    | CARD                                                                             |       |

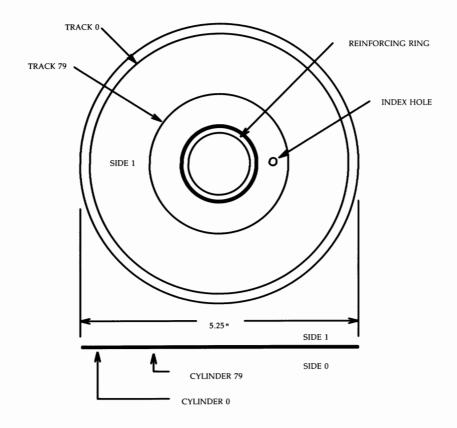

|    | 23-MEGABYTE CARTRIDGE TAPE DRIVE                                                 | 2-179 |

|    | $(KS-23165,L1)  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 2-183 |

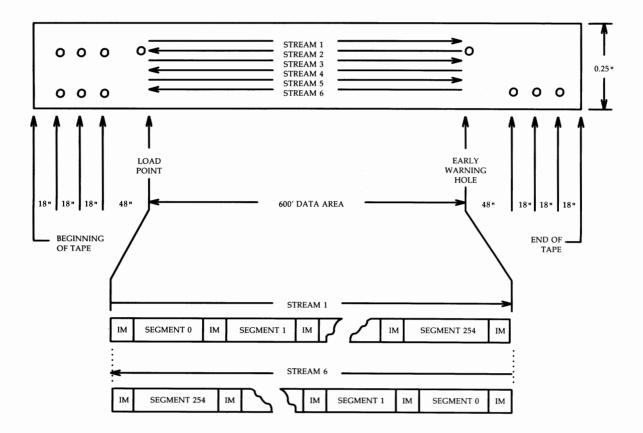

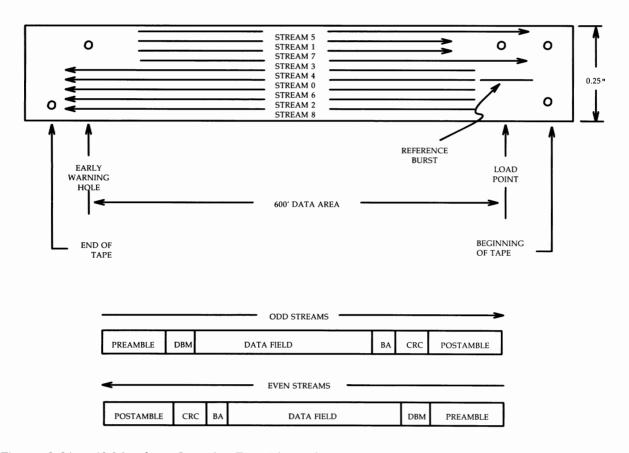

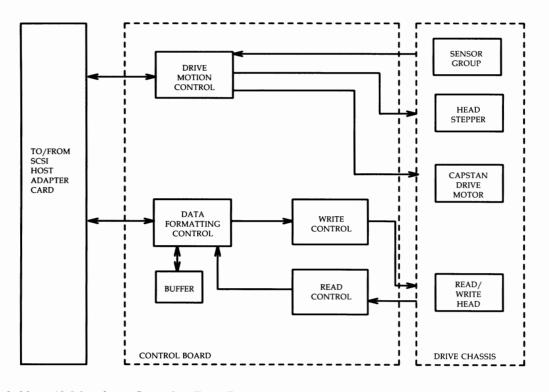

|    | 60-MEGABYTE CARTRIDGE TAPE DRIVE                                                 | 2-105 |

|    | (KS-23417,L2)                                                                    | 2-187 |

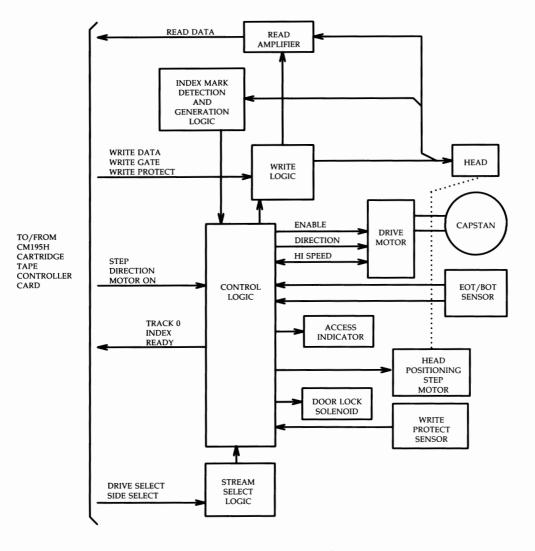

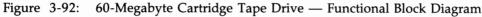

|    | 120-MEGABYTE CARTRIDGE TAPE DRIVE                                                | 2-107 |

|    | (KS-23465,L1A)                                                                   | 2-189 |

|    | HARD DISK DRIVES                                                                 | 2-191 |

|    | POWER-EQUIPMENT DESCRIPTION                                                      |       |

|    | MISCELLANEOUS EQUIPMENT AND APPARATUS                                            |       |

|    | ~                                                                                |       |

| 3. | FUNCTIONAL DESCRIPTION                                                           | 3-1   |

|    |                                                                                  |       |

|    | FUNCTIONAL DESCRIPTION                                                           |       |

|    | SYSTEM OVERVIEW                                                                  |       |

|    | SYSTEM BOARDS                                                                    | 3-31  |

|    | RANDOM ACCESS MEMORY CARDS                                                       |       |

|    | BACKPLANES                                                                       | 3-153 |

|    | CM195A NETWORK INTERFACE CARD                                                    |       |

|    | CM195AA ALARM INTERACE CIRCUIT CARD                                              | 3-175 |

|    | CM195AC/CM195AD "DATAKIT" VCS INTERFACE                                          |       |

|    | CARD                                                                             | 3-183 |

|    | CM195AE GPSC CARD                                                                | 3-189 |

|    | CM195AY EPORTS CARD                                                              |       |

|    | CM195B/CM195BA PORTS CARD                                                        |       |

|    | CM195H CARTRIDGE TAPE CONTROLLER CARD                                            |       |

|    | CM195K EXPANSION DISK CONTROLLER CARD                                            | 3-215 |

|    | CM195T INTELLIGENT SERIAL CONTROLLER                                             |       |

|    | CARD                                                                             |       |

|    | CM195U STARLAN INTERFACE CARD                                                    |       |

|    | CM195W SCSI HOST ADAPTER CARD                                                    |       |

|    | CM195Y EPORTS CARD                                                               |       |

|    | CM521A DIFFERENTIAL SCSI HOST ADAPTER CARD                                       |       |

|    | CM522A VCACHE CARD                                                               |       |

|    | CM524A PROCESSING ELEMENT CARD                                                   |       |

|    | CM525B VMEbus CARD                                                               | 3-271 |

| CM527A MULTIPROCESSOR ENHANCEMENT                |       |

|--------------------------------------------------|-------|

| CARD                                             | 3-277 |

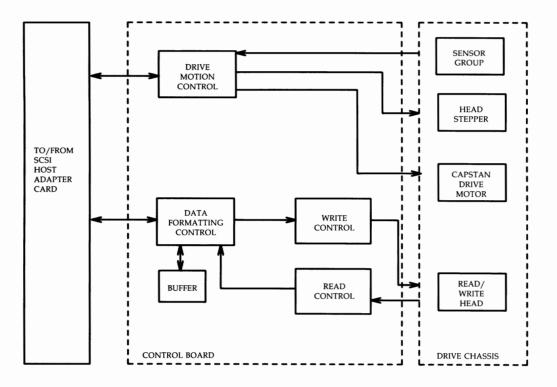

| FLOPPY DISK DRIVE                                | 3-283 |

| 23-MEGABYTE CARTRIDGE TAPE DRIVE                 | 3-287 |

| 60-MEGABYTE SCSI CARTRIDGE TAPE DRIVE            | 3-291 |

| 120-MEGABYTE SCSI CARTRIDGE TAPE DRIVE           | 3-295 |

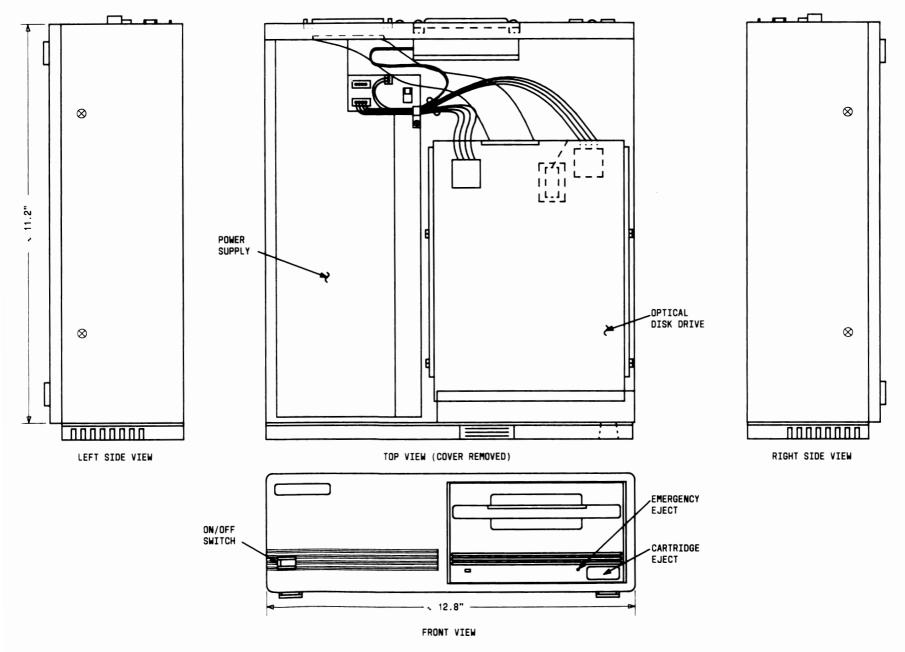

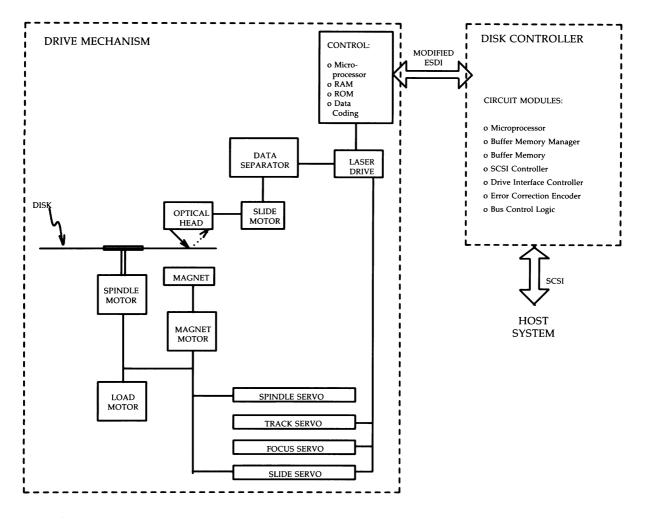

| AT&T SCSI REWRITABLE OPTICAL DISK DRIVE          | 3-299 |

| HARD DISK DRIVES                                 | 3-301 |

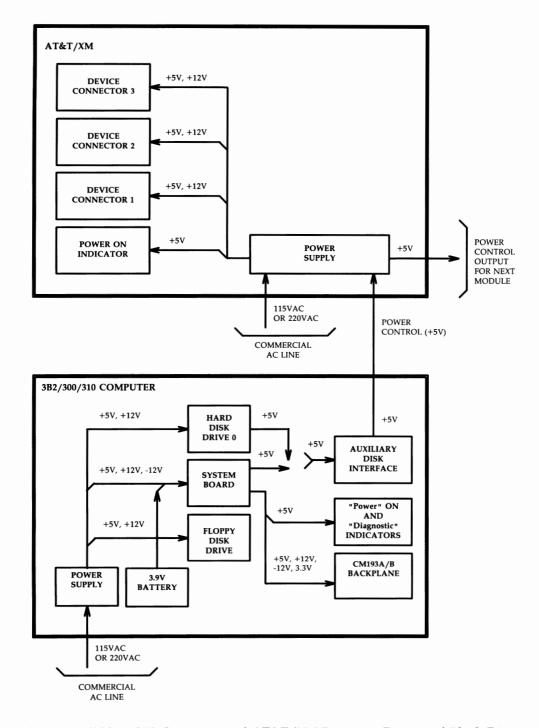

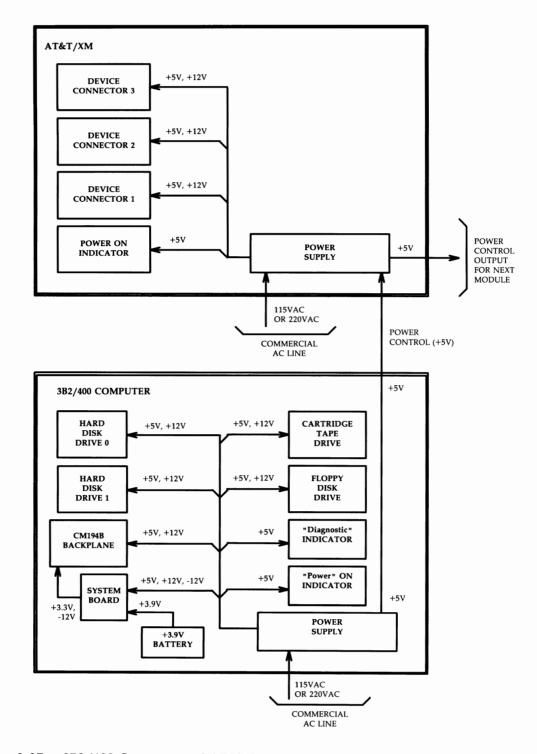

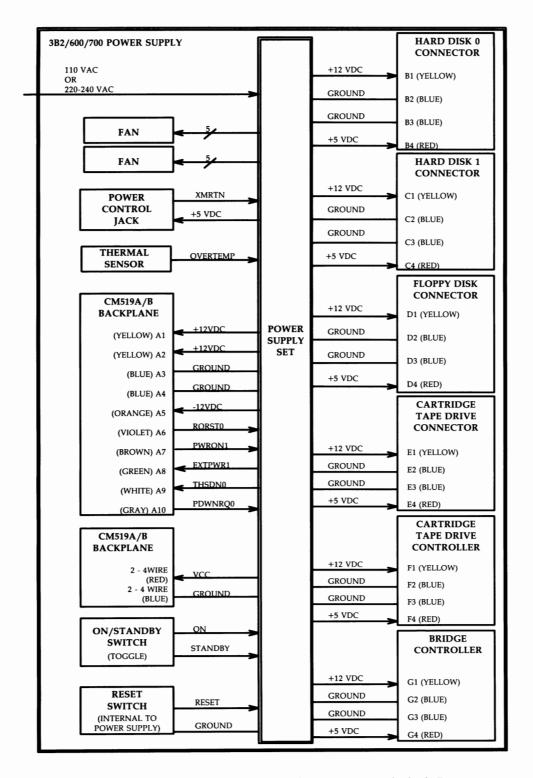

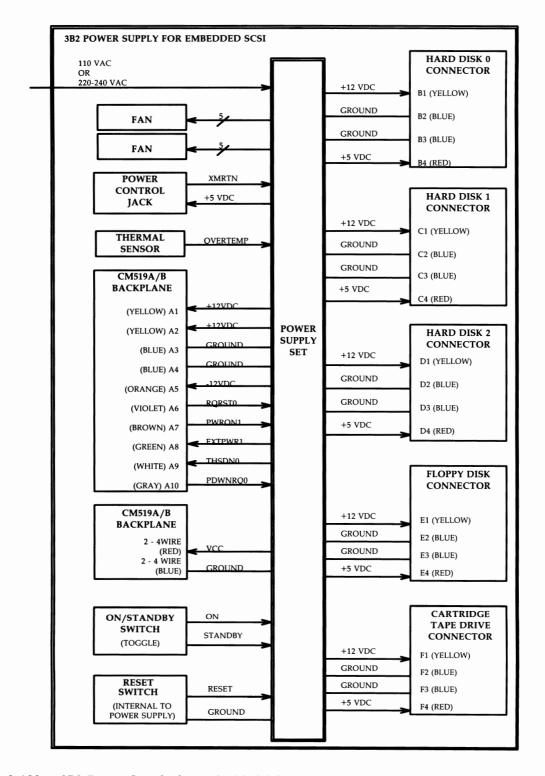

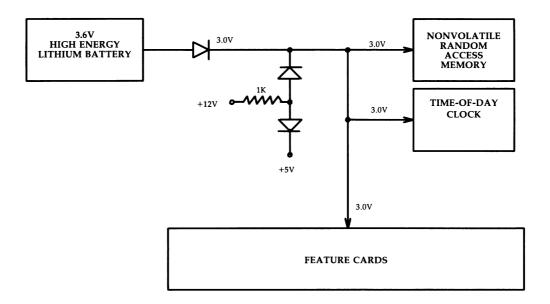

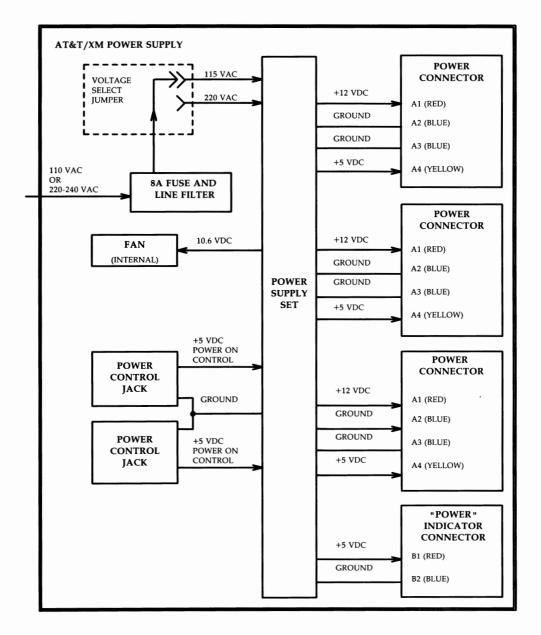

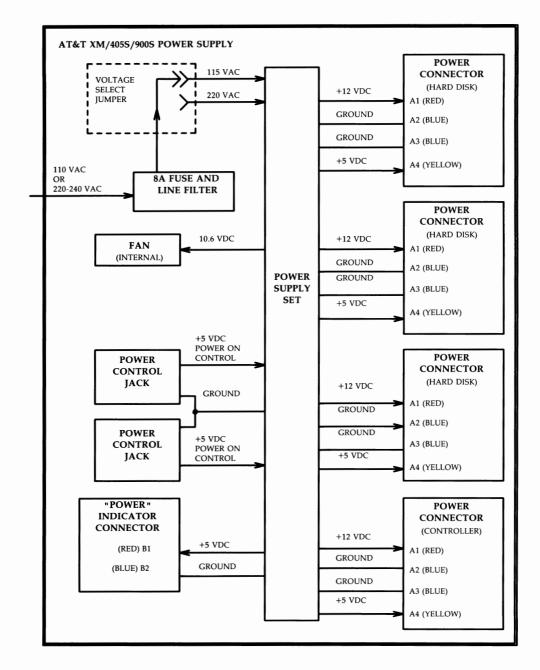

| POWER—FUNCTIONAL DESCRIPTION                     | 3-303 |

| Appendix A: VIRTUAL ADDRESS SPACE                | A-1   |

| Appendix B: CONNECTOR AND CABLING<br>INFORMATION | B-1   |

| Index                                            | IN-1  |

C

$\bigcirc$

# **List of Figures**

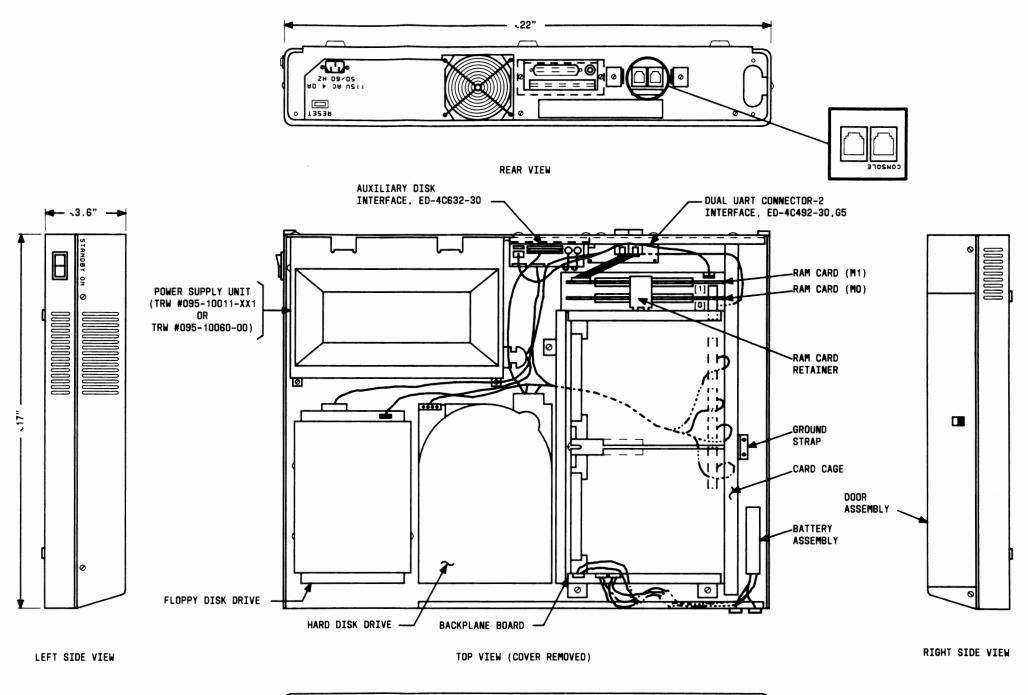

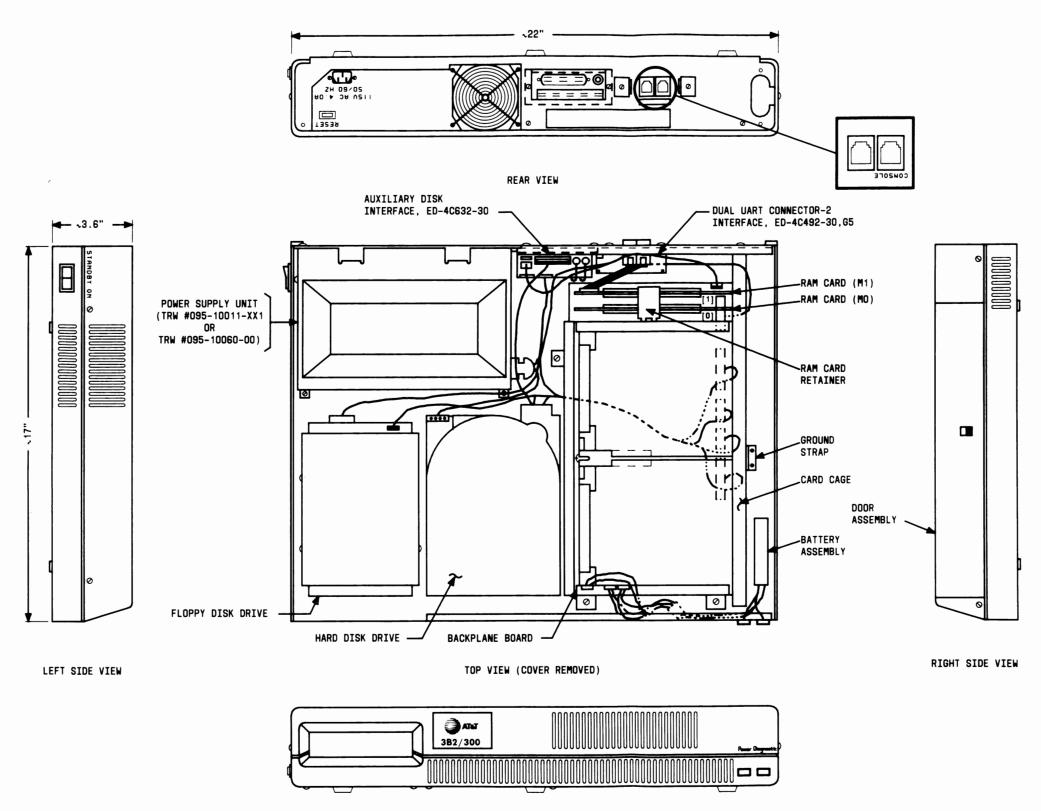

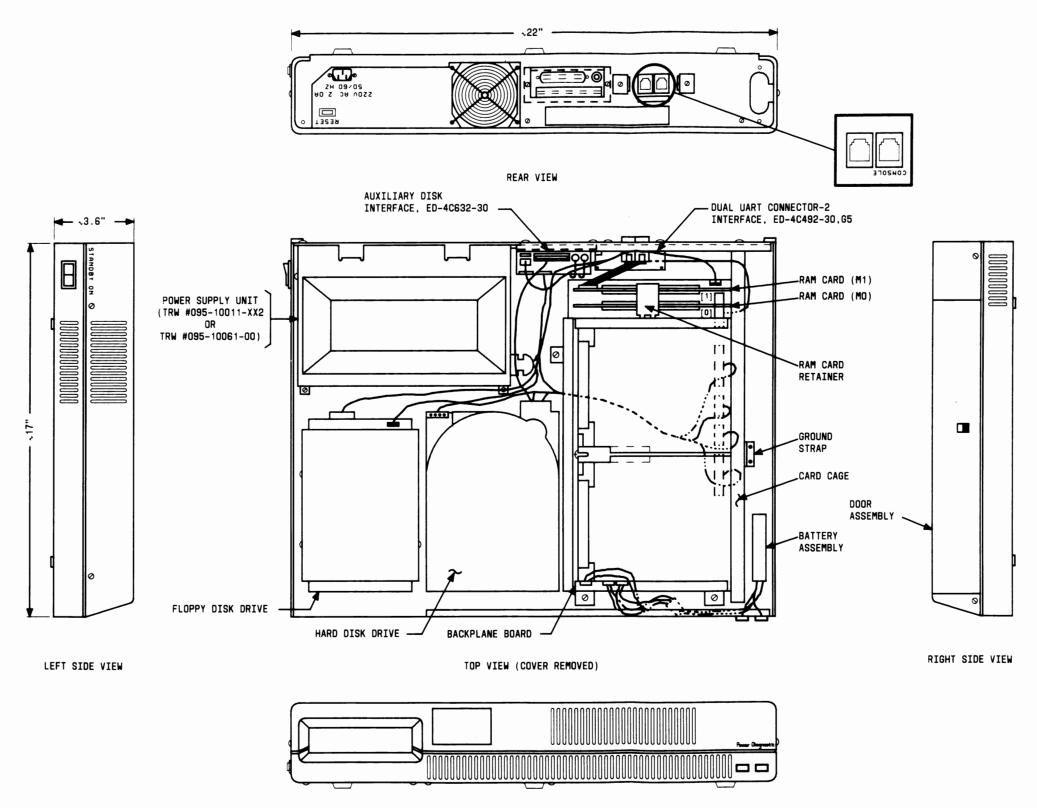

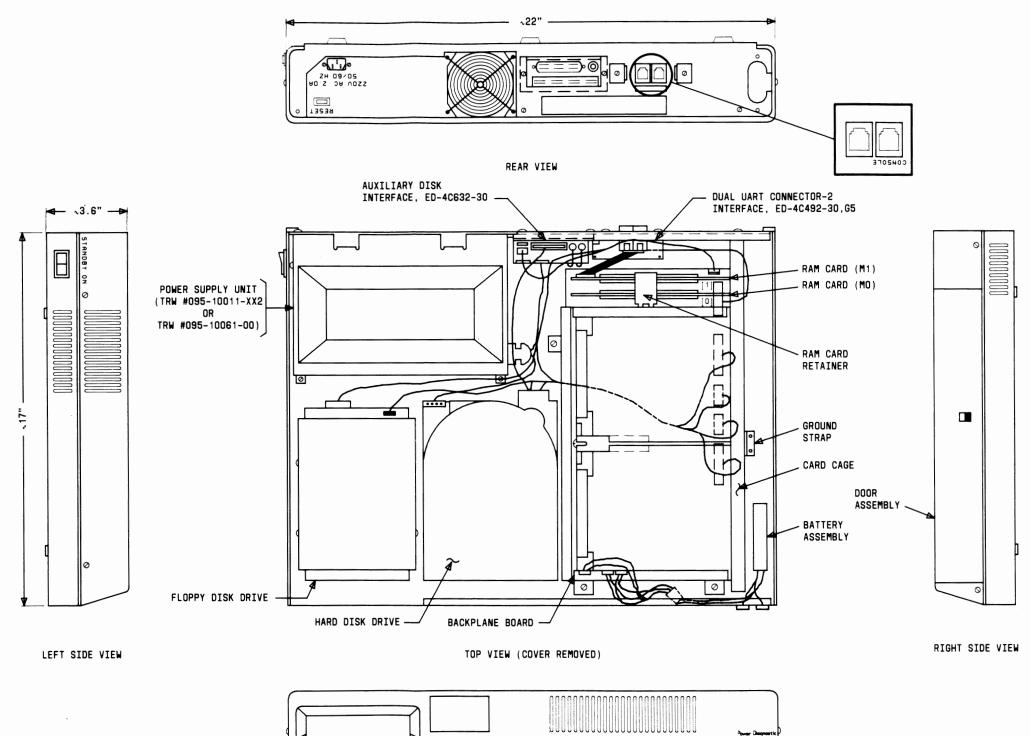

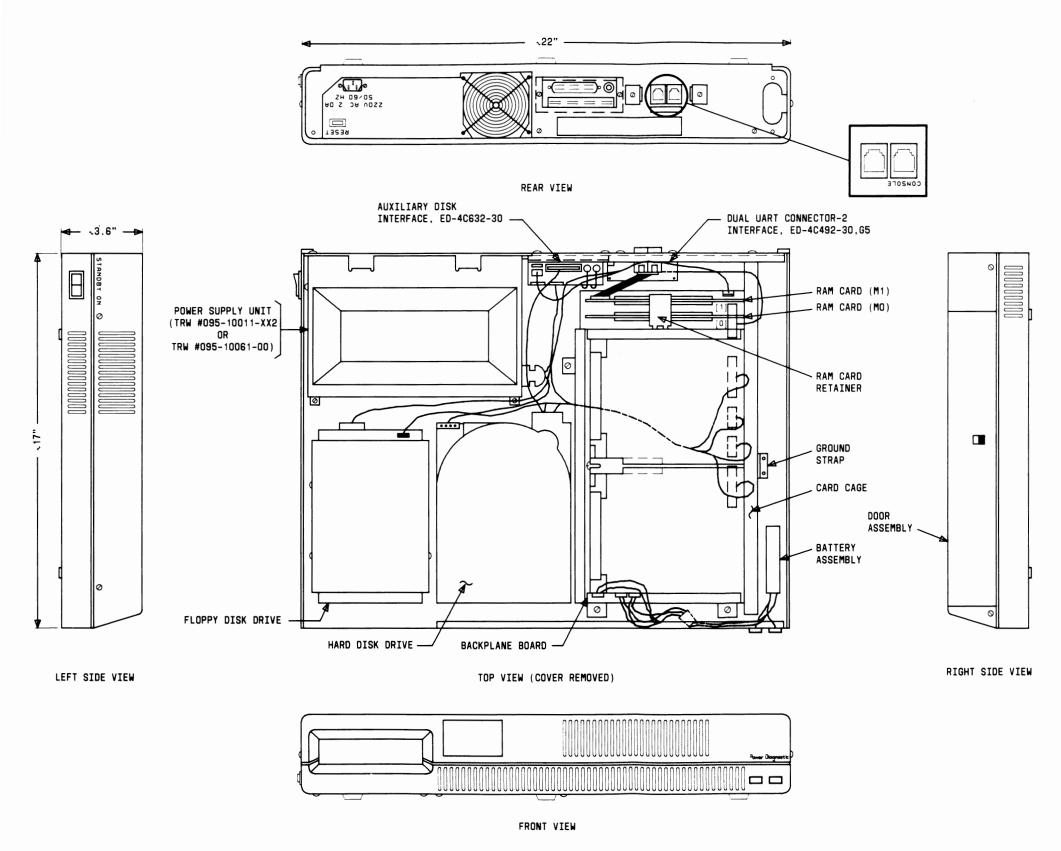

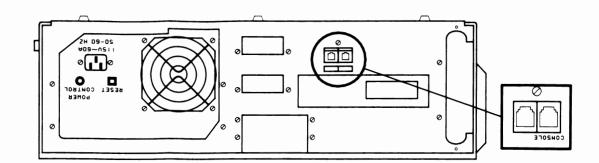

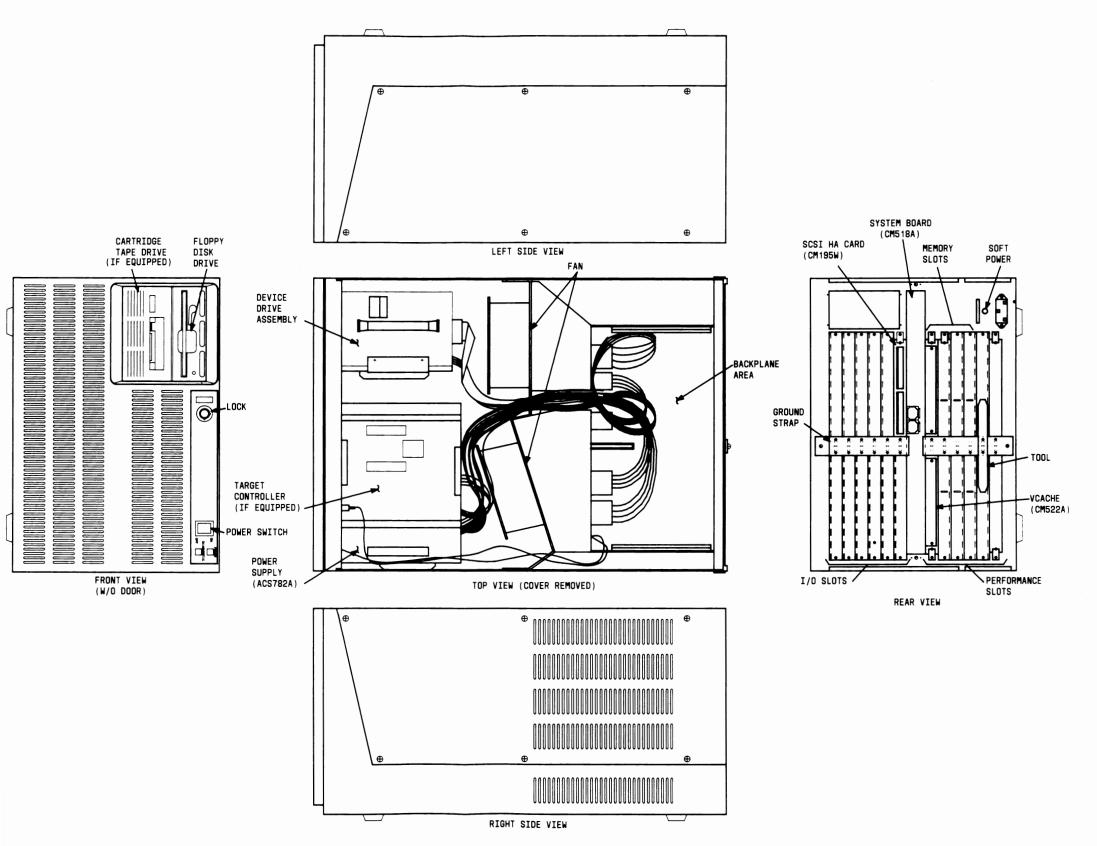

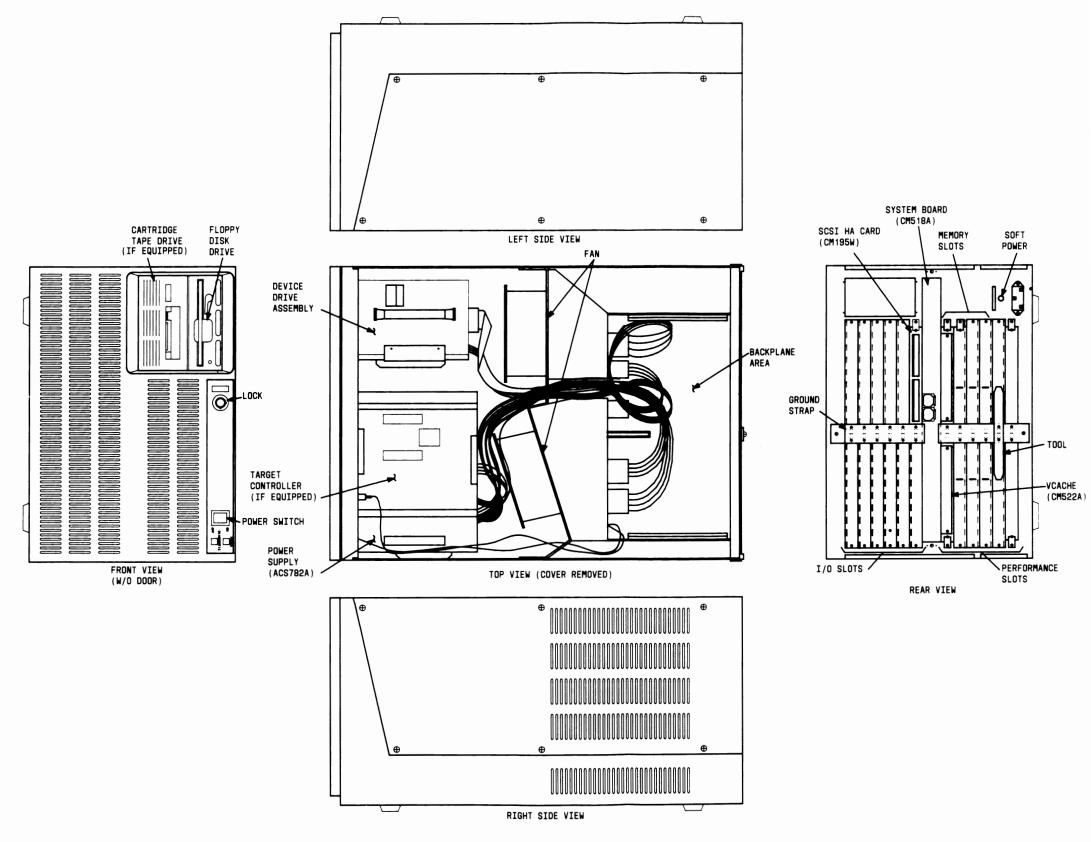

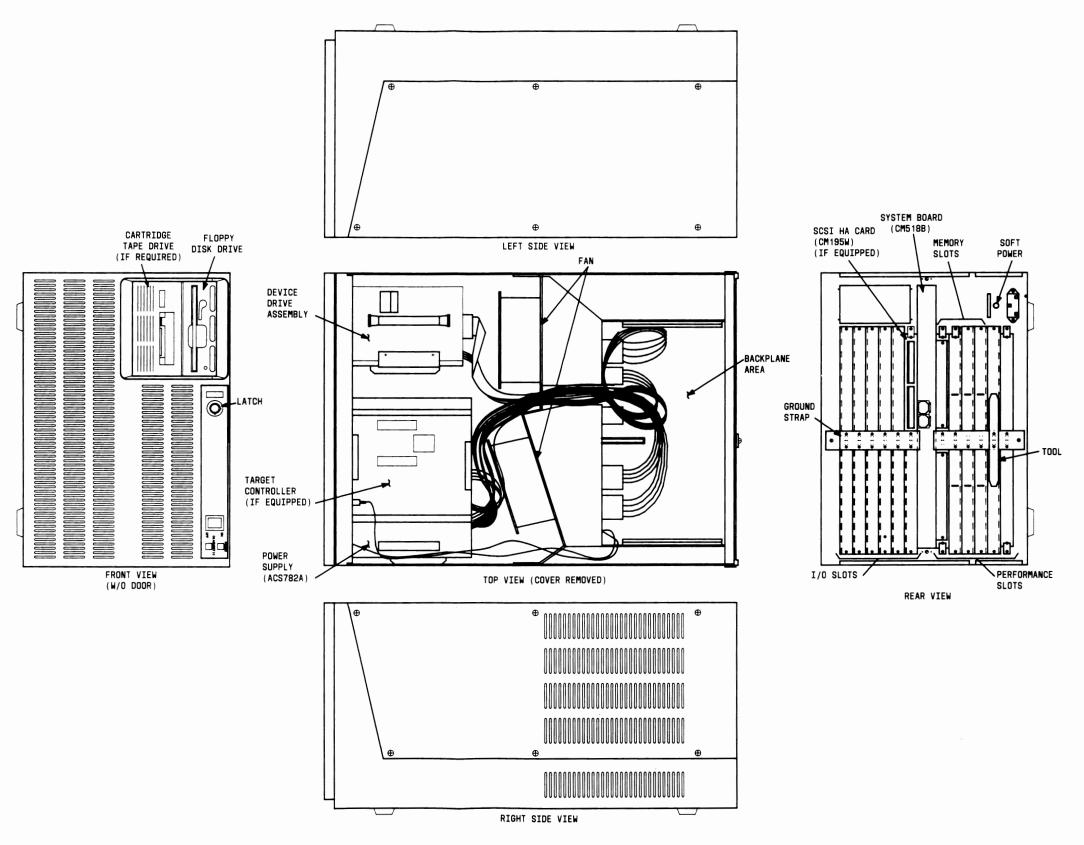

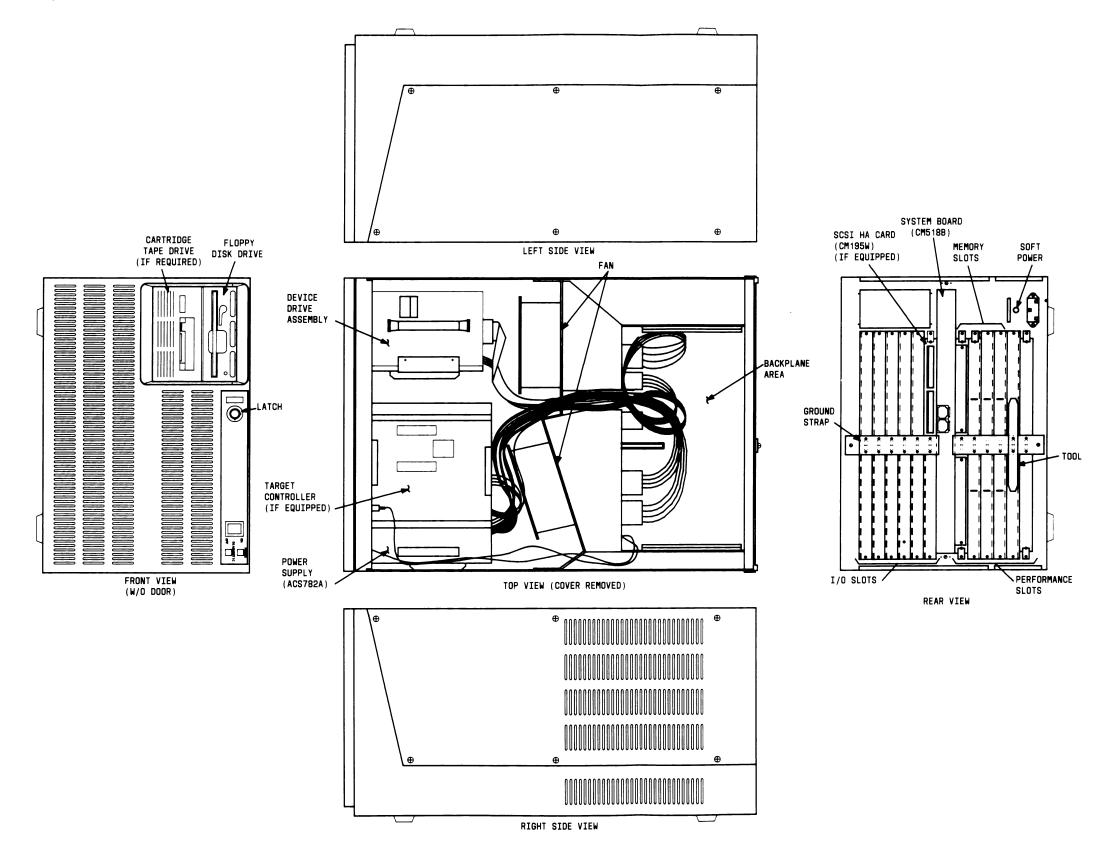

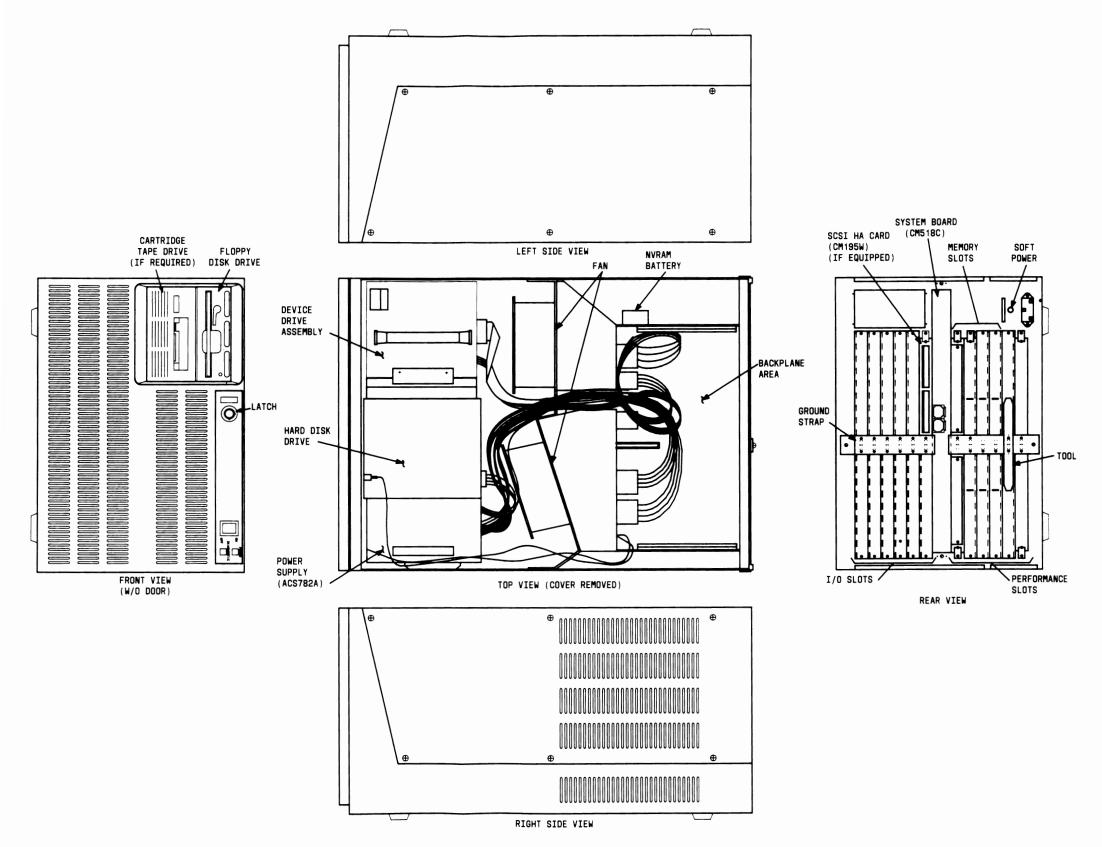

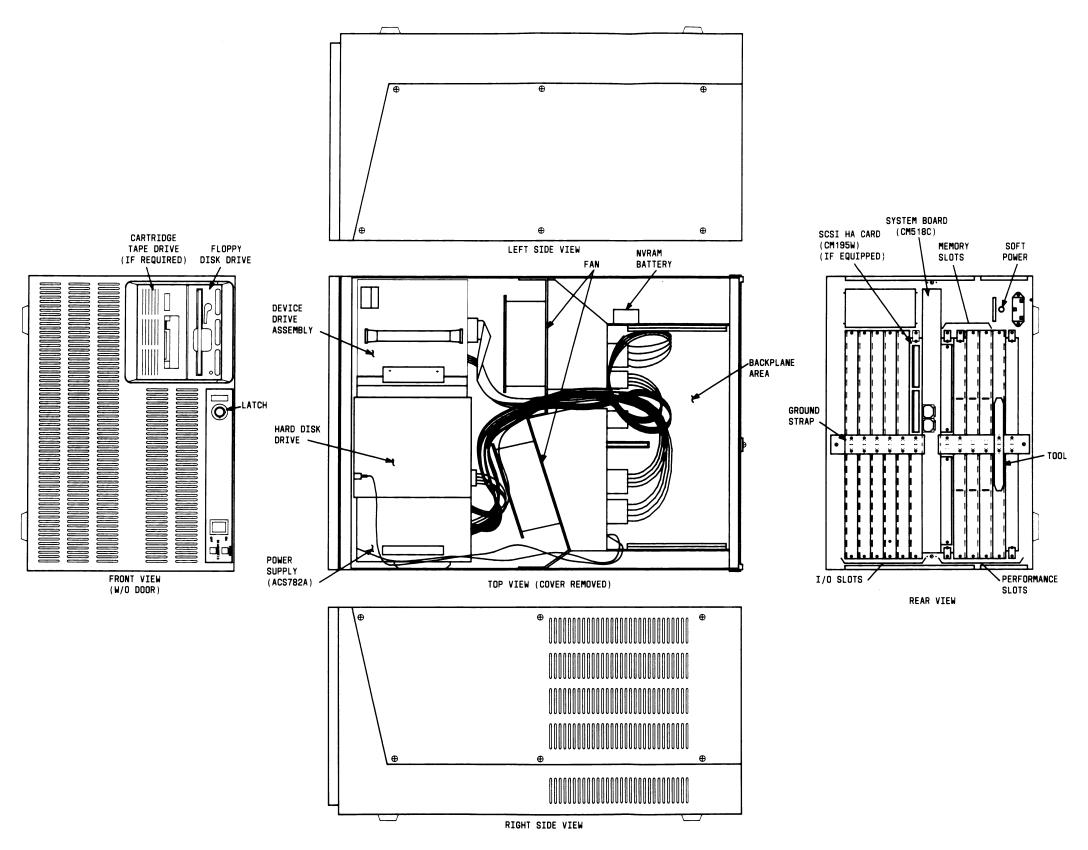

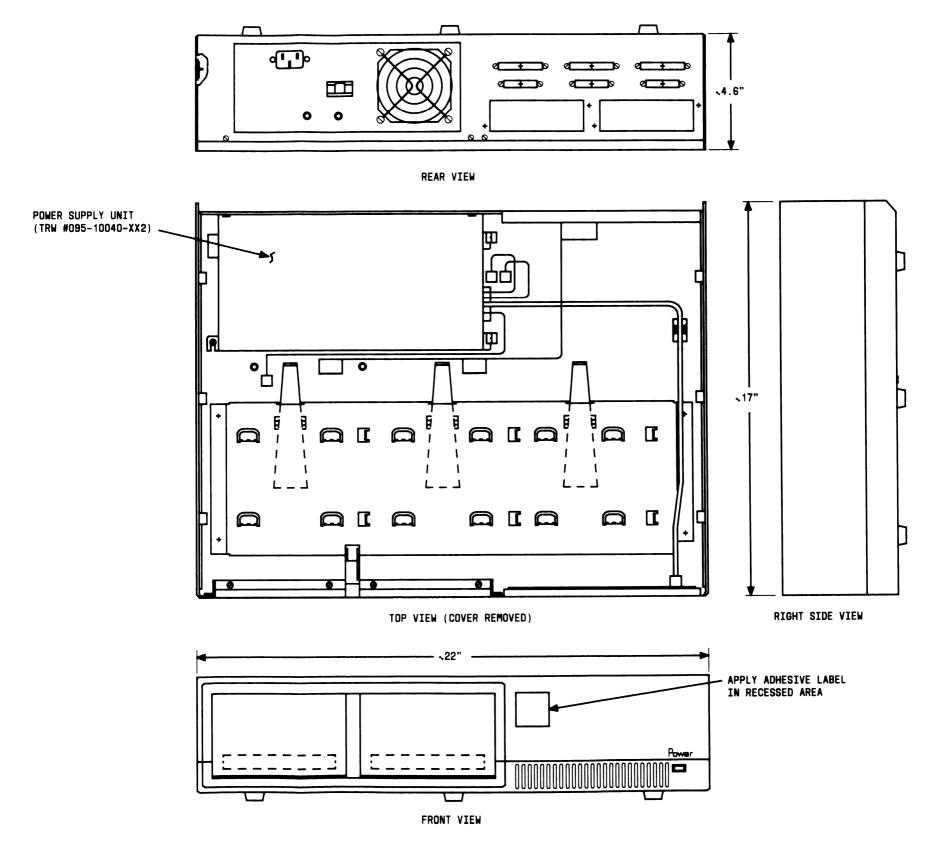

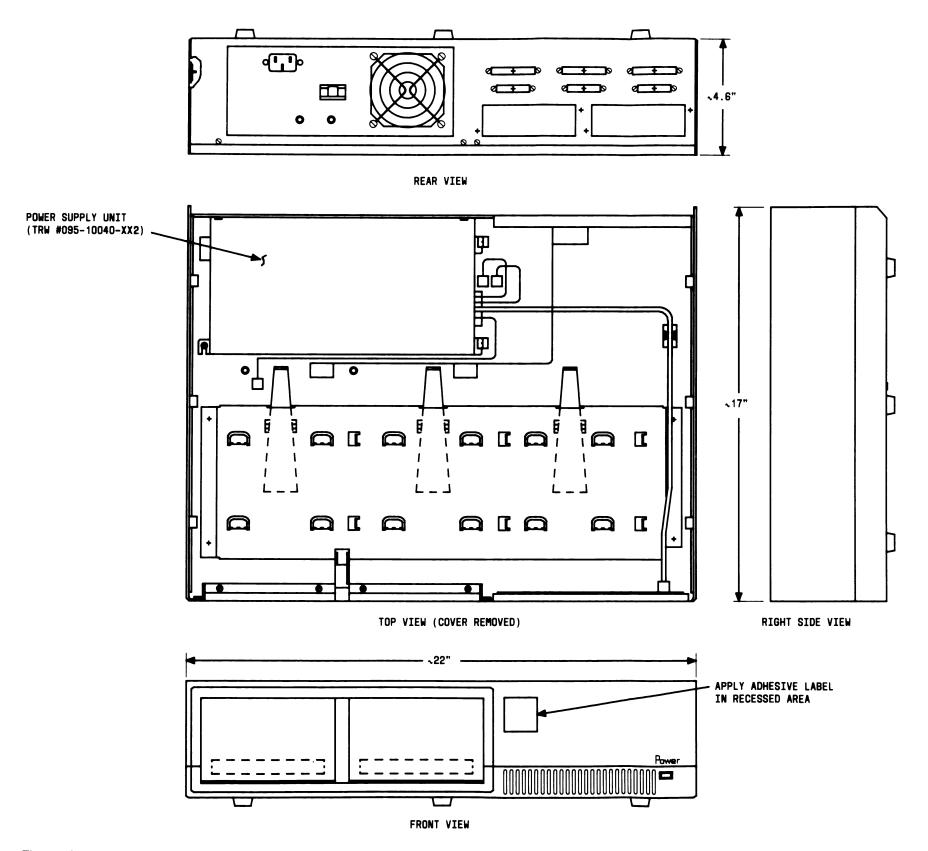

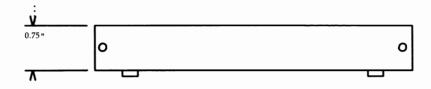

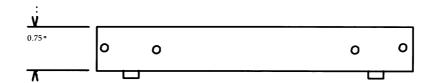

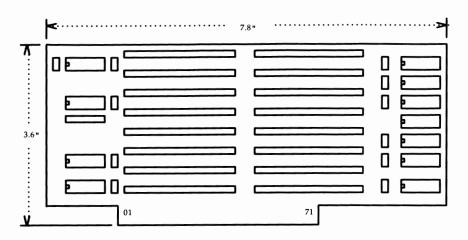

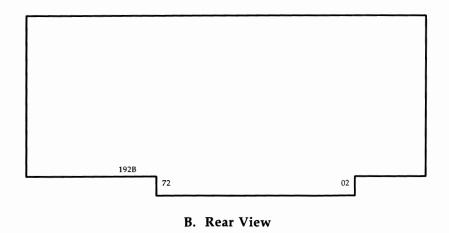

| Figure 2-1:                  | Domestic 3B2/300 Computer Cabinet Assembly Drawing (ED-4C492-30)                                                                  | 2-15         |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------|

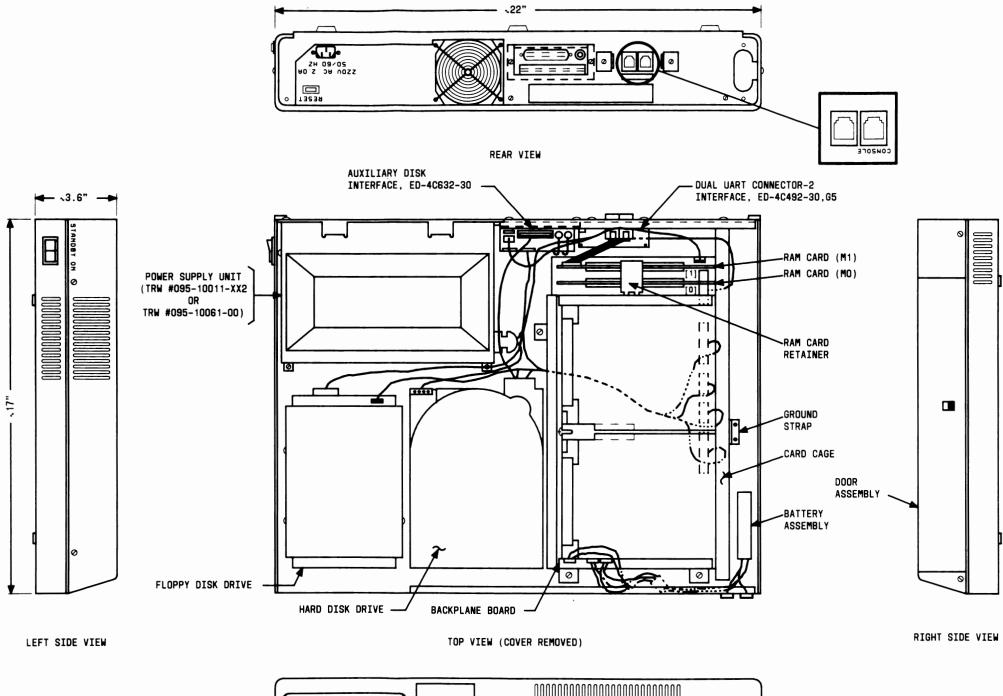

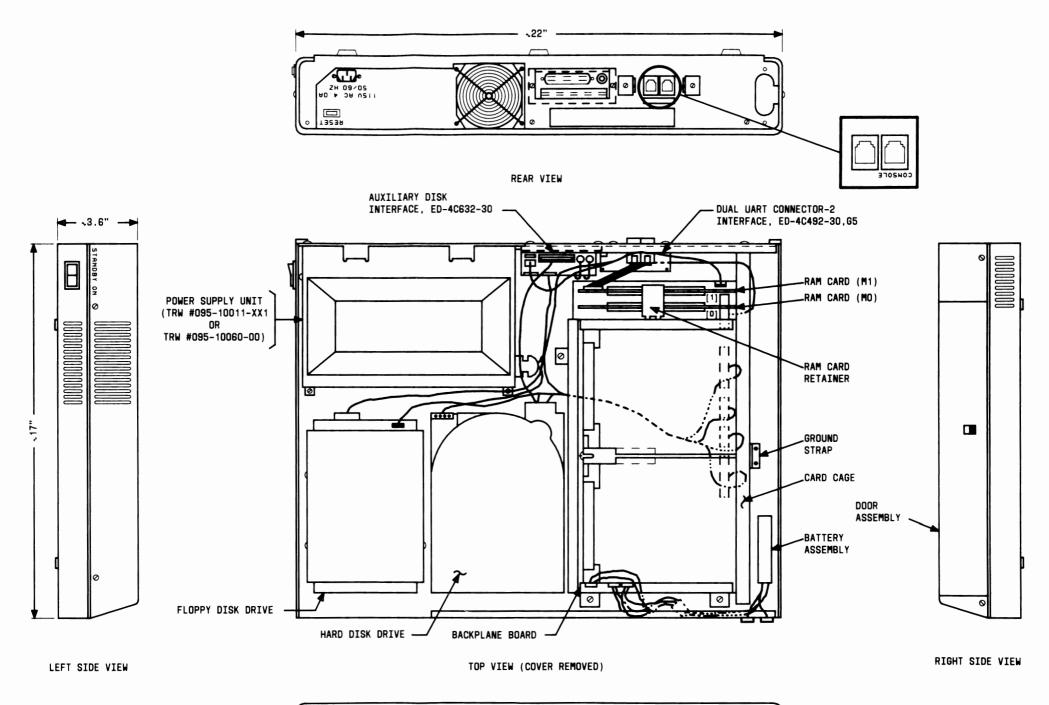

| Figure 2-2:                  | International 3B2/300 Computer Cabinet Assembly Drawing                                                                           |              |

|                              | (ED-4C560-30)                                                                                                                     | 2-19         |

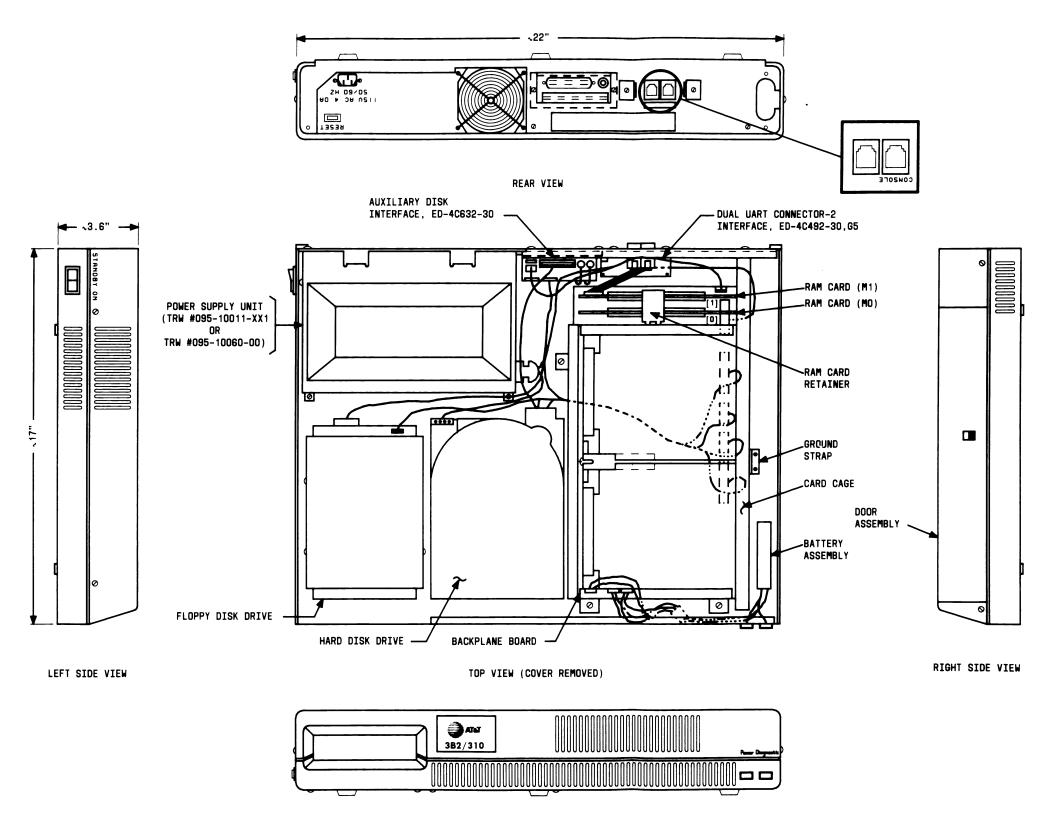

| Figure 2-3:                  | Domestic 3B2/310 Computer Cabinet Assembly Drawing (ED-4C645-30)                                                                  | 2-23         |

| Figure 2-4:                  | International 3B2/310 Computer Cabinet Assembly Drawing                                                                           |              |

| Figure 0 Fr                  | $(ED-4C646-30) \dots \dots$ | 2-27         |

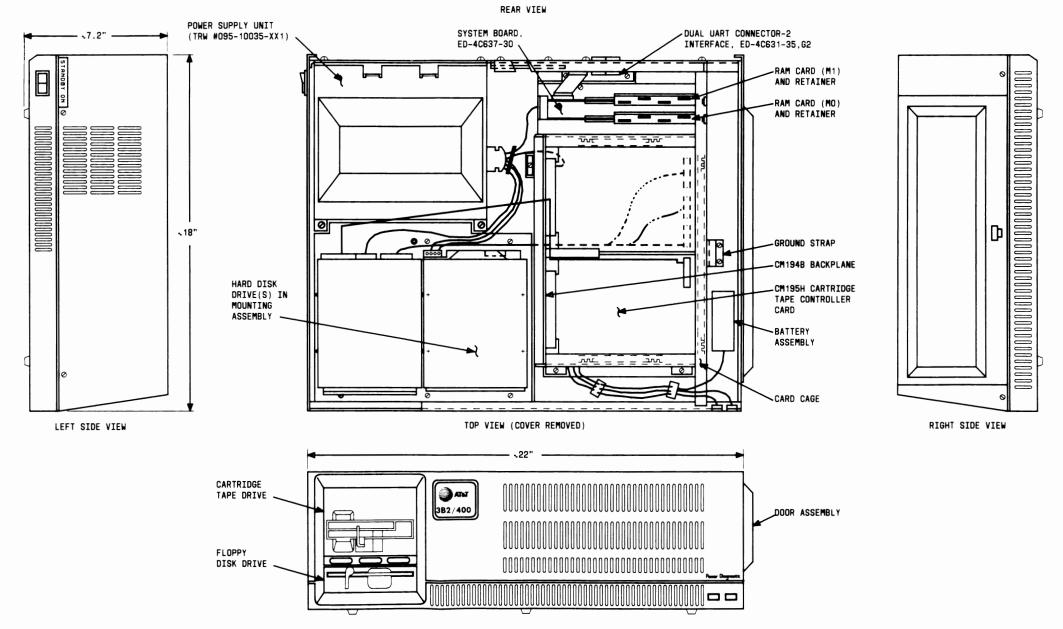

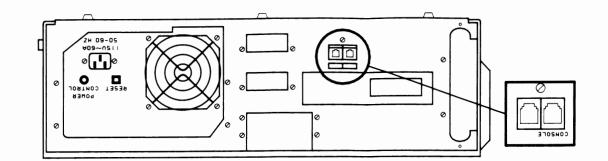

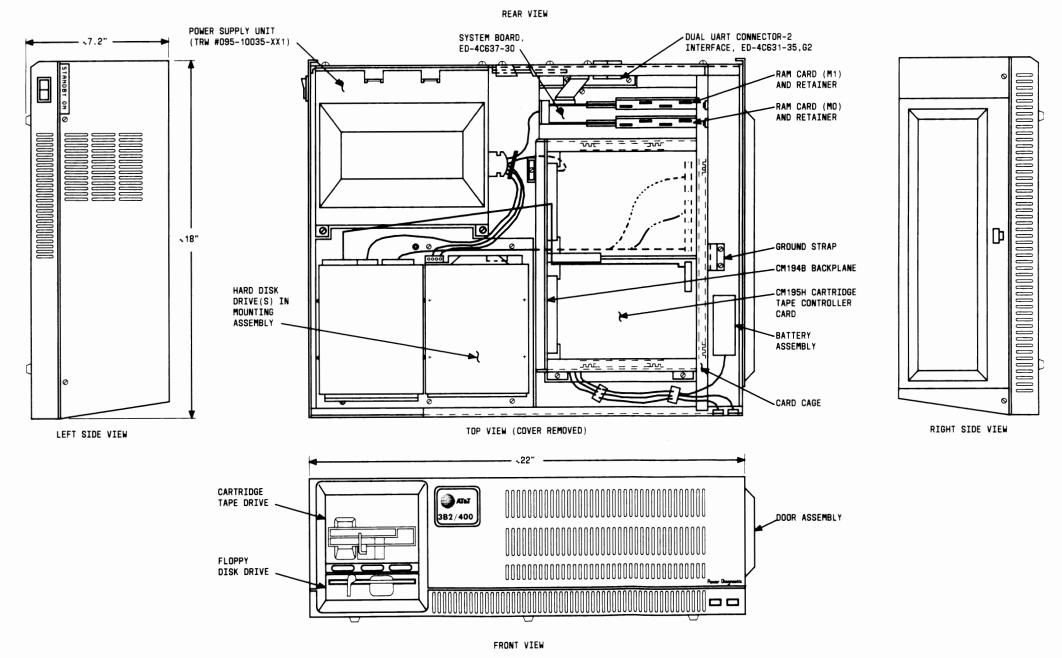

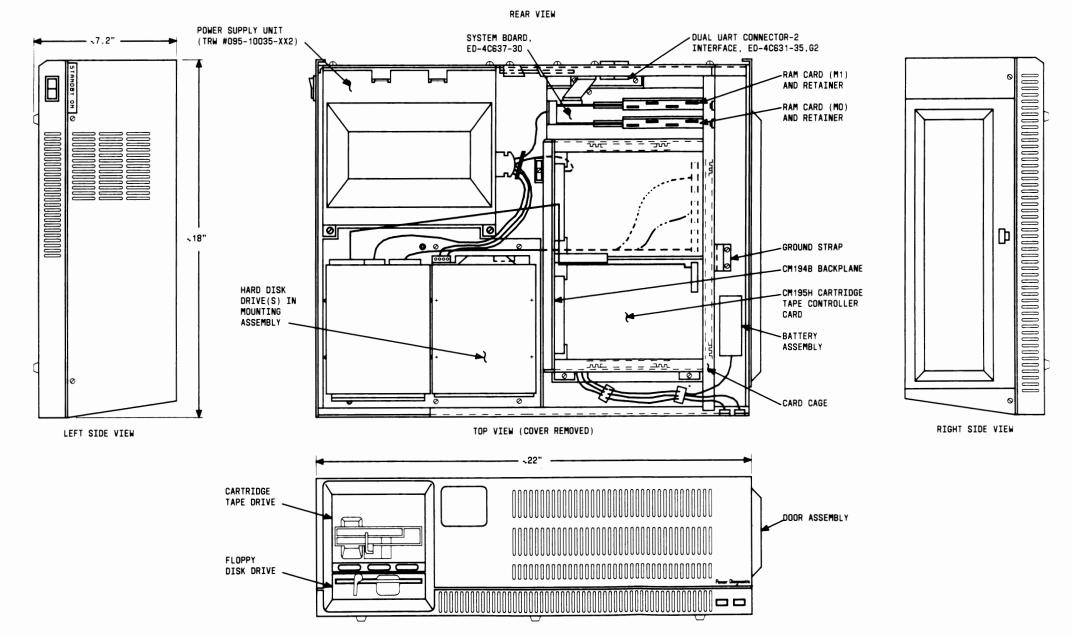

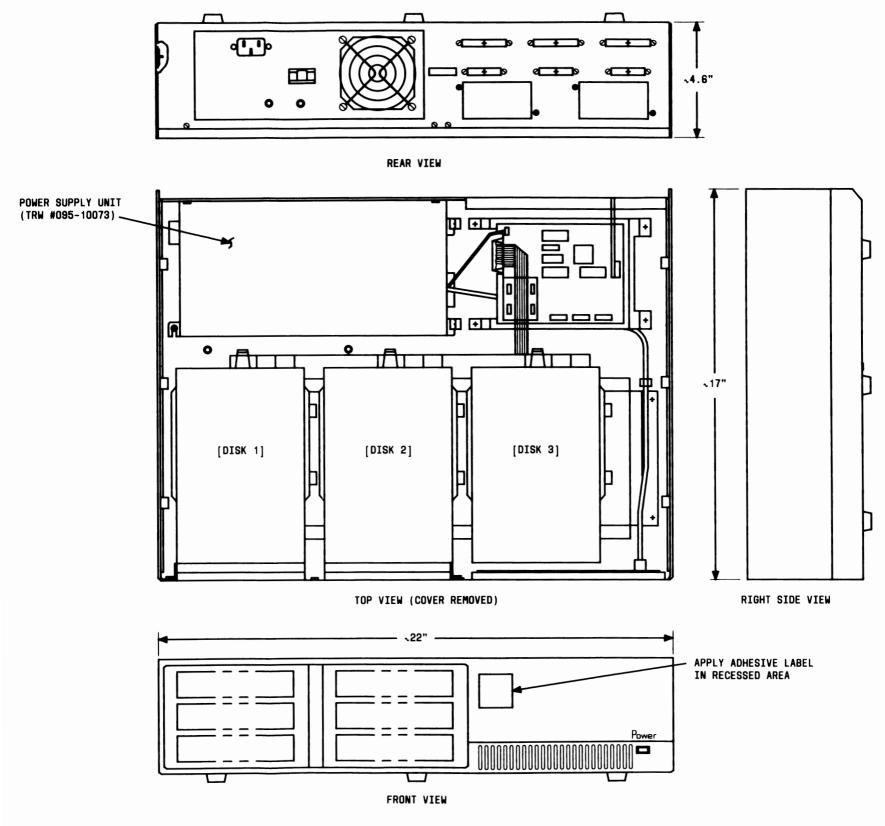

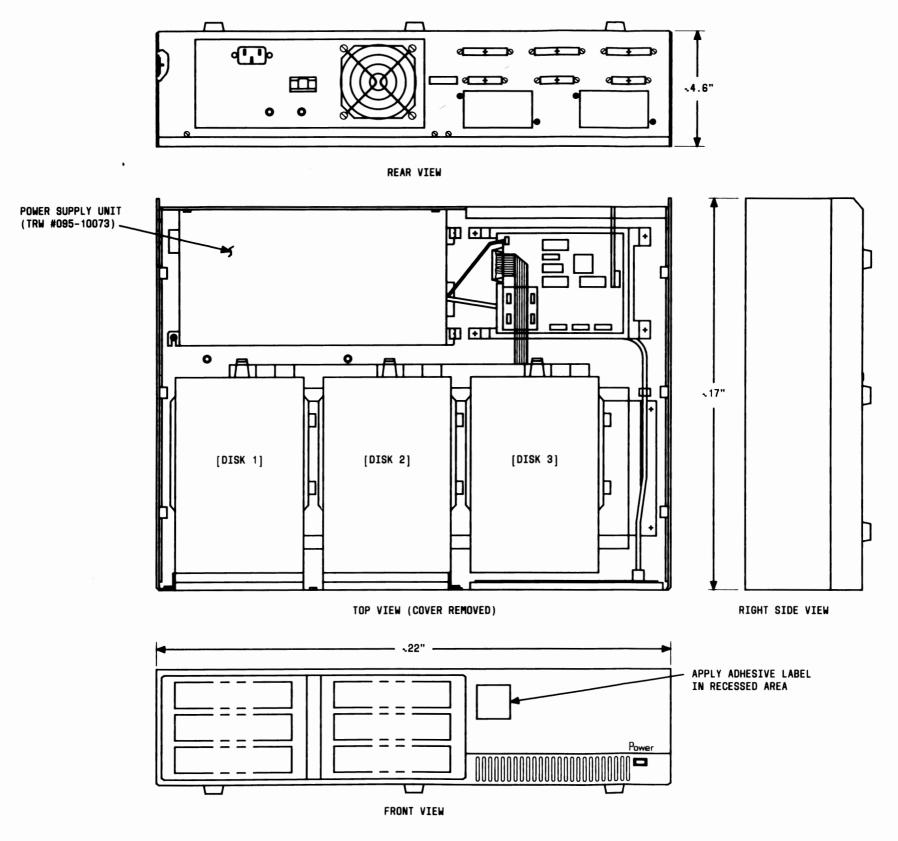

| Figure 2-5:                  | Domestic 3B2/400 Computer Cabinet Assembly Drawing (ED-4C631-30)                                                                  | 2-31         |

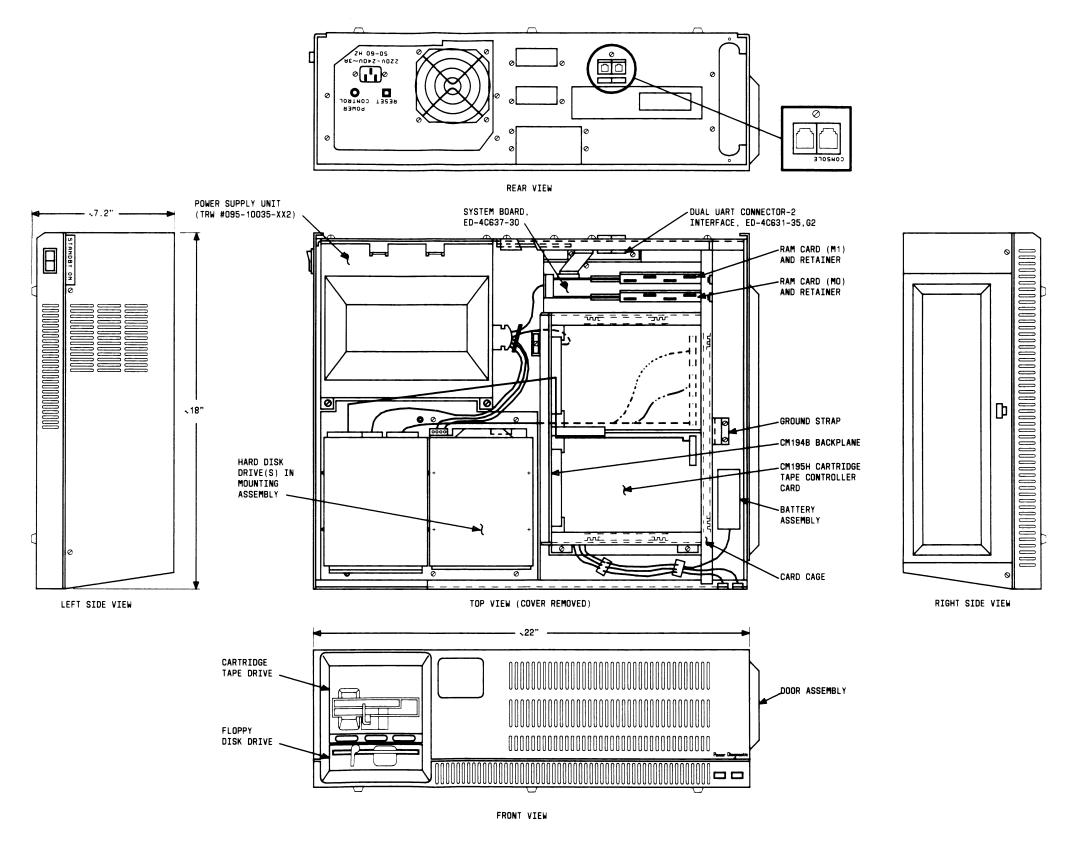

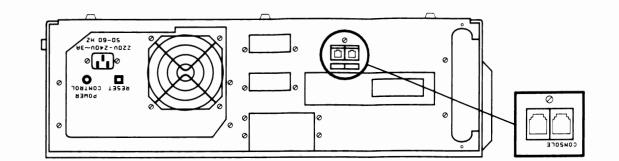

| Figure 2-6:                  | International 3B2/400 Computer Cabinet Assembly Drawing                                                                           | 0.05         |

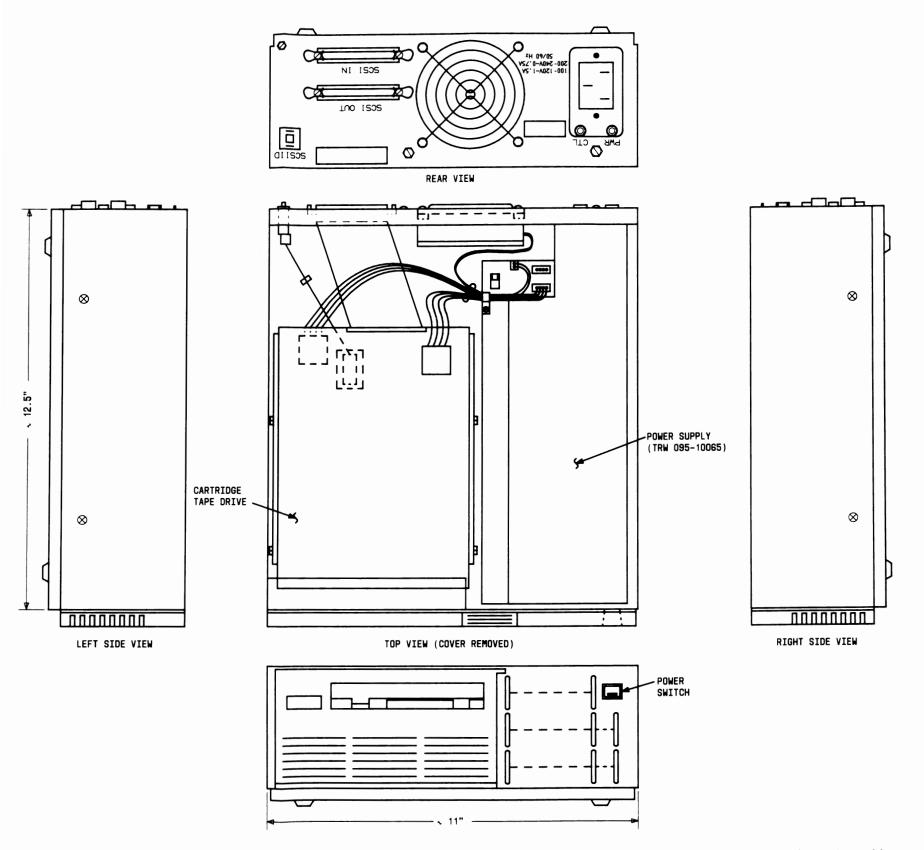

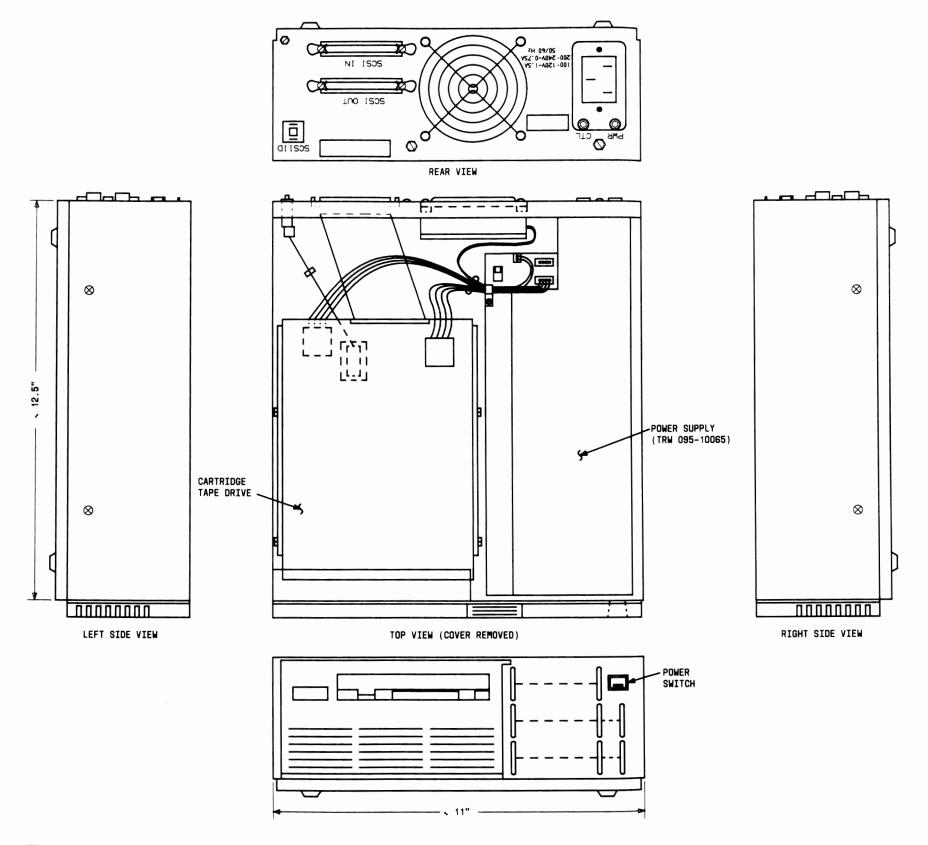

| Figure 2-7:                  | (ED-4C638-30)                                                                                                                     | 2-35<br>2-39 |

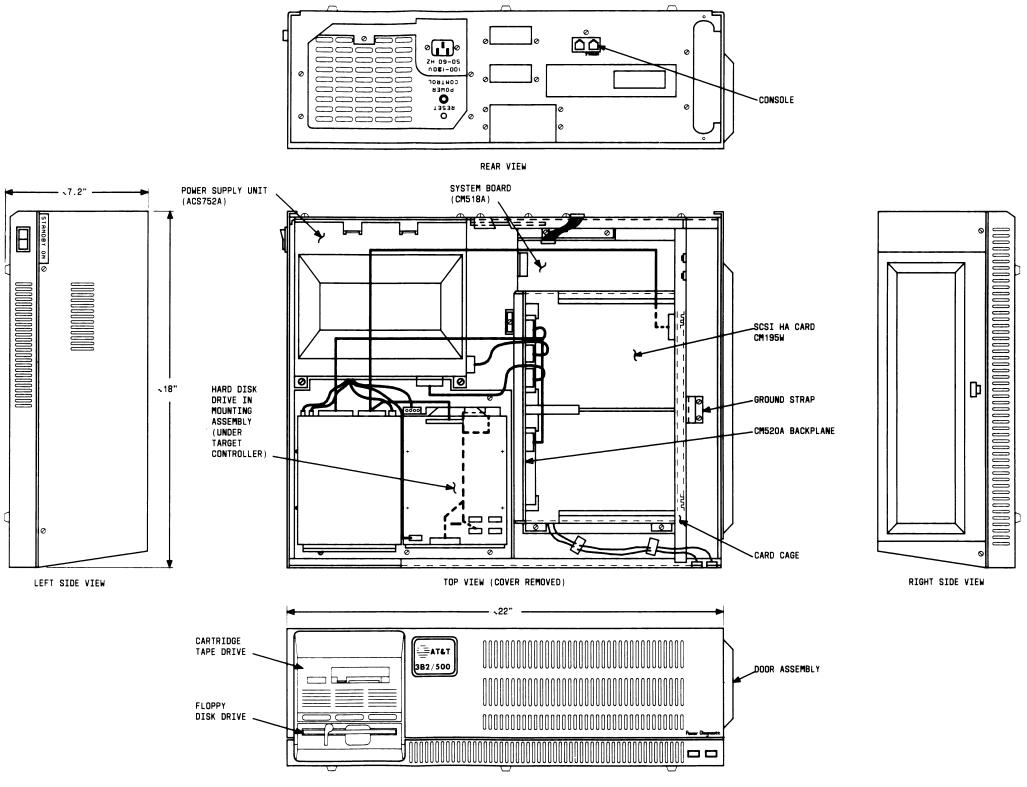

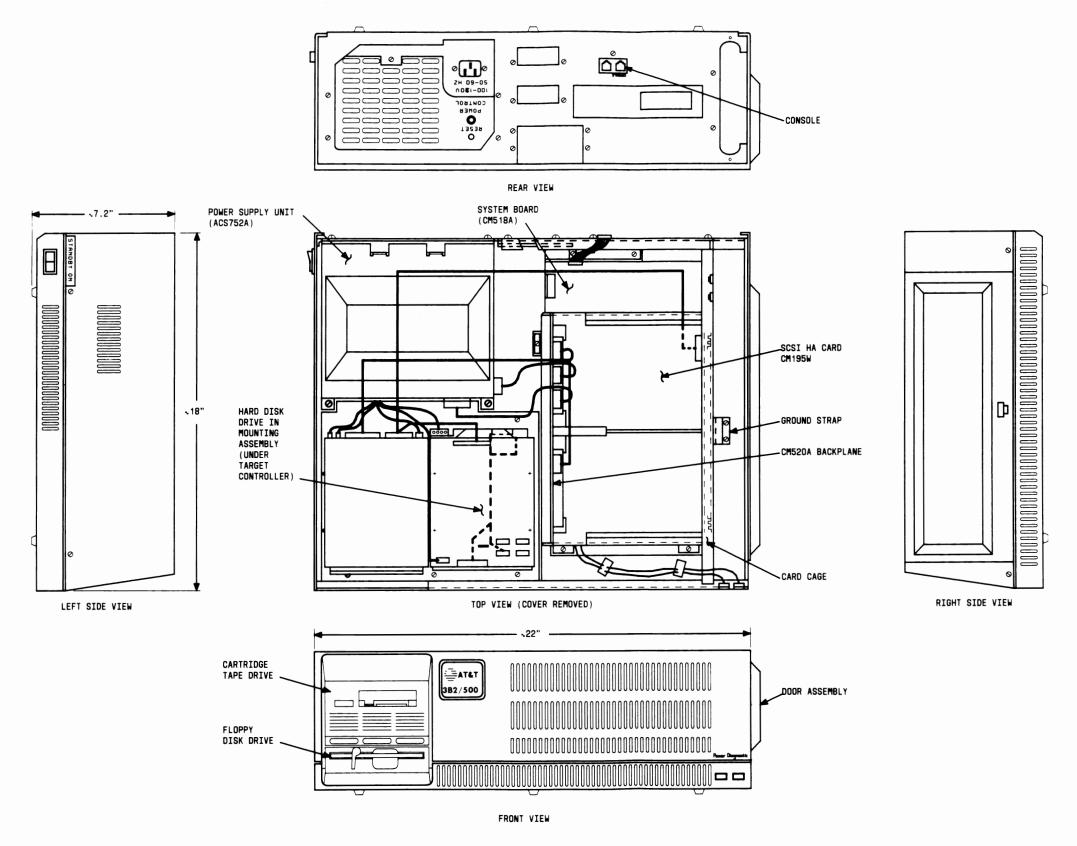

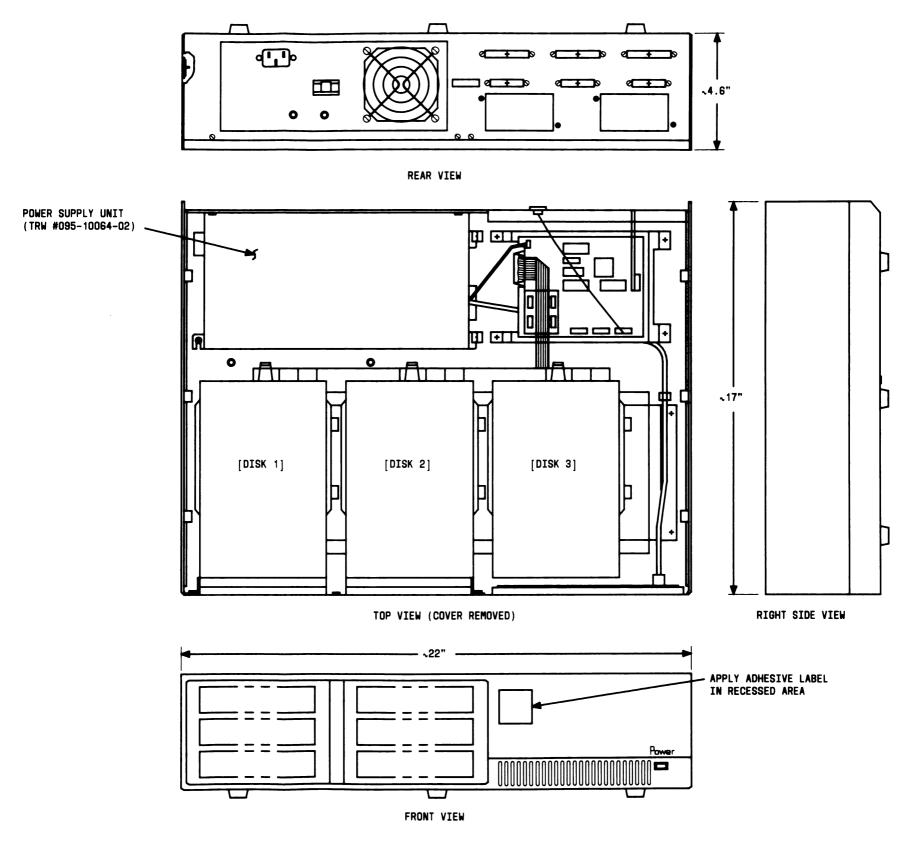

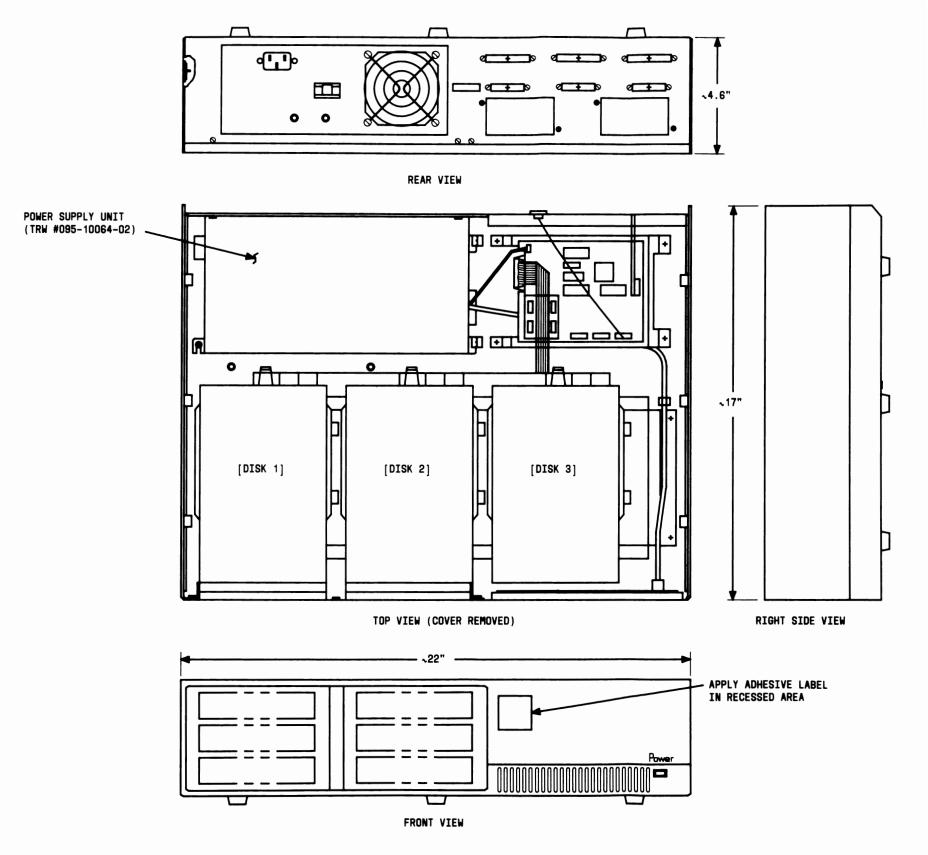

| Figure 2-7:                  | 3B2/600 Computer Cabinet Assembly Drawing (ED-3T043-30)                                                                           | 2-39         |

| Figure 2-9:                  | 3B2/700 Computer Cabinet Assembly Drawing (ED-3T047-30)                                                                           | 2-43<br>2-47 |

| Figure 2-10:                 | 3B2/1000 Computer Cabinet Assembly Drawing (ED-3T057-30)                                                                          | 2-47         |

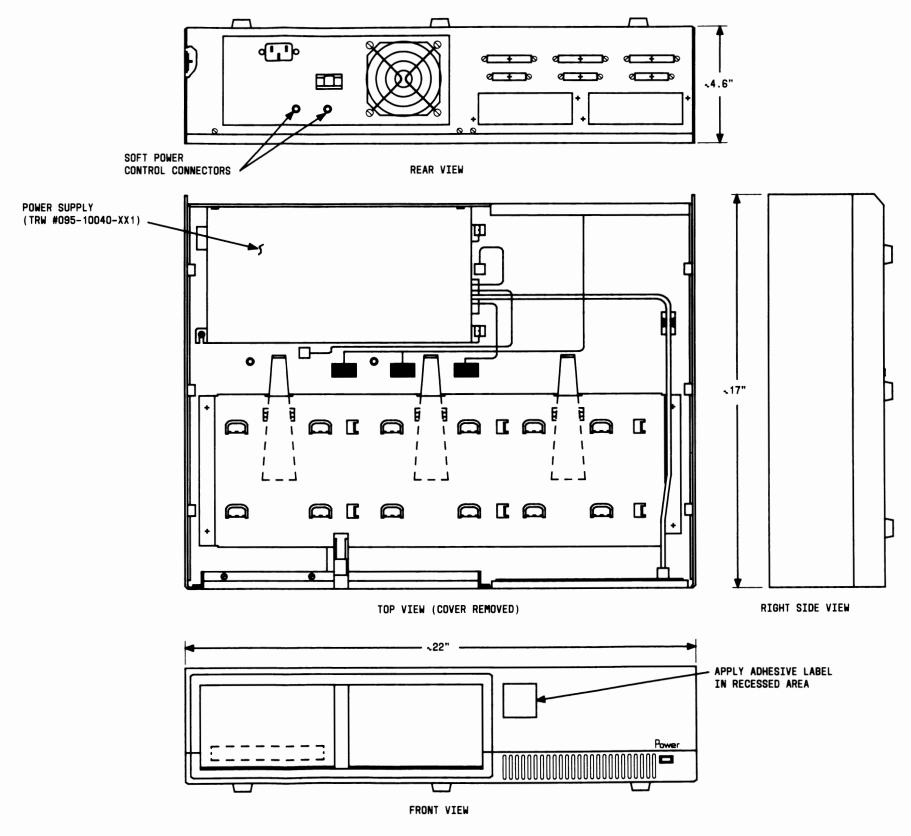

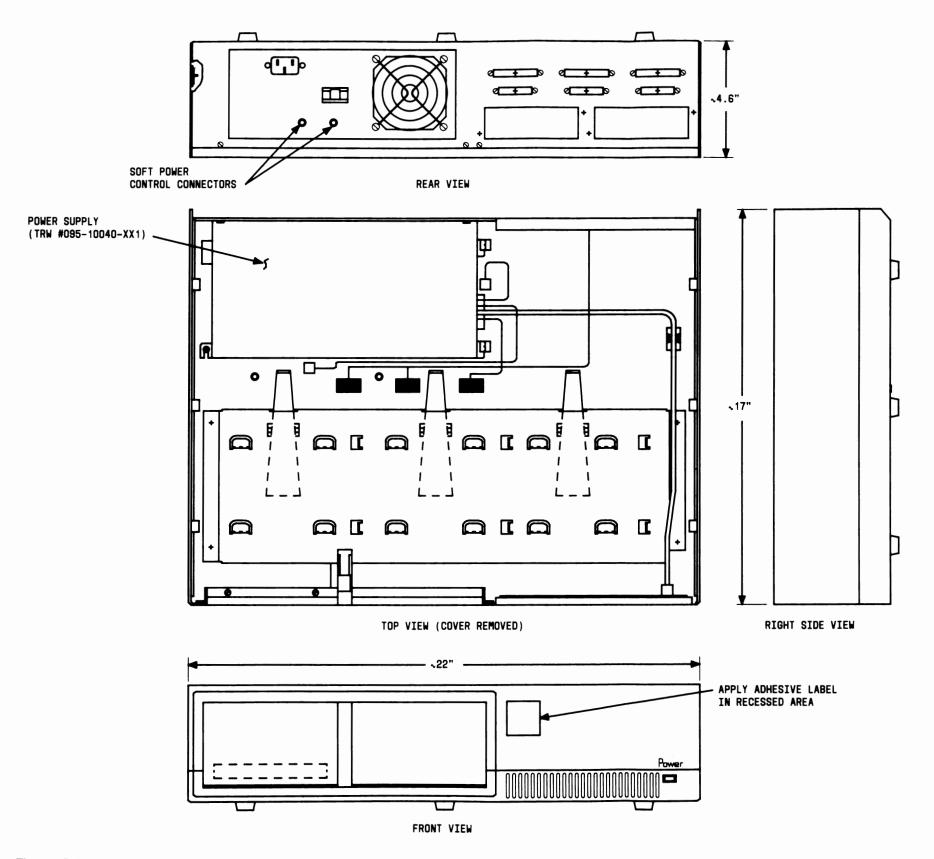

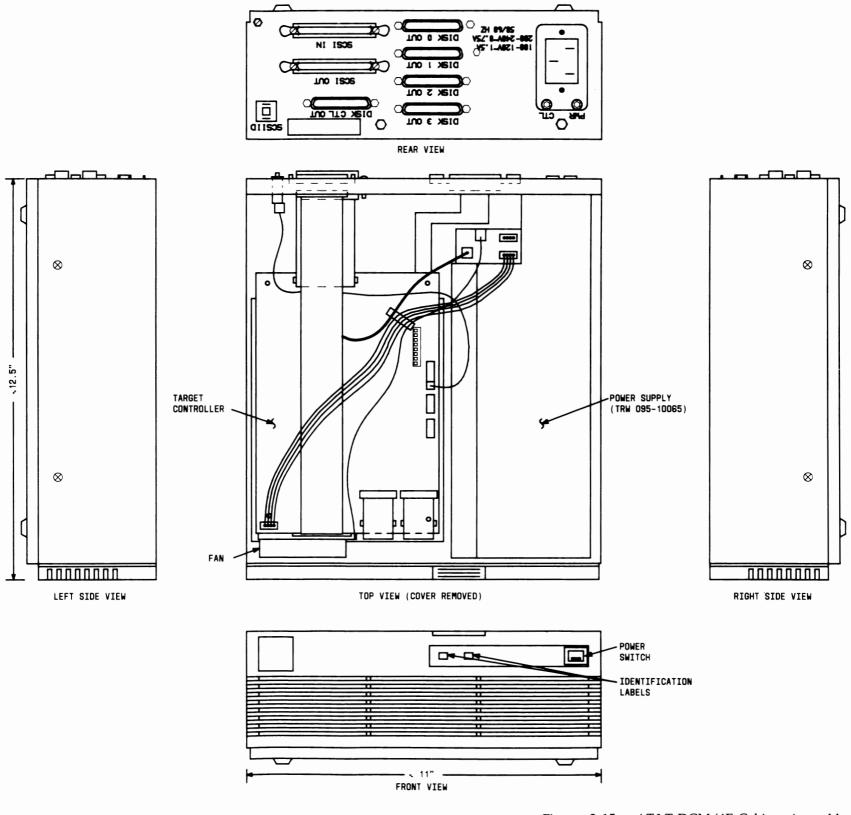

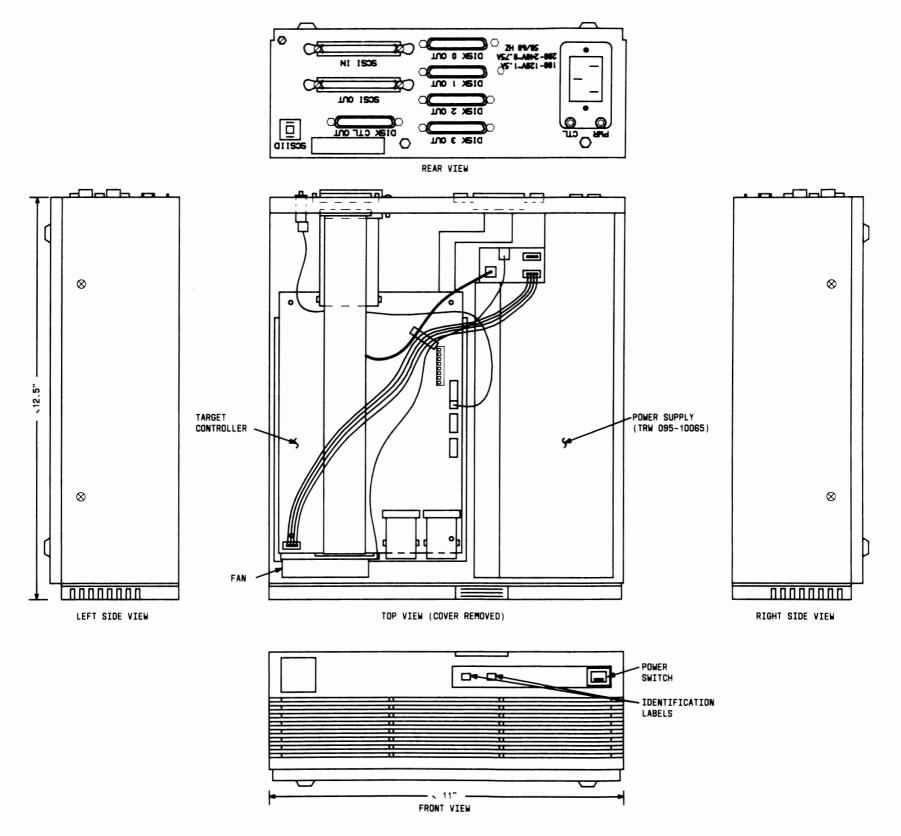

| Figure 2-11:                 | Domestic AT&T/XM Cabinet Assembly Drawing (ED-4C580-30)                                                                           | 2-51         |

| Figure 2-12:                 | International AT&T/XM Cabinet Assembly Drawing (ED-4C635-30)                                                                      | 2-59         |

| Figure 2-13:                 | Domestic AT&T XM/405S/900S Cabinet Assembly Drawing                                                                               | 2 07         |

|                              | (ED-3T010-30)                                                                                                                     | 2-63         |

| Figure 2-14:                 | International AT&T XM/405S/900S Cabinet Assembly Drawing                                                                          | - 00         |

| 0                            | (ED-3T027-30)                                                                                                                     | 2-67         |

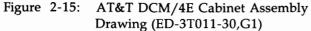

| Figure 2-15:                 | AT&T DCM/4E Cabinet Assembly Drawing (ED-3T011-30,G1)                                                                             | 2-71         |

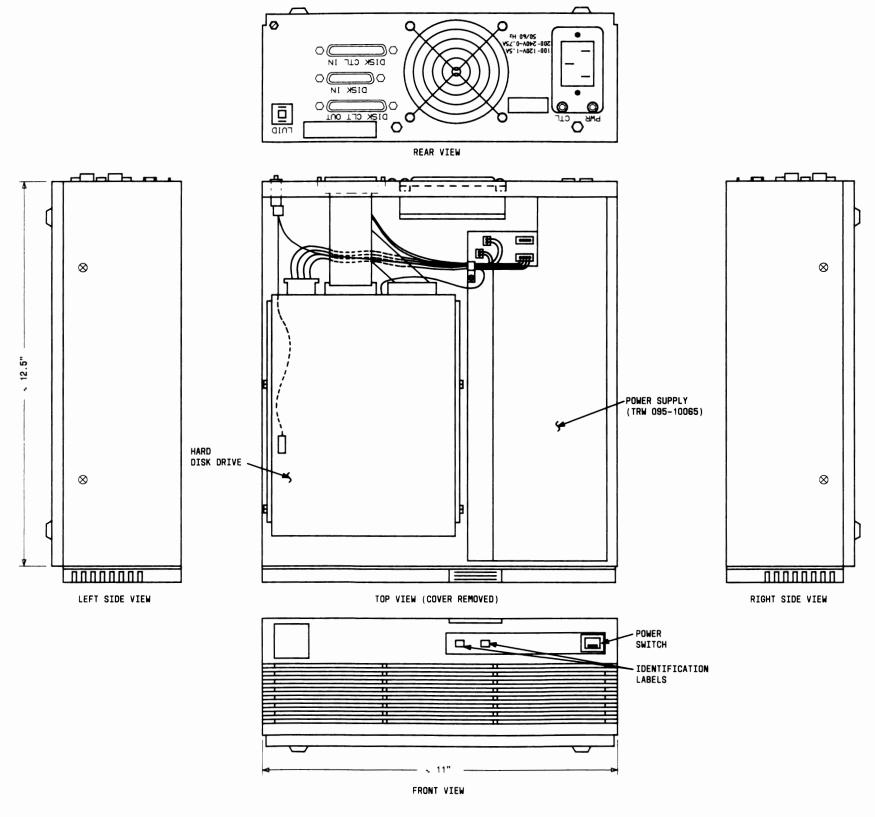

| Figure 2-16:                 | AT&T DM Cabinet Assembly Drawing (ED-3T011-30,G2, G3, G5, G6)                                                                     | 2-75         |

| Figure 2-17:                 | AT&T DM/S or DM/DS Cabinet Assembly Drawing (ED-3T011-30,G8, G9,                                                                  |              |

| 0                            | G11)                                                                                                                              | 2-79         |

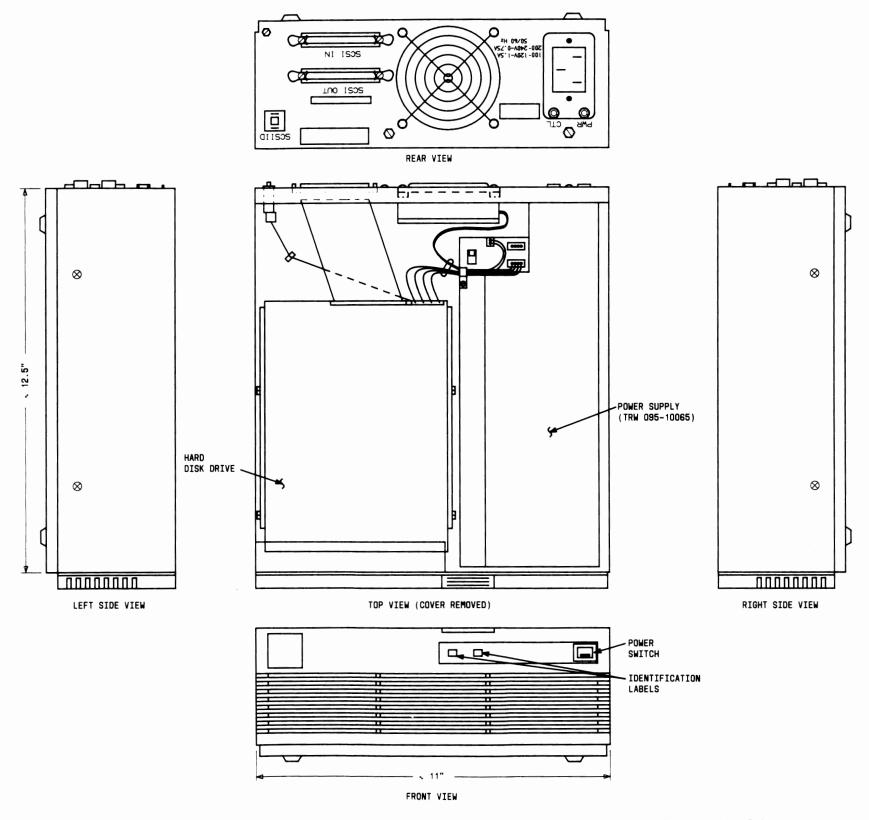

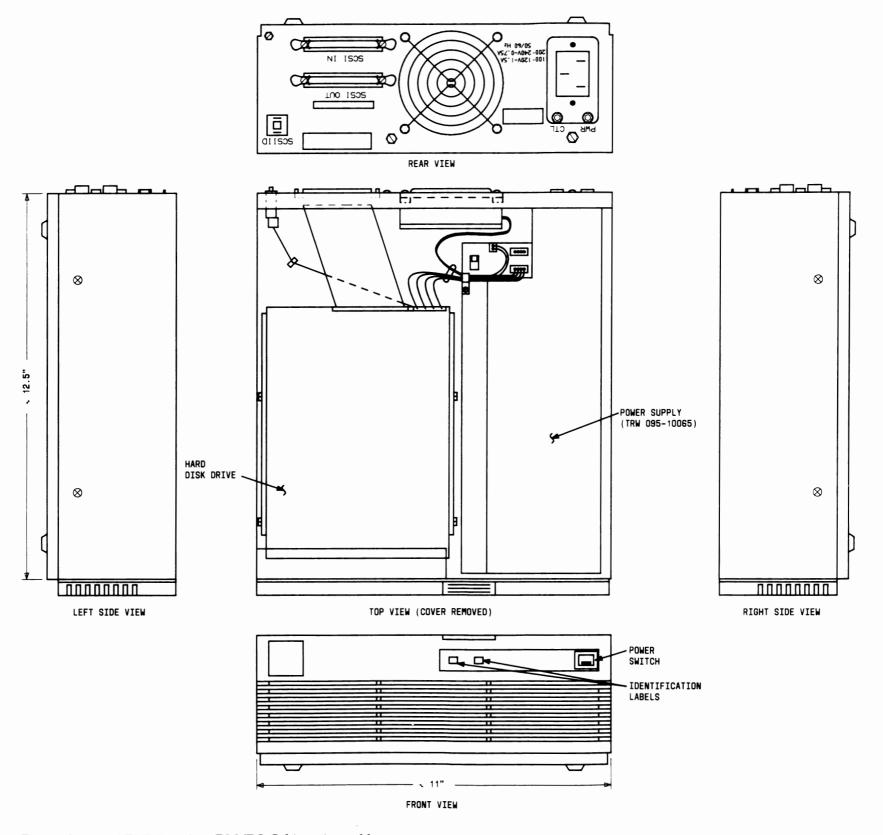

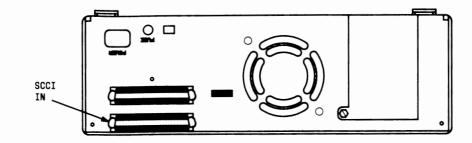

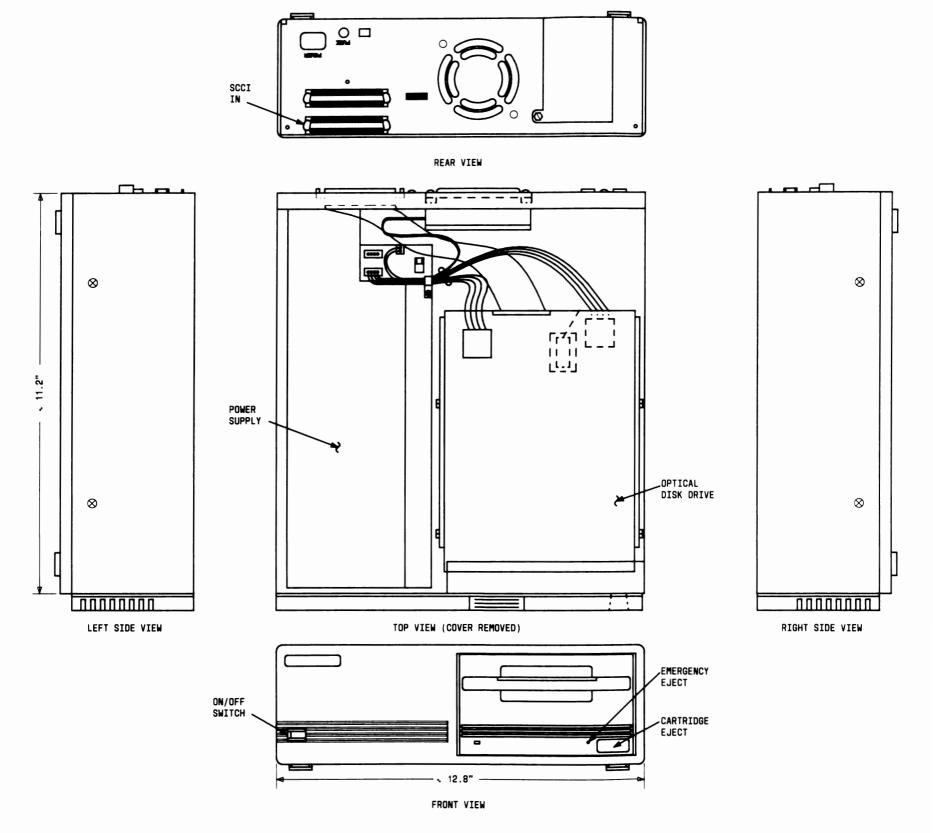

| Figure 2-18:                 | AT&T SCSI Rewritable Optical Disk Cabinet Assembly Drawing                                                                        | 2-83         |

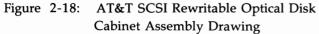

| Figure 2-19:                 | SCSI Manual-Loading 9-Track Tape Cabinet                                                                                          | 2-87         |

| Figure 2-20:                 | SCSI Autoloading 9-Track Tape Cabinet                                                                                             | 2-88         |

| Figure 2-21:                 | AT&T SCSI TM Cabinet Assembly Drawing (ED-3T011-30,G4, G7)                                                                        | 2-91         |

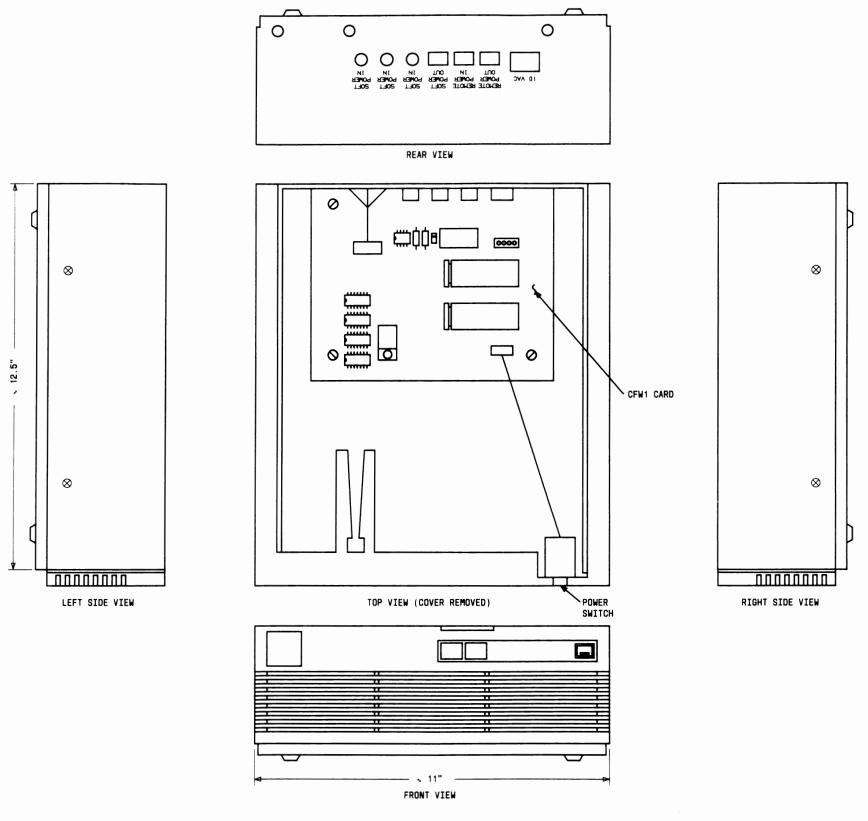

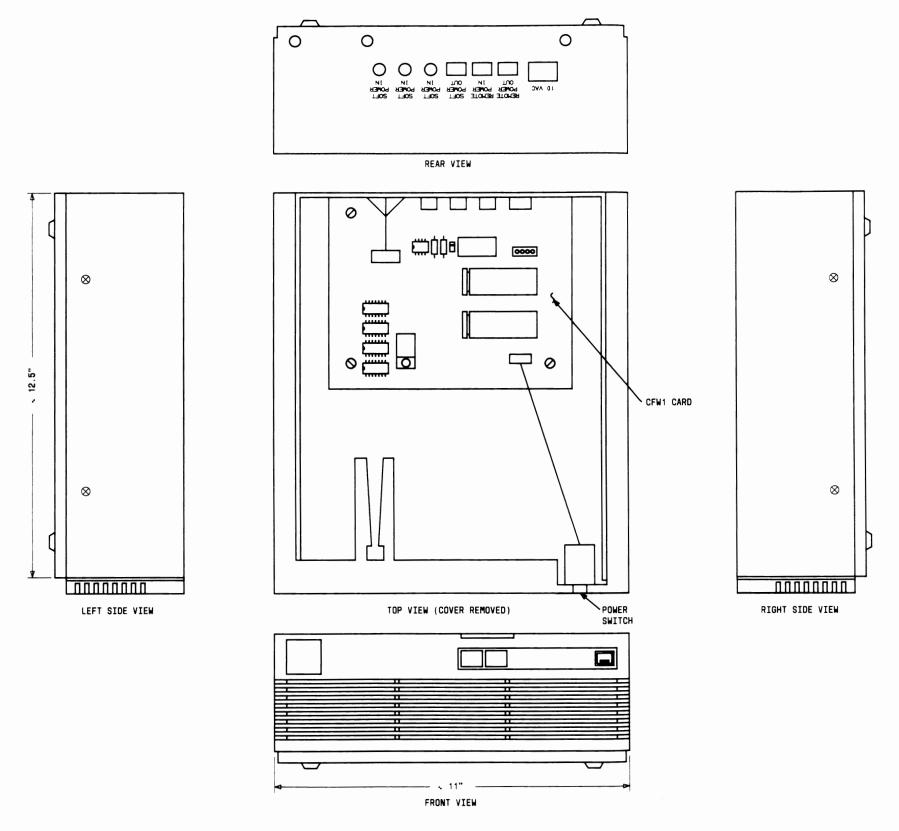

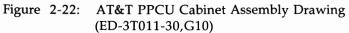

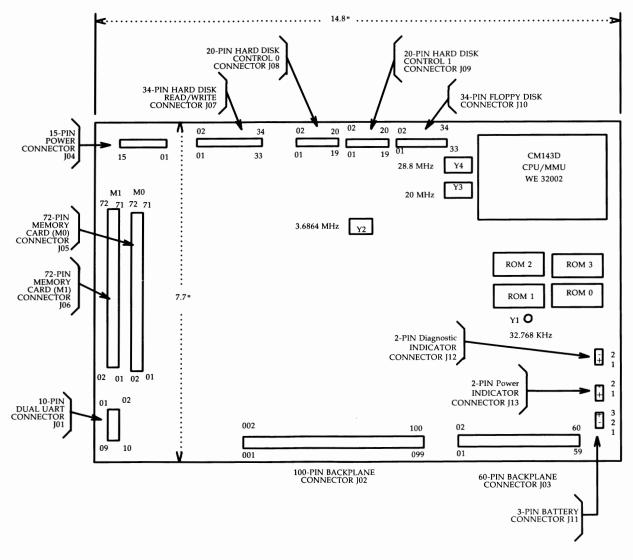

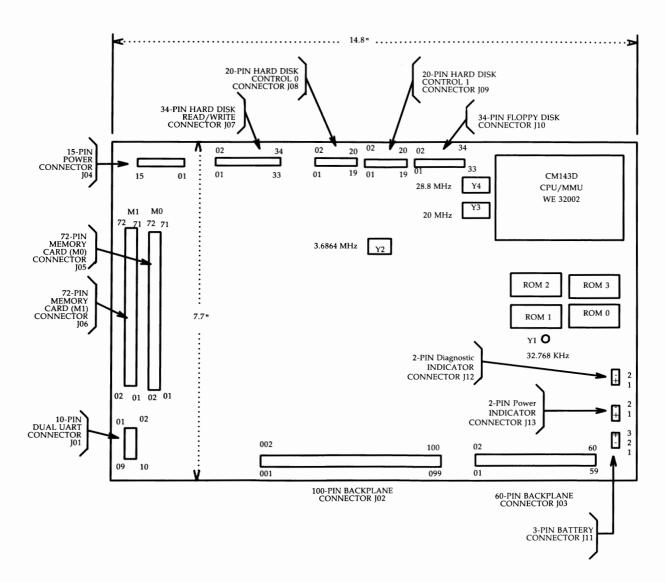

| Figure 2-22:                 | AT&T PPCU Cabinet Assembly Drawing (ED-3T011-30,G10)                                                                              | 2-97         |

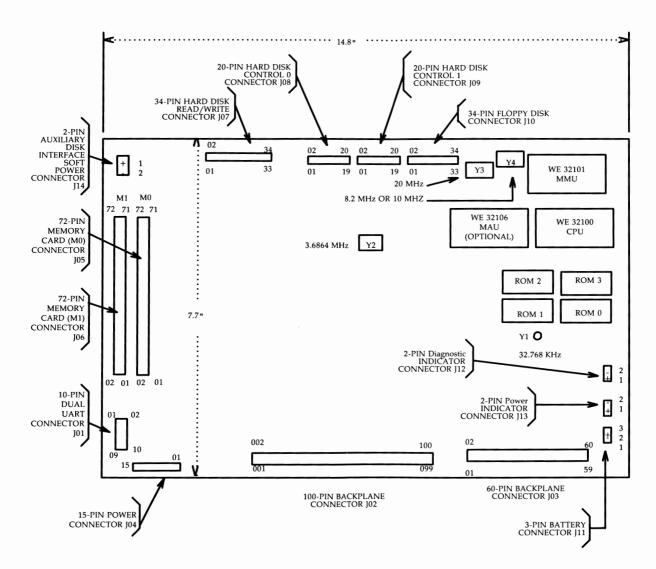

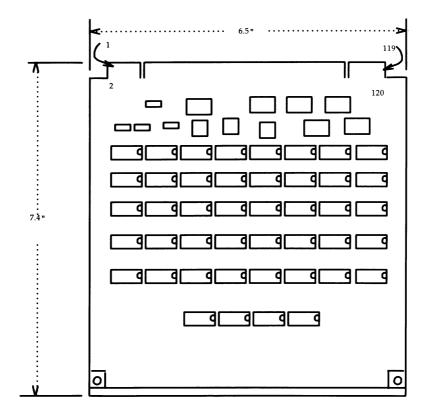

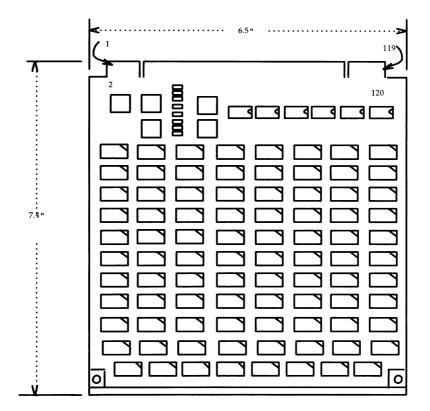

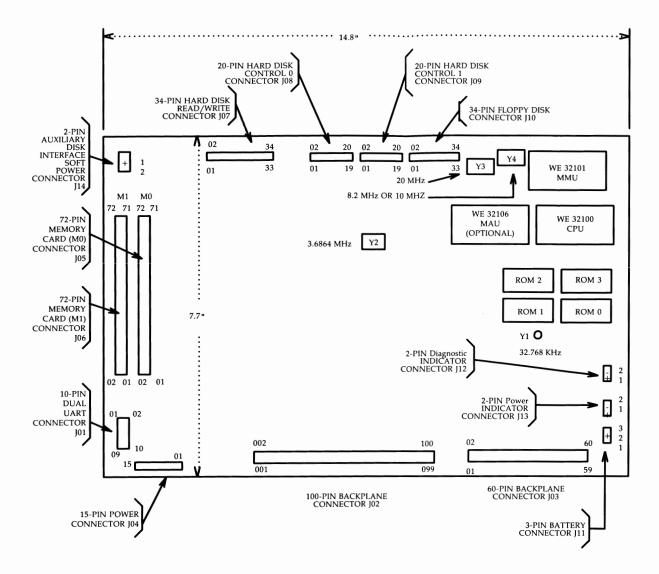

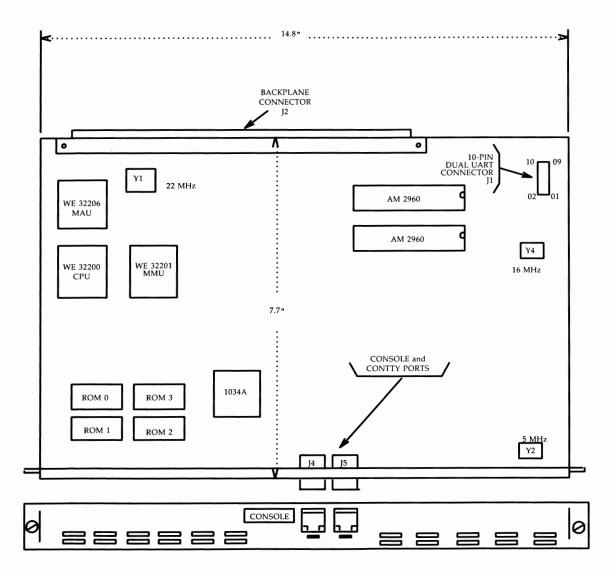

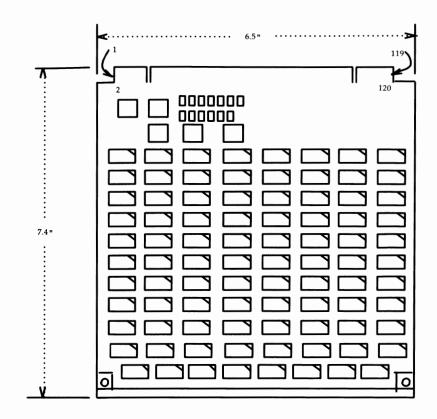

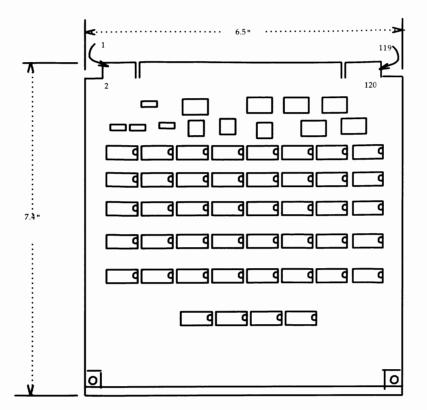

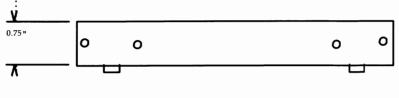

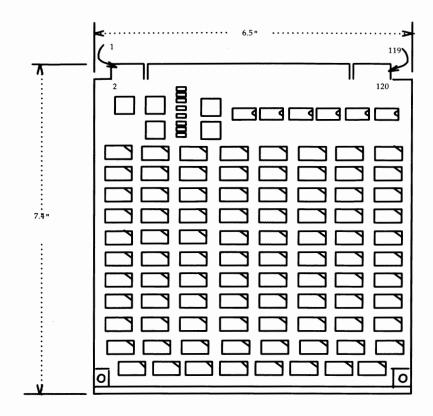

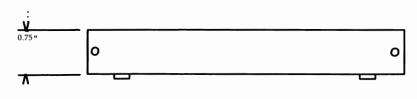

| Figure 2-23:                 | CM190A System Board Layout (Discontinued Availability)                                                                            | 2-101        |

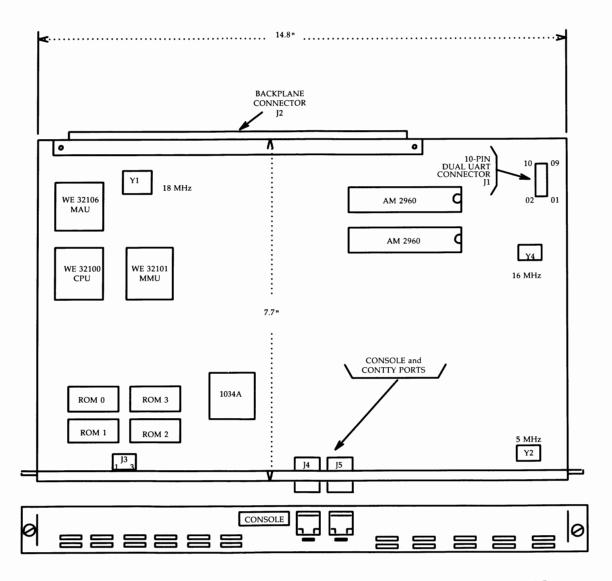

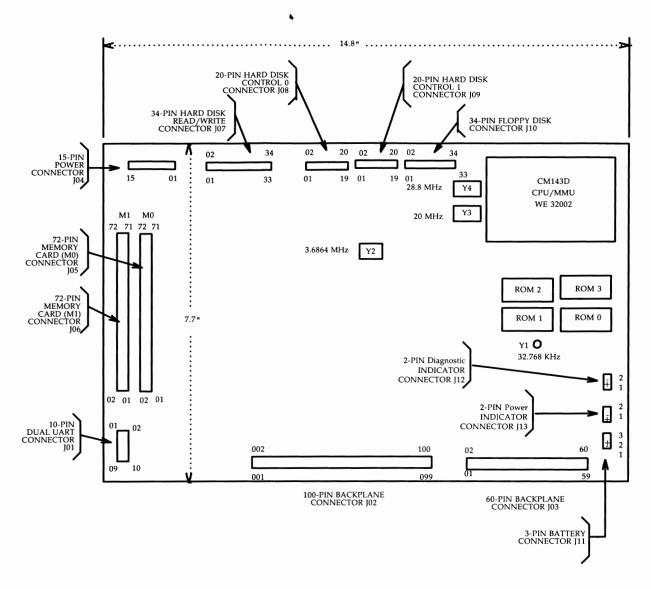

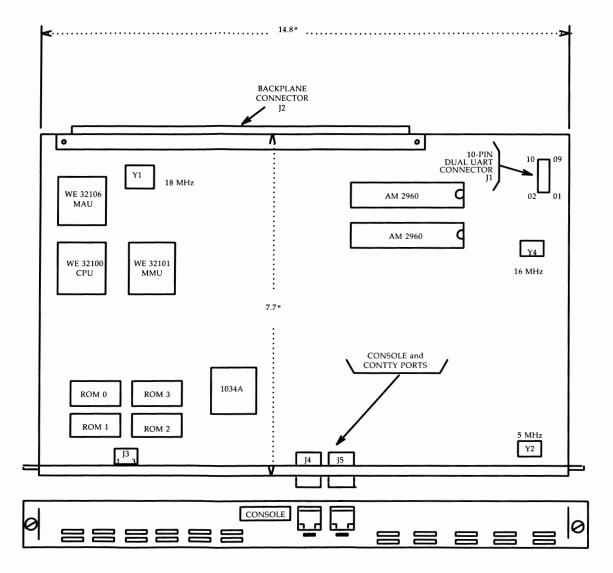

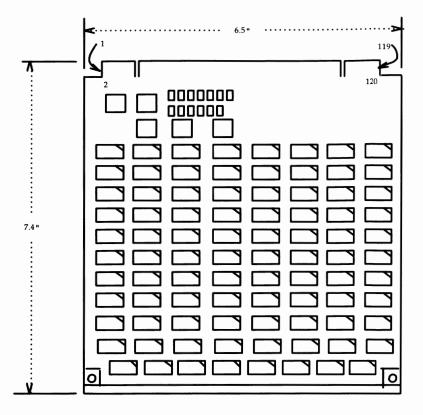

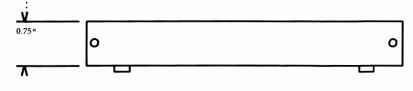

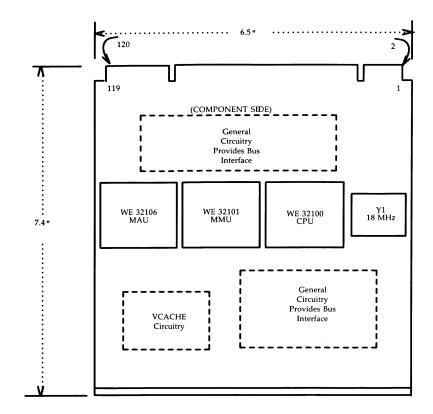

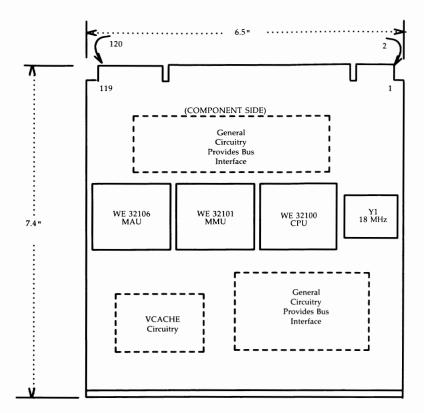

| Figure 2-24:                 | System Board, ED-4C637-30 Layout                                                                                                  | 2-105        |

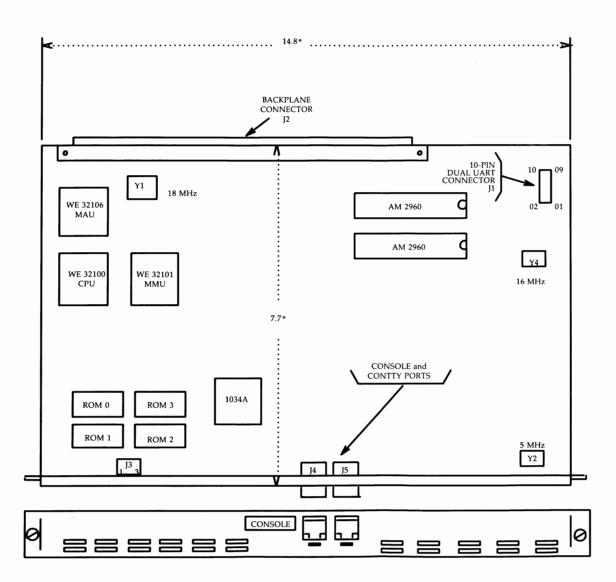

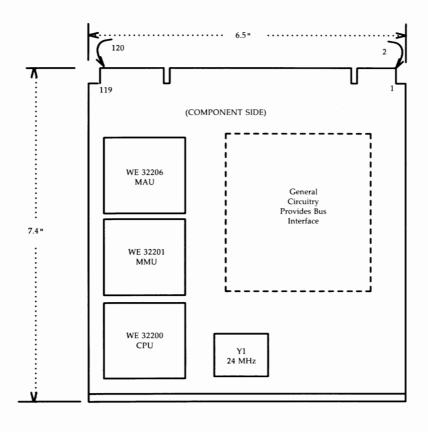

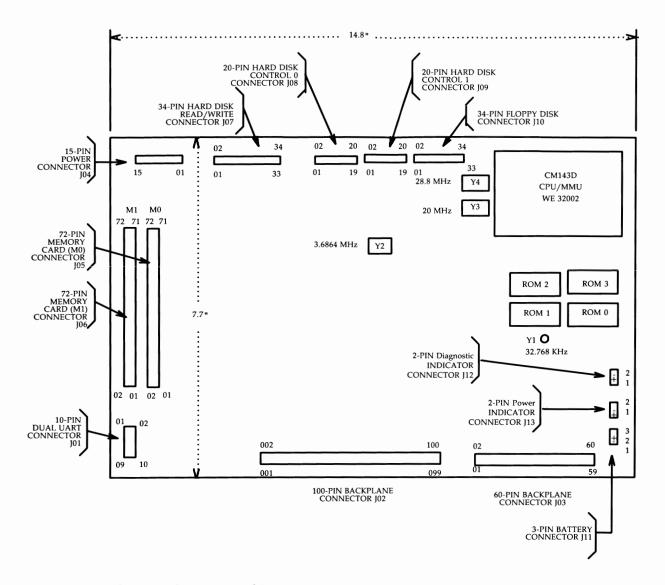

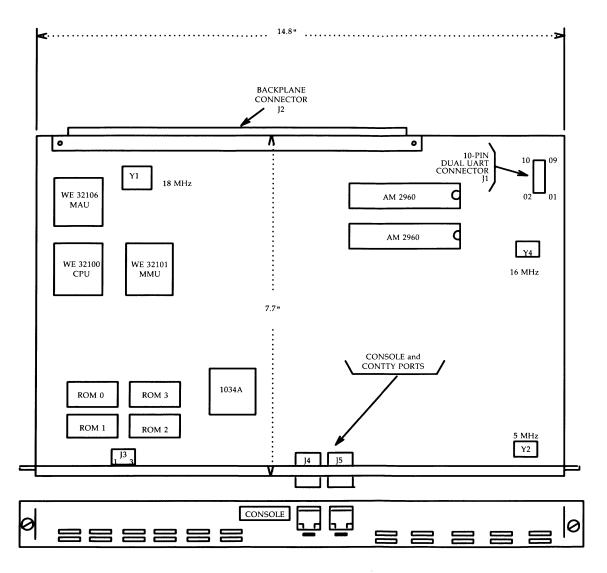

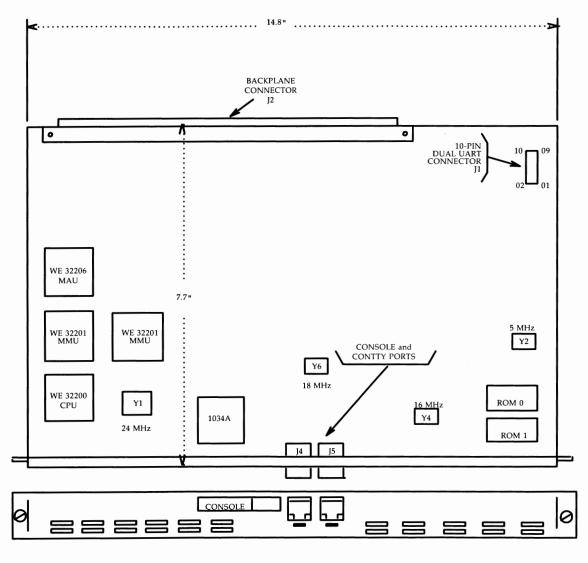

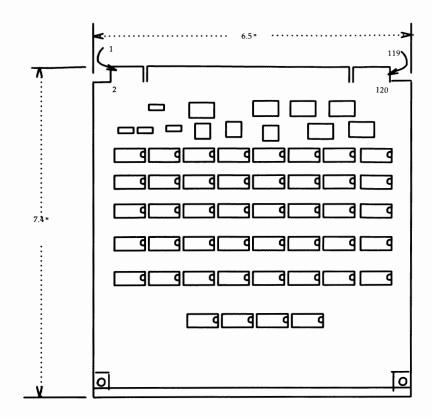

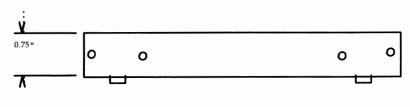

| Figure 2-25:                 | CM518A System Board Layout                                                                                                        | 2-109        |

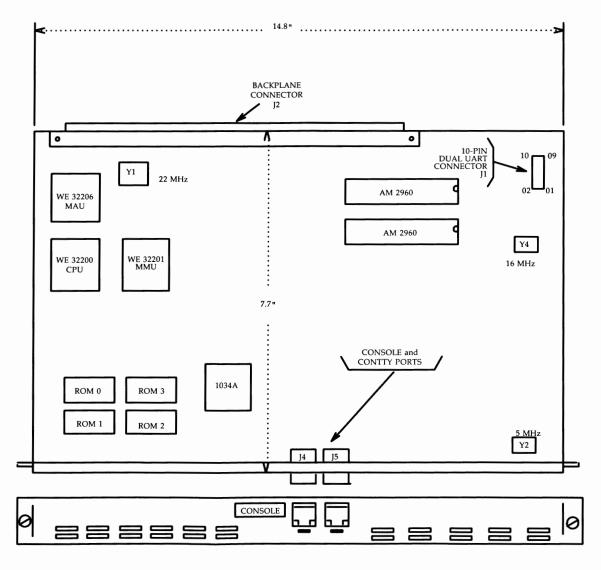

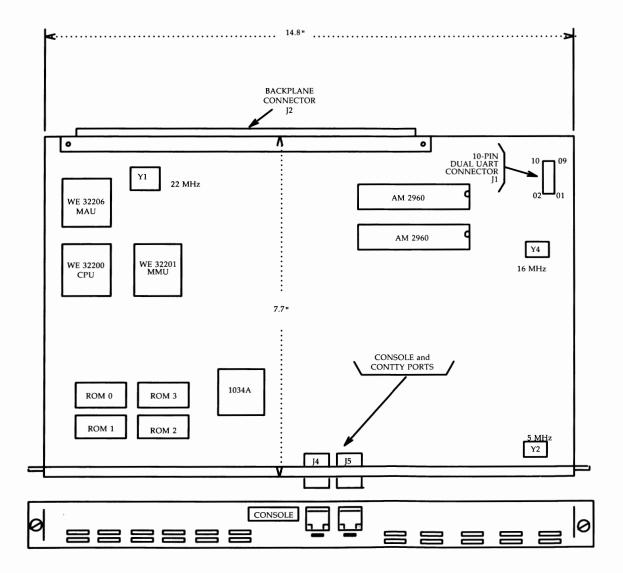

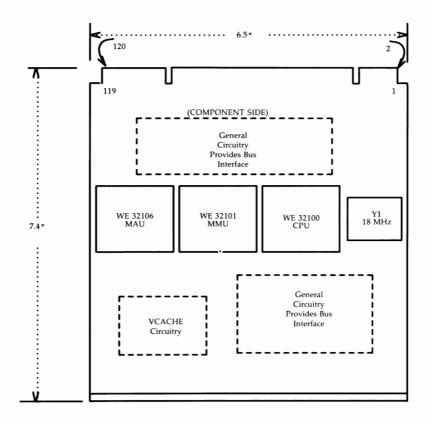

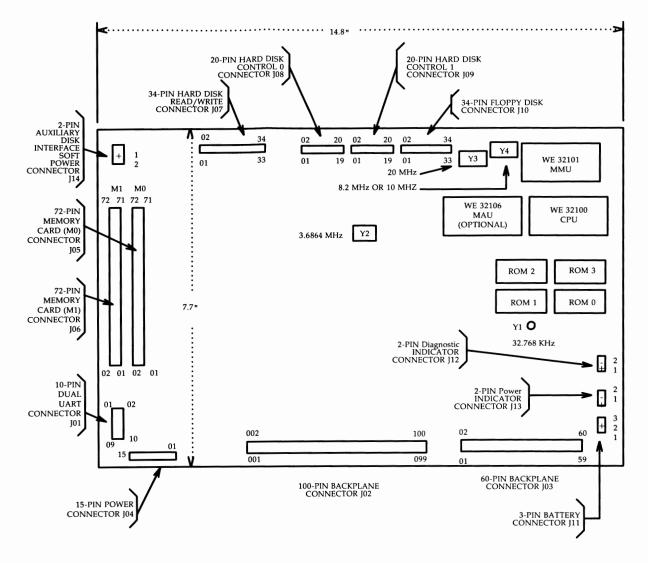

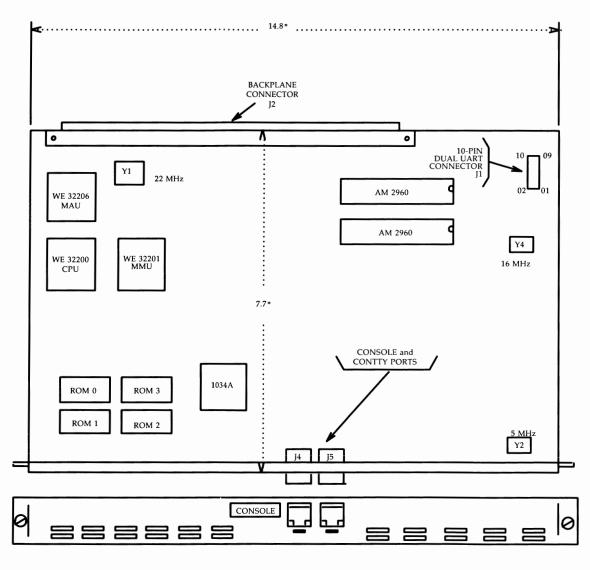

| Figure 2-26:                 | CM518B System Board Layout                                                                                                        | 2-113        |

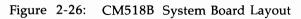

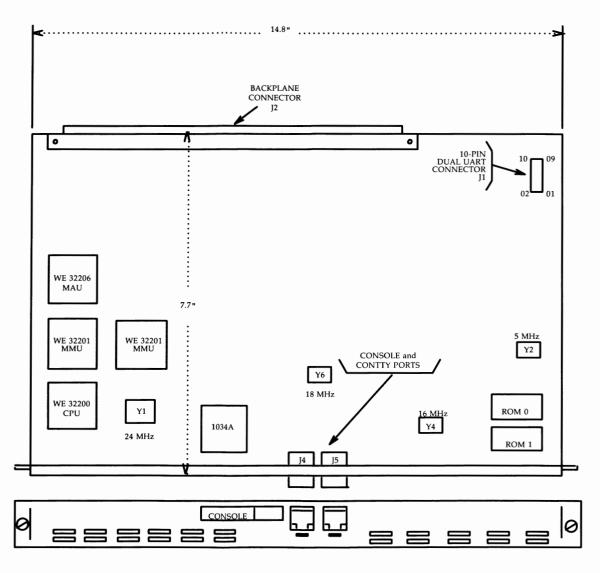

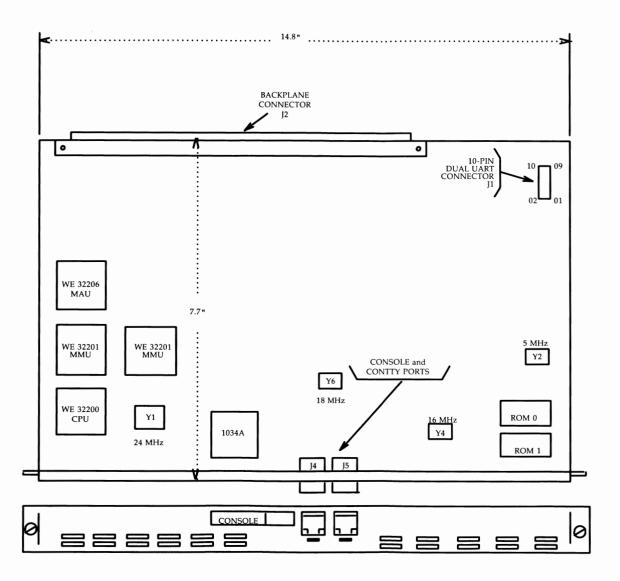

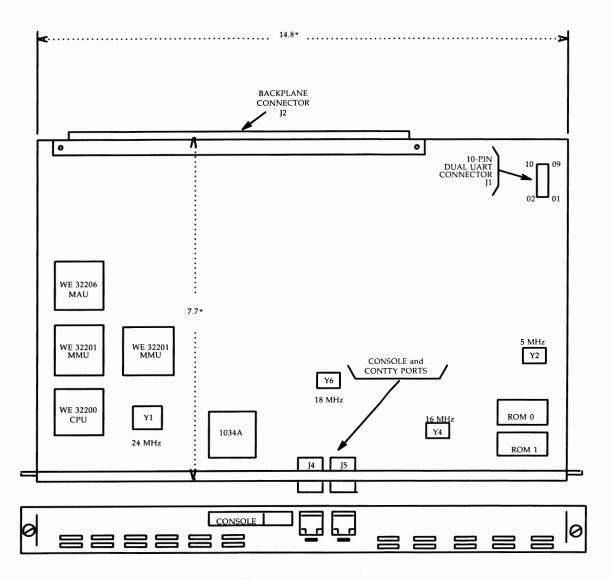

| Figure 2-27:                 | CM518C System Board Layout                                                                                                        | 2-117        |

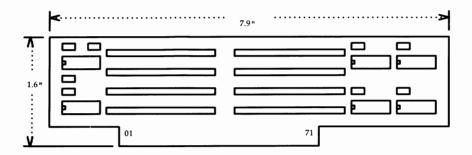

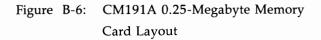

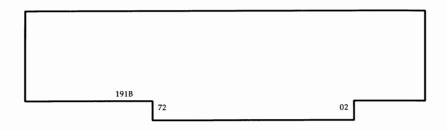

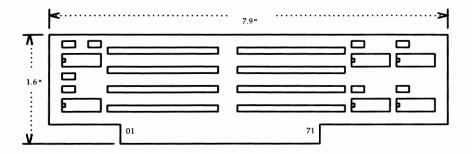

| Figure 2-28:                 | CM191A 0.25-Megabyte RAM Card Layout                                                                                              |              |

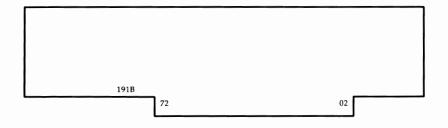

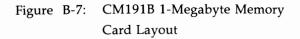

| Figure 2-29:                 | CM191B 1-Megabyte RAM Card Layout                                                                                                 | 2-122        |

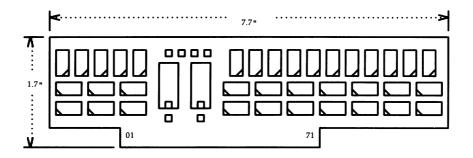

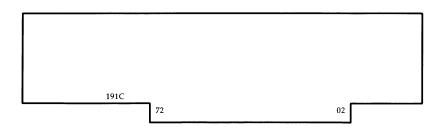

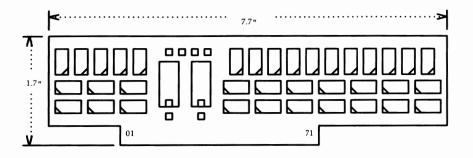

| Figure 2-30:                 | CM191C 1-Megabyte, Surface Mounted, RAM Card Layout                                                                               | 2-123        |

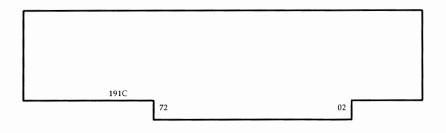

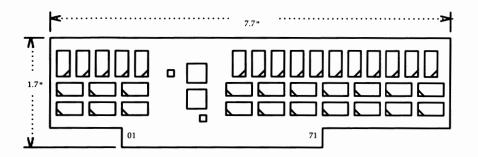

| Figure 2-31:                 | CM191D 2-Megabyte, Surface Mounted, RAM Card Layout                                                                               | 2-124        |

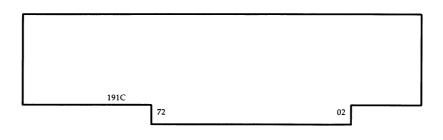

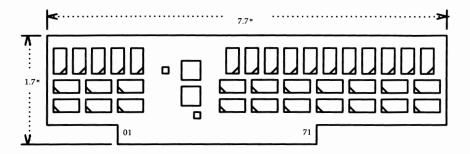

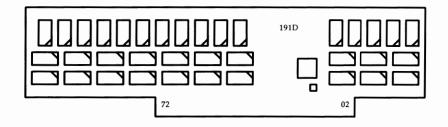

| Figure 2-32:                 | CM192B 2-Megabyte RAM Card Layout                                                                                                 | 2-125        |

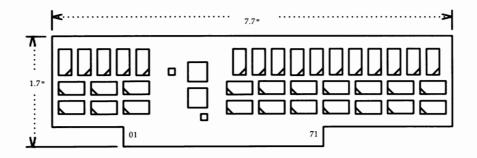

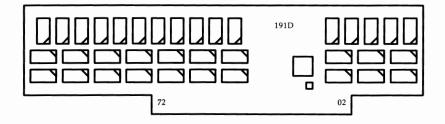

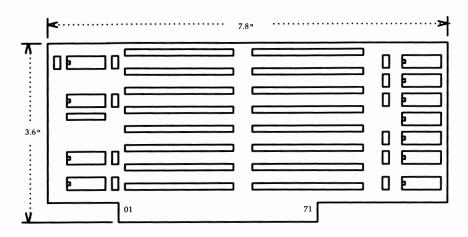

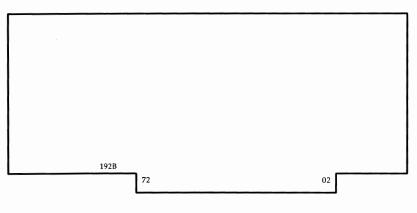

| Figure 2-33:                 | CM523A 4-Megabyte, Surface Mounted, RAM Card Layout                                                                               | 2-126        |

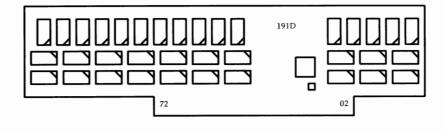

| Figure 2-34:                 | CM523AA 4-Megabyte, Surface Mounted, RAM Card Layout                                                                              | 2-127        |

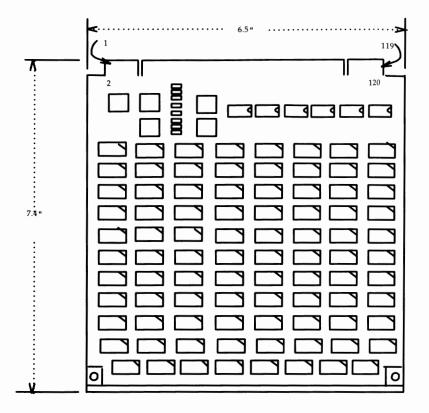

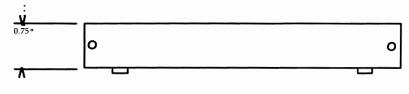

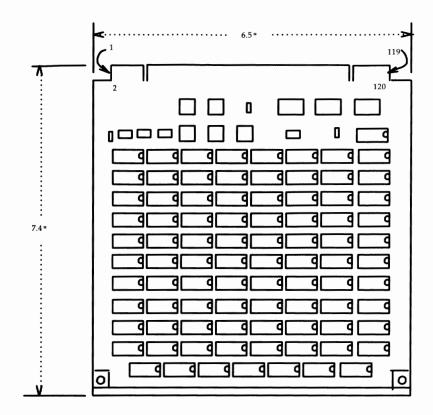

| Figure 2-35:                 | CM523B 2-Megabyte, Surface Mounted, RAM Card Layout                                                                               | 2-128        |

| Figure 2-36:                 | CM523D 16-Megabyte, Surface Mounted, RAM Card Layout                                                                              | 2-129        |

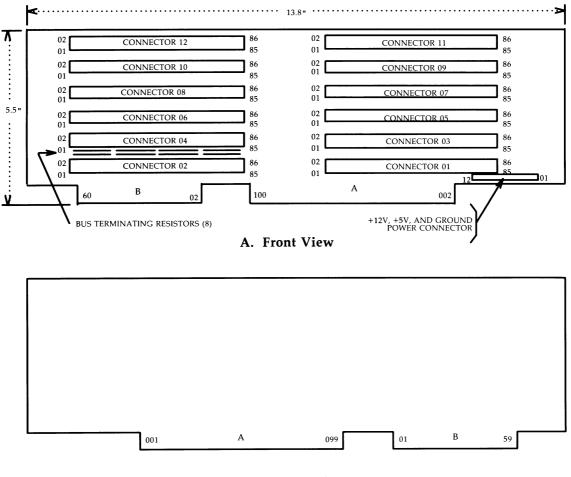

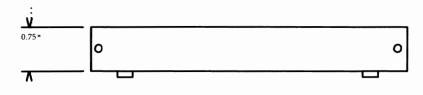

| Figure 2-37:                 | CM193A/B Backplane Board Layout                                                                                                   | 2-131        |

| Figure 2-38:<br>Figure 2-39: | CM194B Backplane Board Layout                                                                                                     | 2-132        |

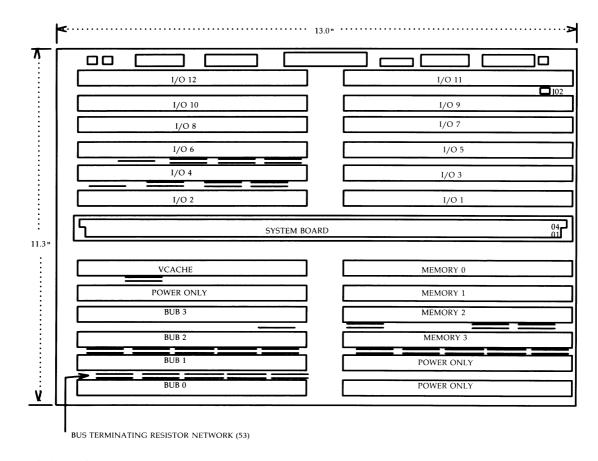

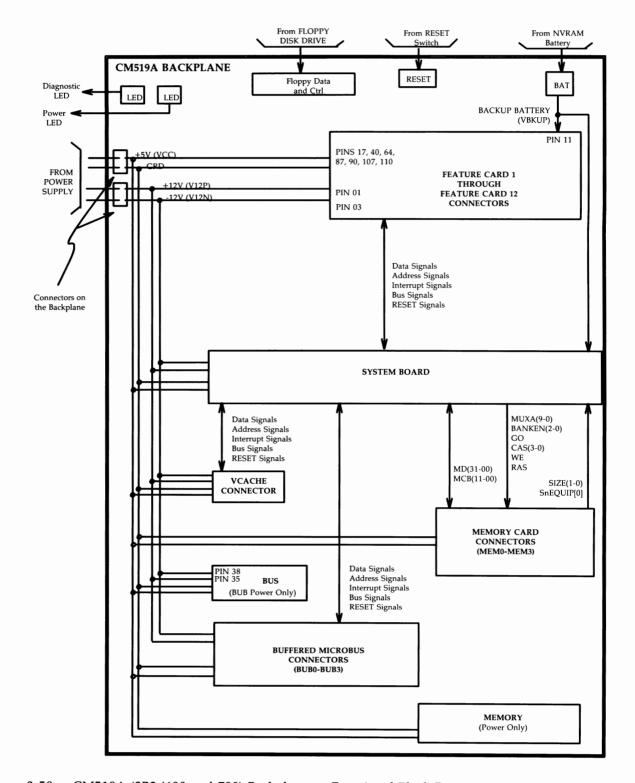

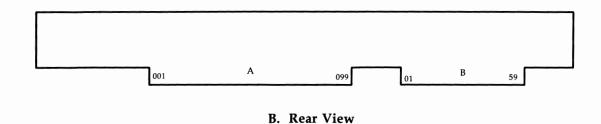

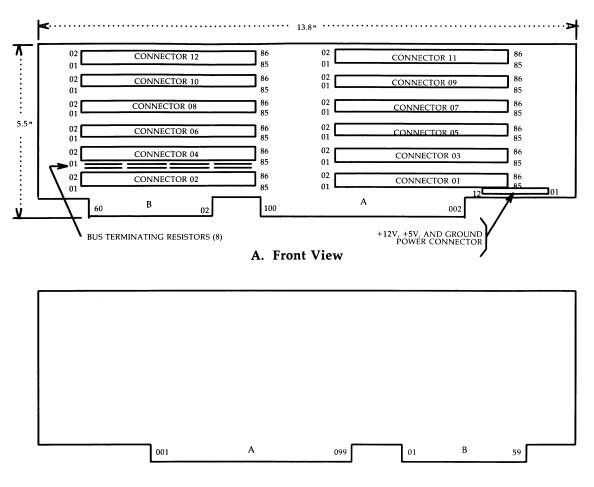

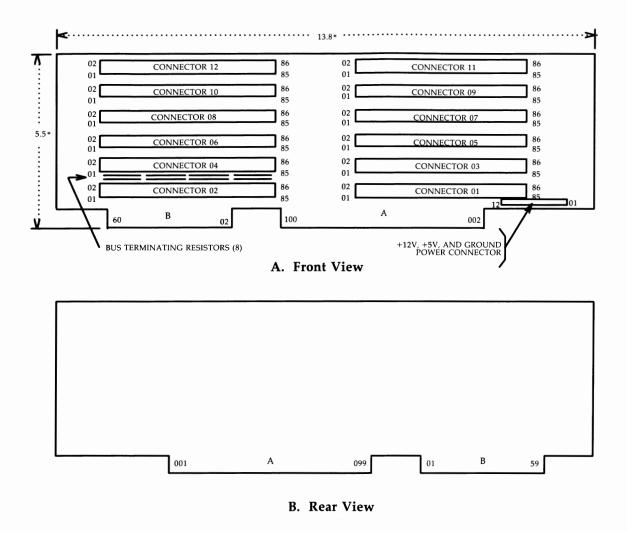

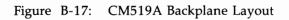

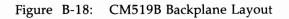

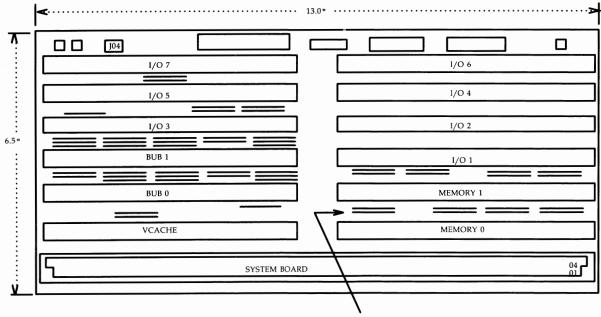

| Figure 2-39:                 | CM519A Backplane Board Layout                                                                                                     | 2-133        |

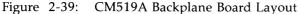

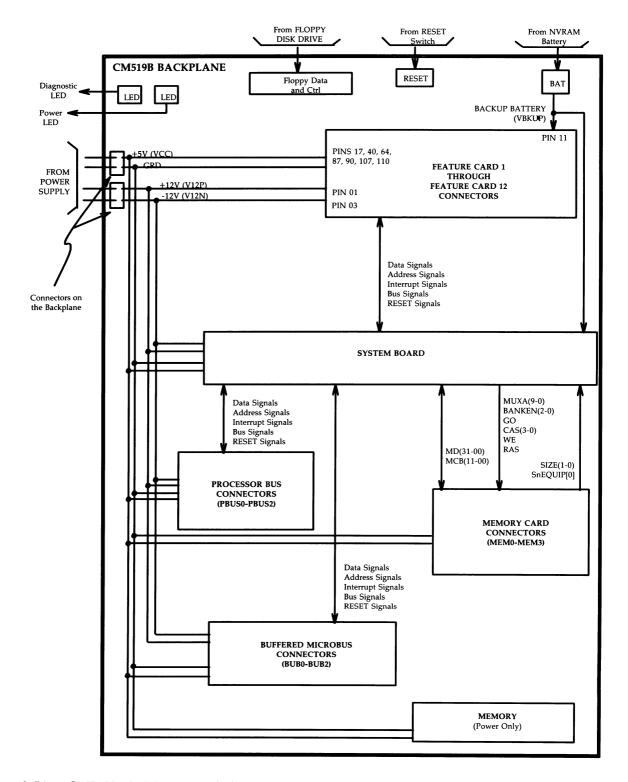

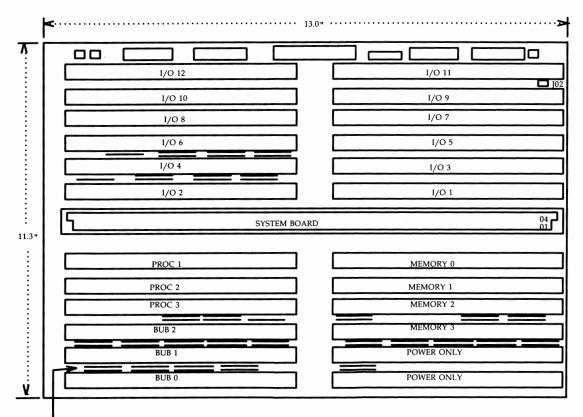

| Figure 2-40:<br>Figure 2-41: | CM519B Backplane Board Layout                                                                                                     | 2-134        |

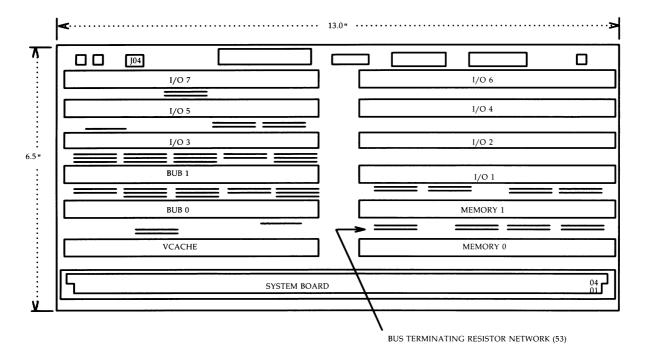

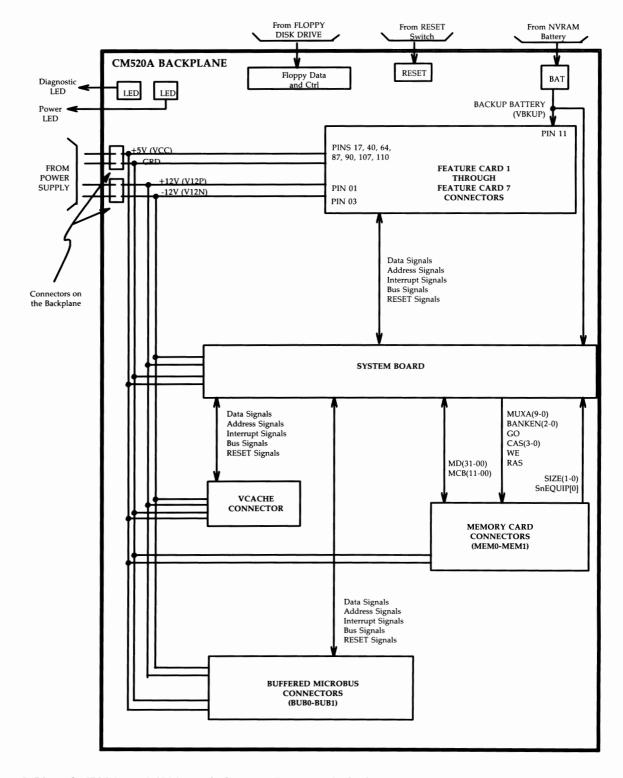

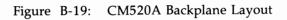

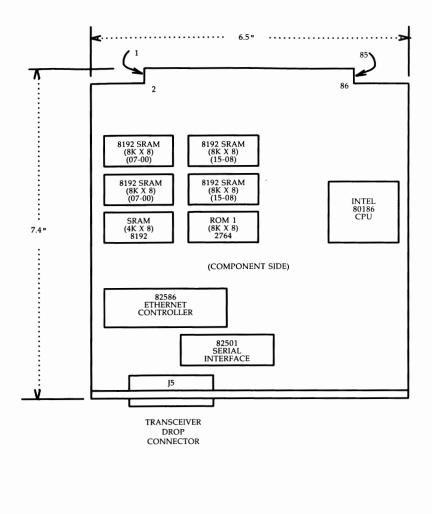

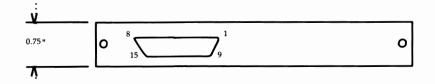

| Figure 2-41:<br>Figure 2-42: | CM520A Backplane Board Layout                                                                                                     | 2-135        |

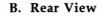

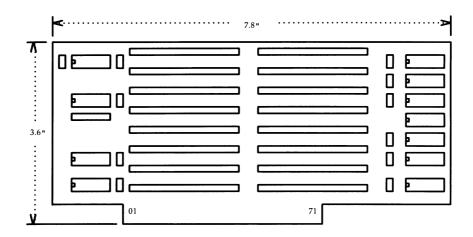

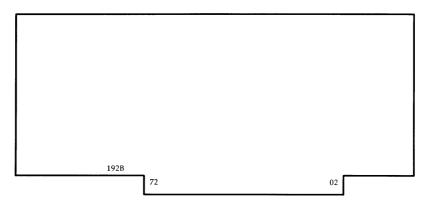

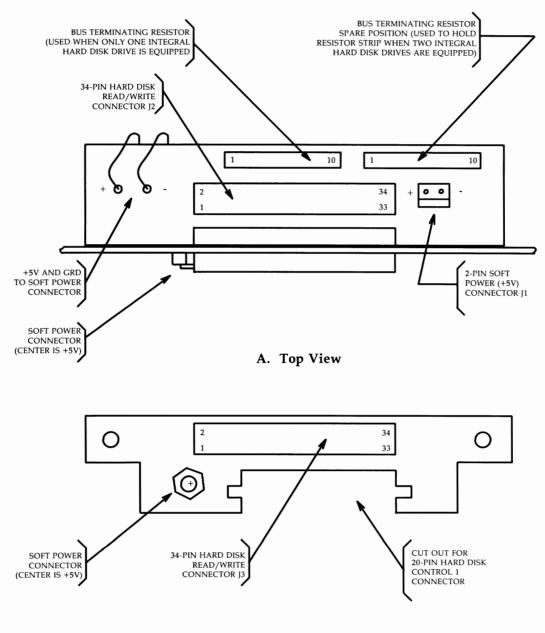

| Figure 2-42:<br>Figure 2-43: | Auxiliary Disk Interface, ED-4C632-30, Layout                                                                                     | 2-138        |

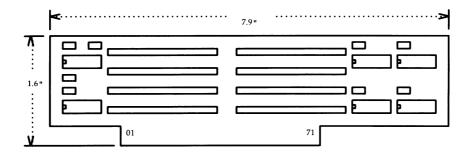

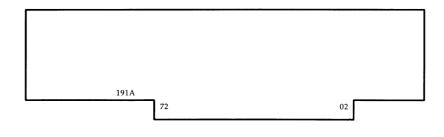

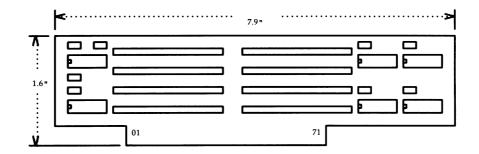

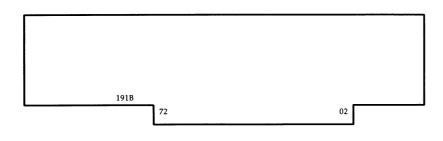

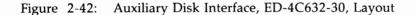

| inguie 2-45.                 | DUART Connector-2 Interface, ED-4C492-30,G5 (3B2/300/310) and ED-4C631-35 C2 (3B2/400) Lawout                                     | 0 1 4 0      |

| Figure 2-44:                 | ED-4C631-35,G2 (3B2/400) Layout                                                                                                   | 2-140        |

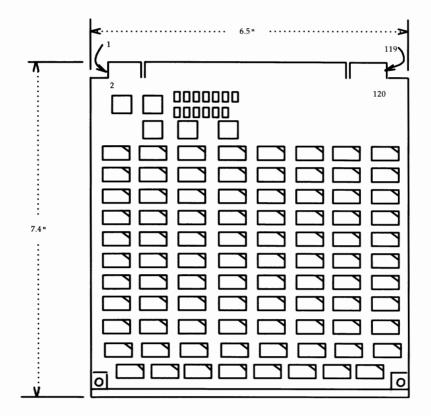

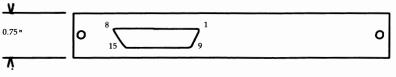

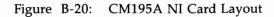

| Figure 2-44:                 | CM195AA AIC Layout                                                                                                                | 2-142        |

| 11guit 2-40.                 | Chiroffi MC Layout                                                                                                                | 2-144        |

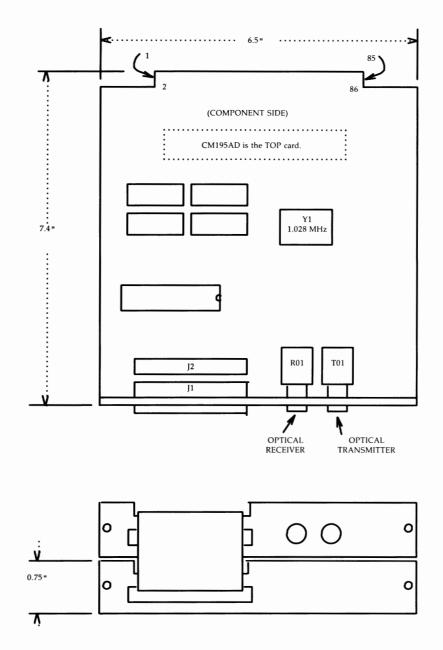

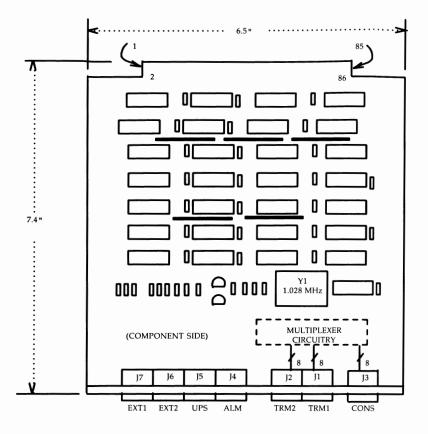

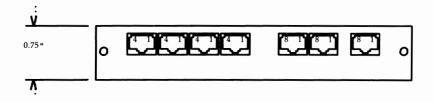

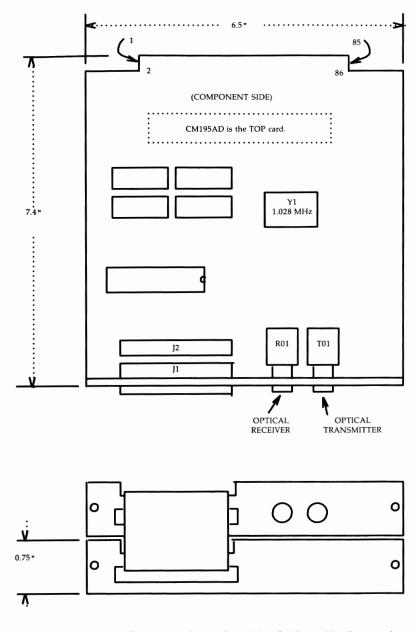

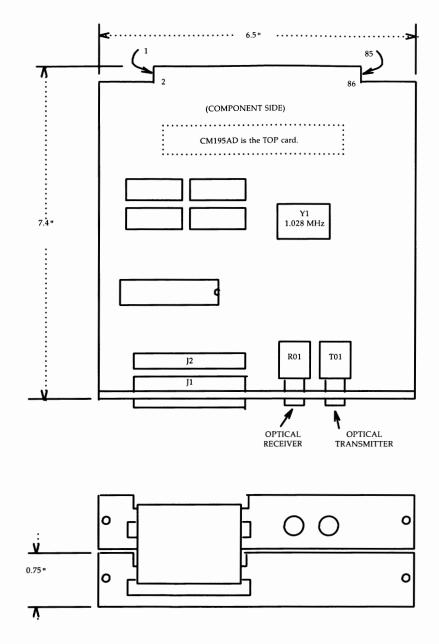

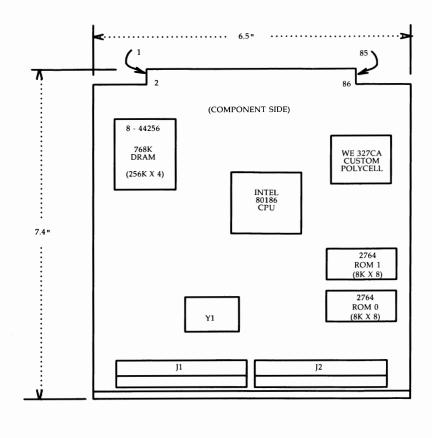

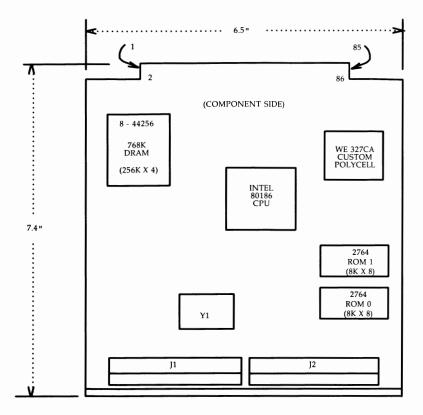

| Figure           |                           | CM195AC/CM195AD Datakit VCS Interface Card Layout                       | 2-146 |

|------------------|---------------------------|-------------------------------------------------------------------------|-------|

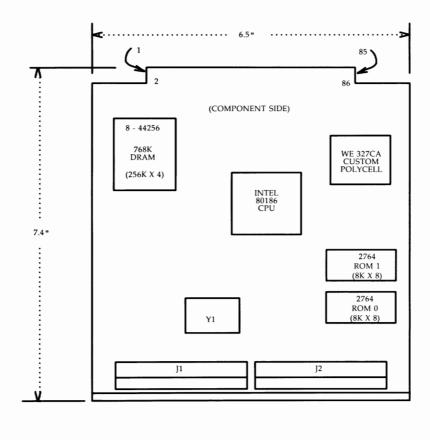

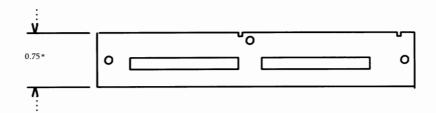

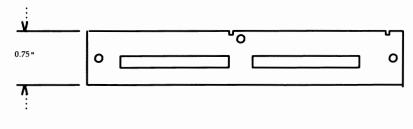

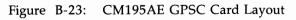

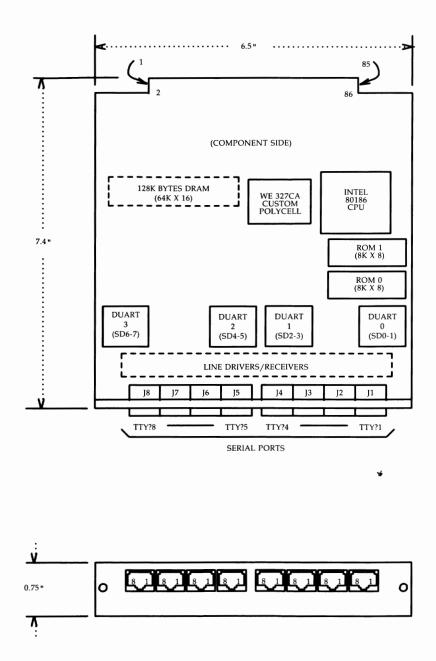

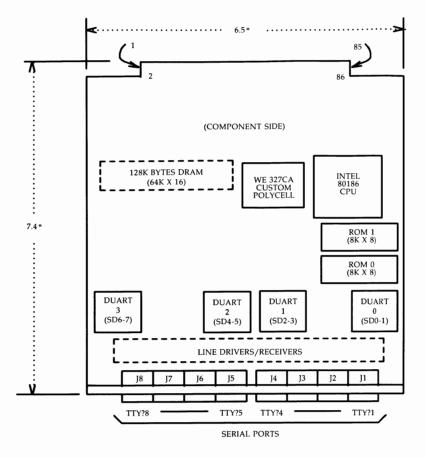

| Figure           | 2-47:                     | CM195AE GPSC Card Layout                                                |       |

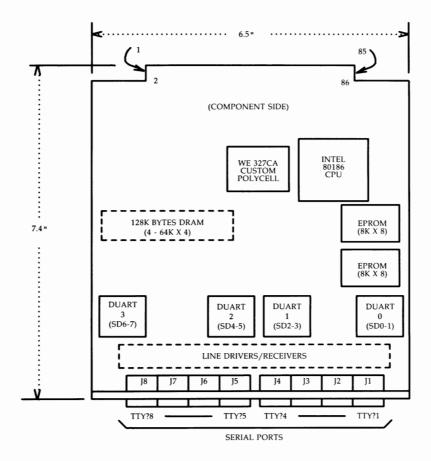

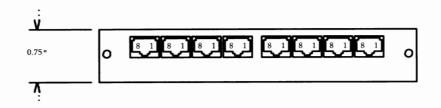

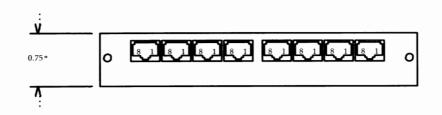

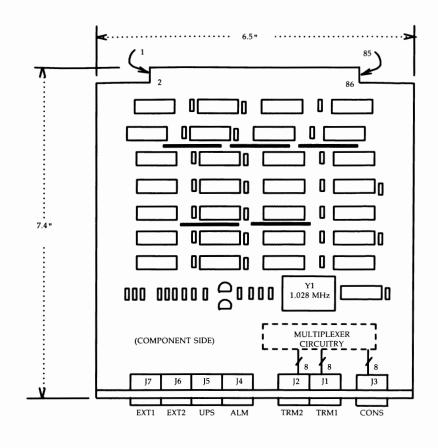

| Figure           | 2-48:                     | CM195AY EPORTS Card Layout                                              |       |

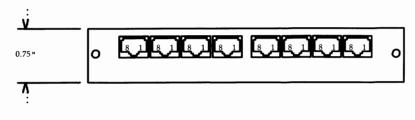

| Figure           | 2-49:                     | CM195B PORTS Card Layout (Early Production)                             | 2-152 |

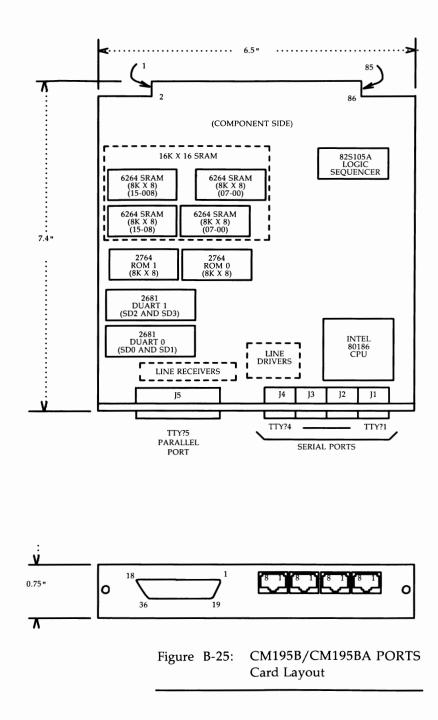

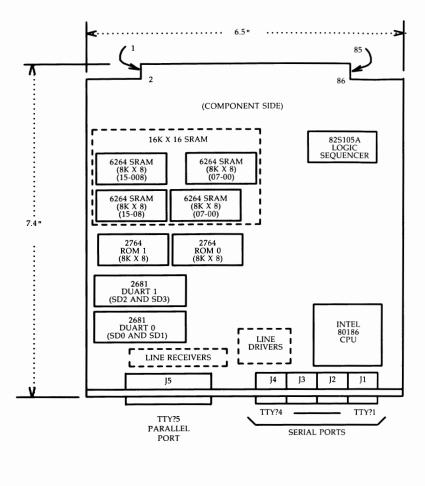

| Figure           | 2-50:                     | CM195B-7 PORTS Card Layout                                              | 2-153 |

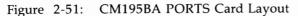

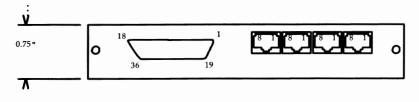

| Figure           | 2-51:                     | CM195BA PORTS Card Layout                                               | 2-156 |

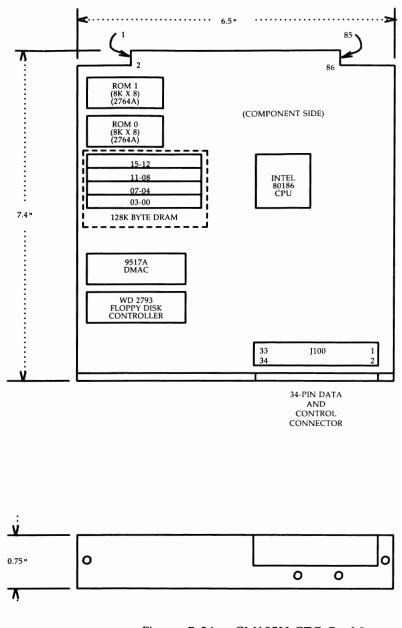

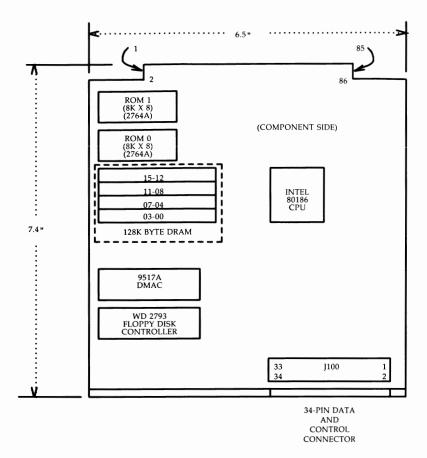

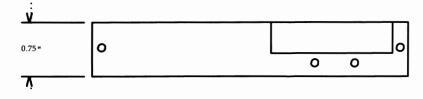

| Figure           | 2-52:                     | CM195H CTC Card Layout                                                  | 2-158 |

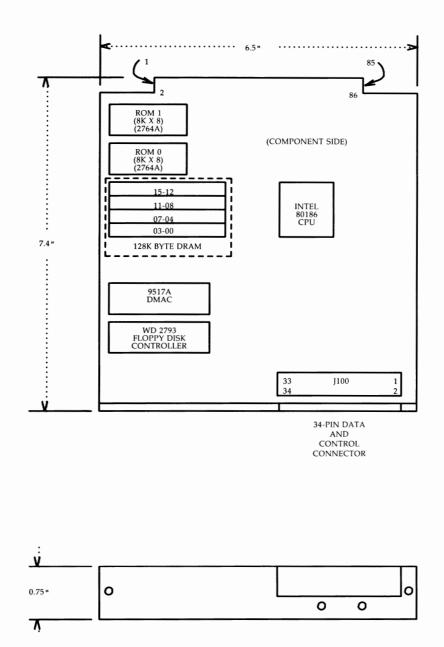

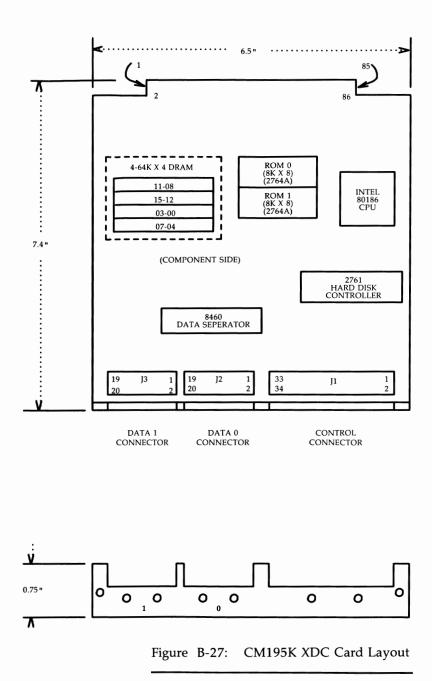

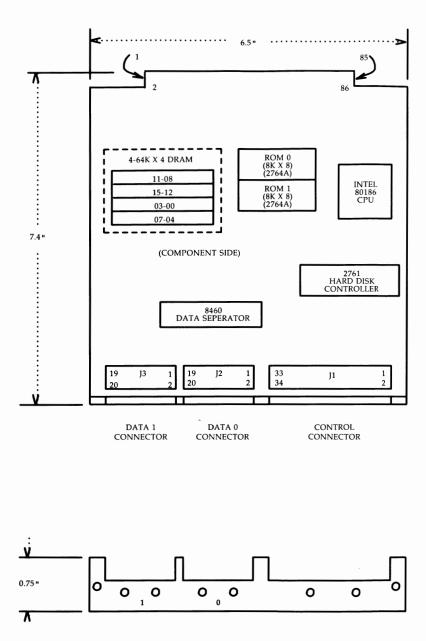

| Figure           | 2-53:                     | CM195K XDC Card Layout                                                  | 2-160 |

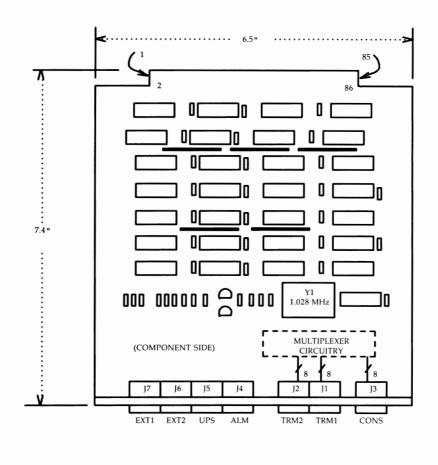

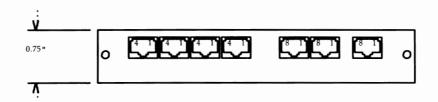

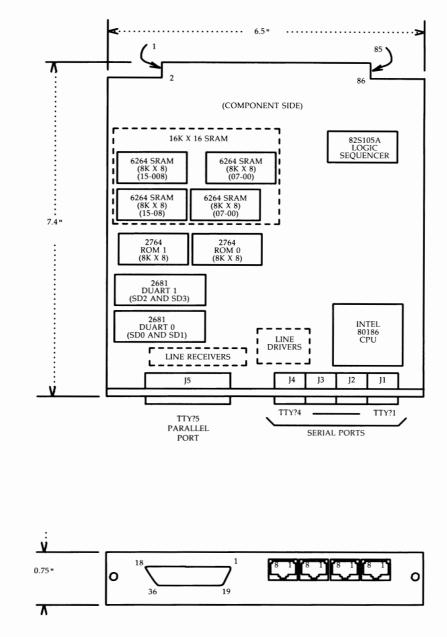

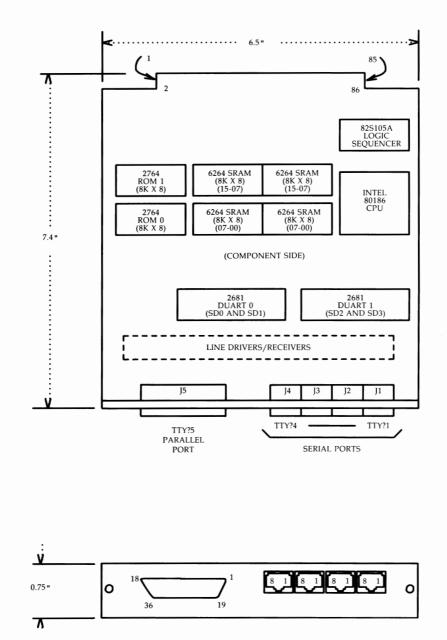

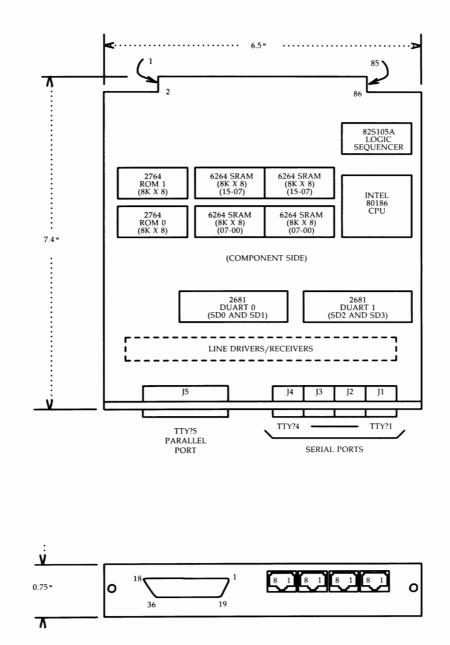

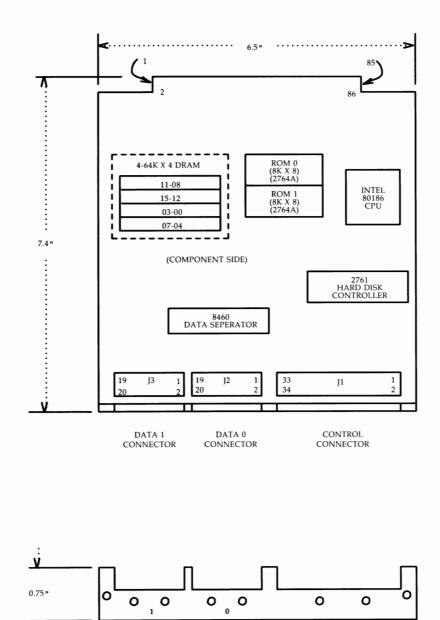

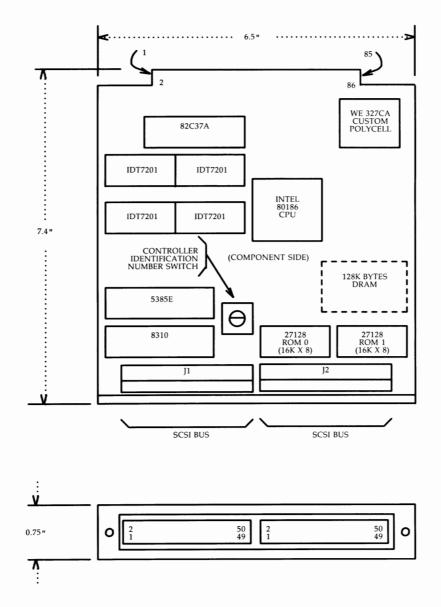

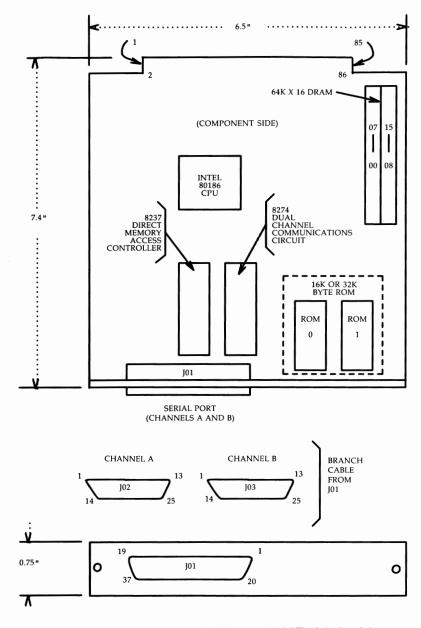

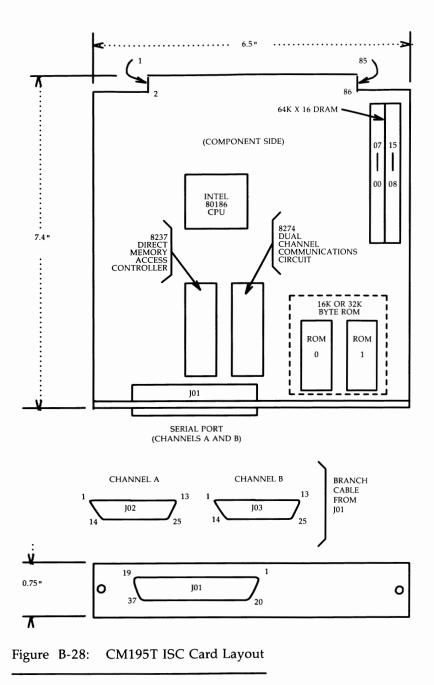

| Figure           | 2-54:                     | CM195T ISC Card Layout                                                  | 2-162 |

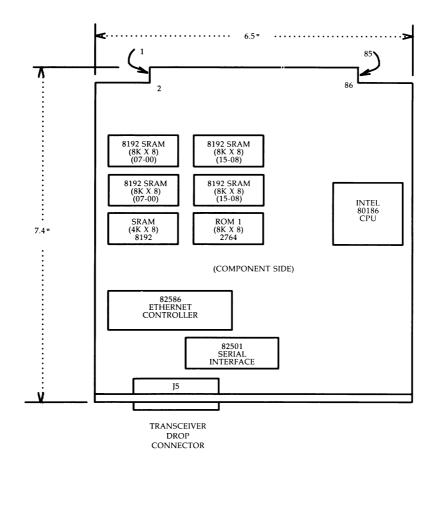

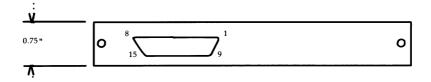

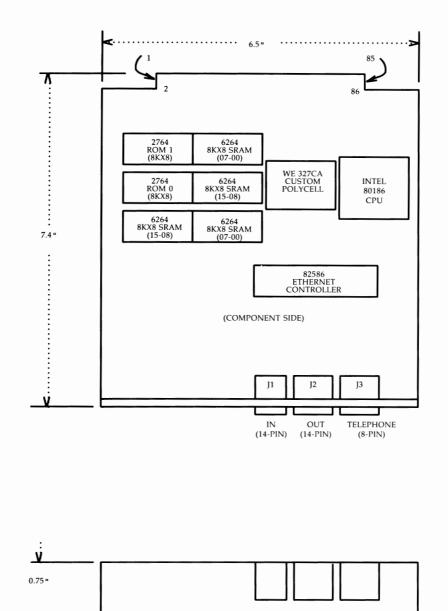

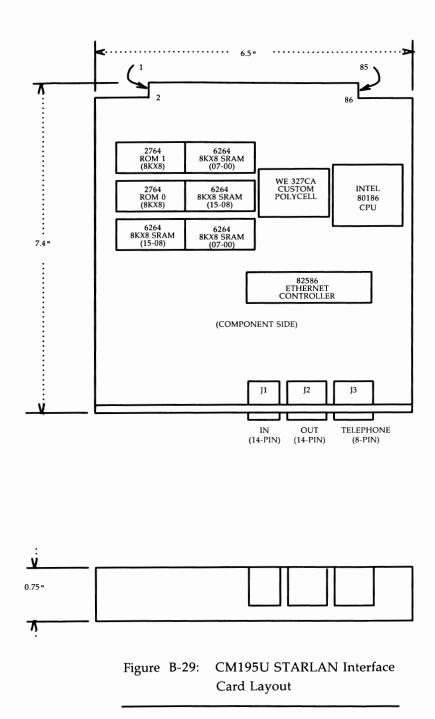

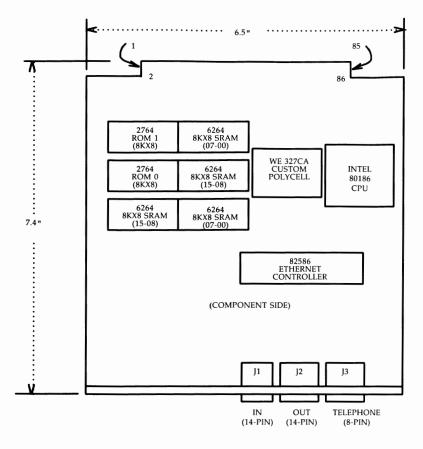

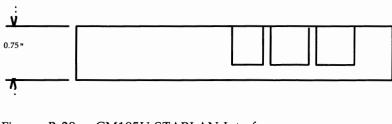

| Figure           | 2-55:                     | CM195U STARLAN Interface Card Layout                                    | 2-164 |

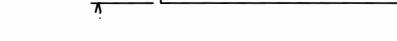

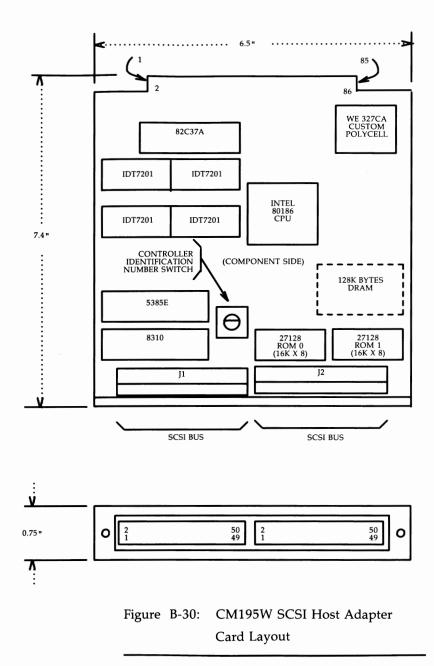

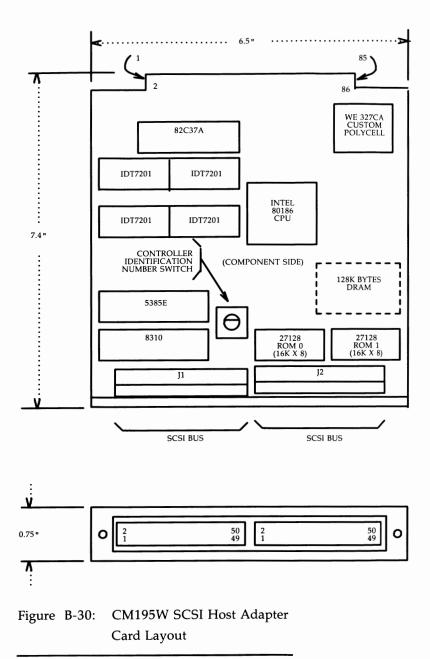

| Figure           |                           | CM195W SCSI Host Adapter Card Layout                                    | 2-166 |

| Figure           | 2-57:                     | CM195Y EPORTS Card Layout                                               | 2-168 |

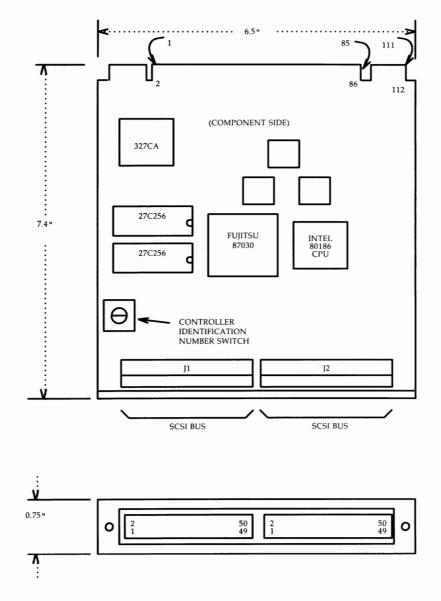

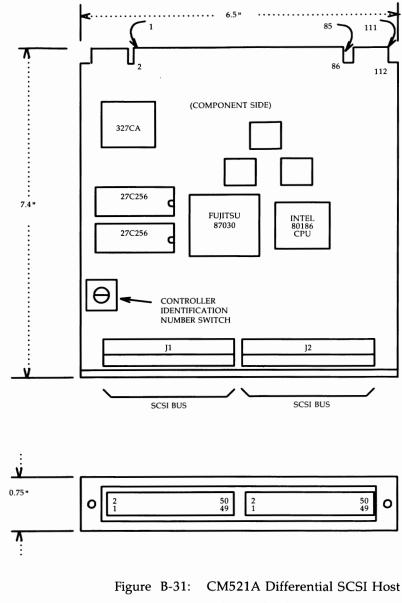

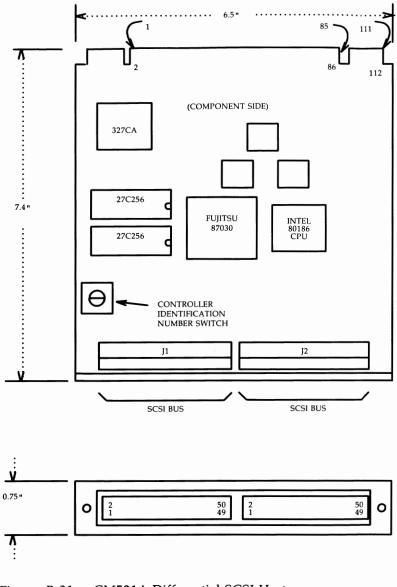

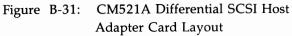

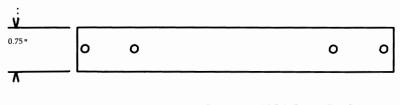

| Figure           |                           | CM521A Differential SCSI Host Adapter Card Layout                       | 2-170 |

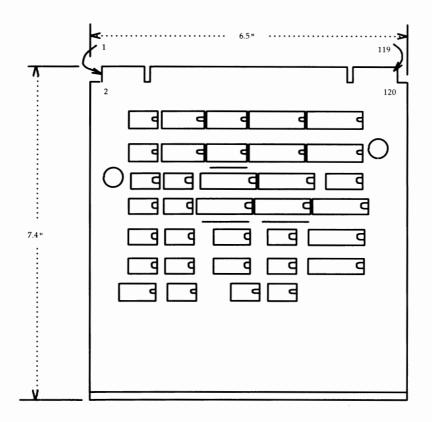

| Figure           |                           | CM522A VCACHE Card Layout                                               | 2-172 |

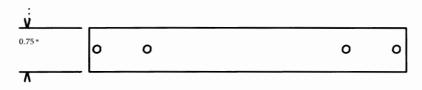

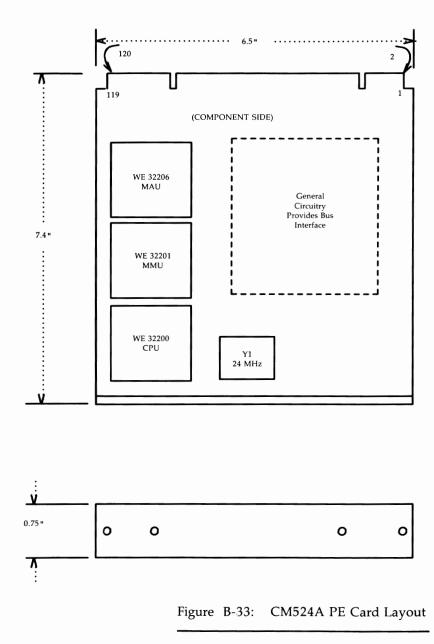

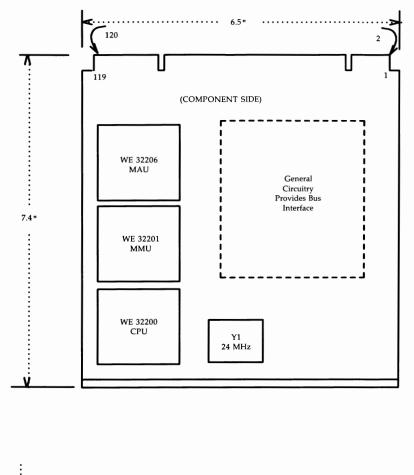

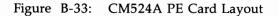

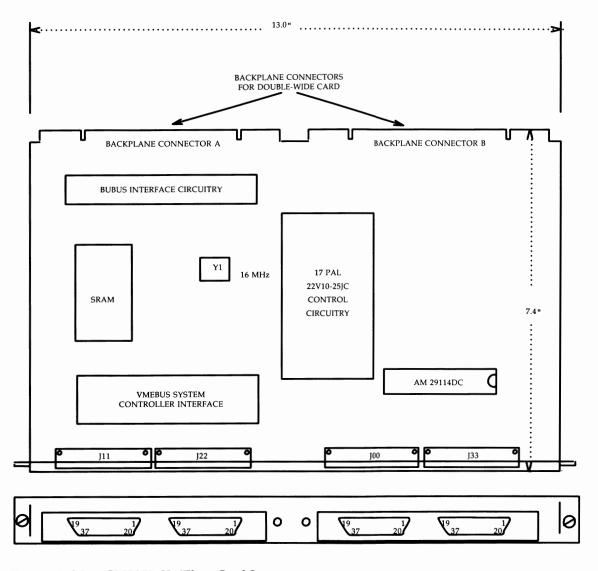

| Figure           |                           | CM524A PE Card Layout                                                   | 2-174 |

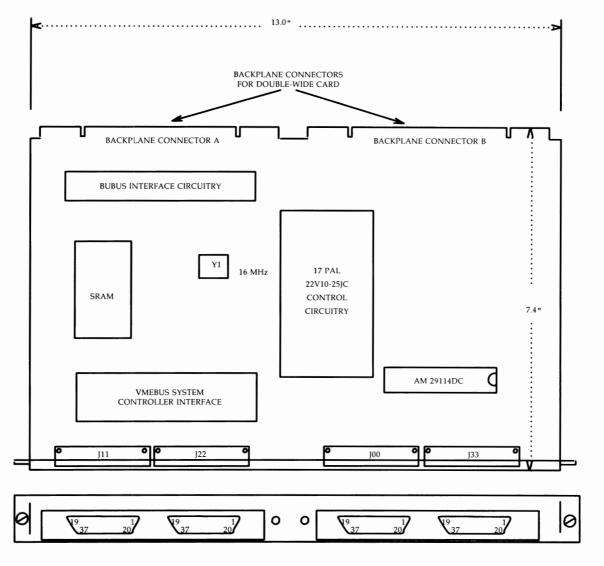

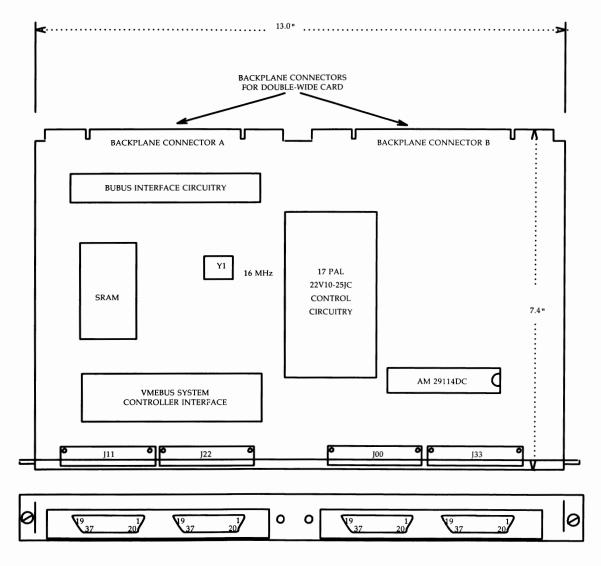

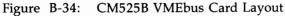

| Figure           |                           | CM525B VMEbus Card Layout                                               | 2-176 |

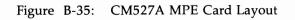

| Figure           |                           | CM527A MPE Card Layout                                                  |       |

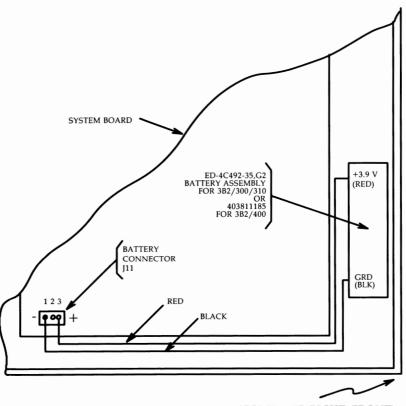

| Figure           |                           | Version 2 Computer Backup Battery Supply Layout                         |       |

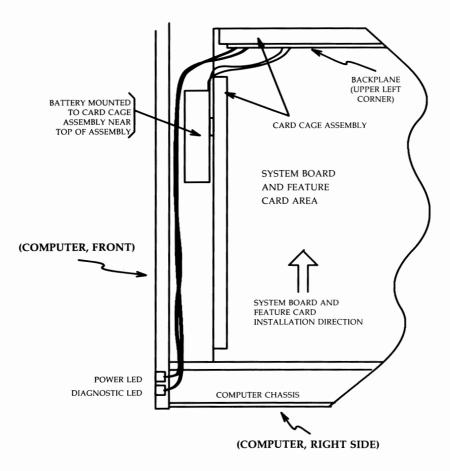

| Figure           |                           | 3B2/500 Computer Backup Battery Supply Position                         |       |

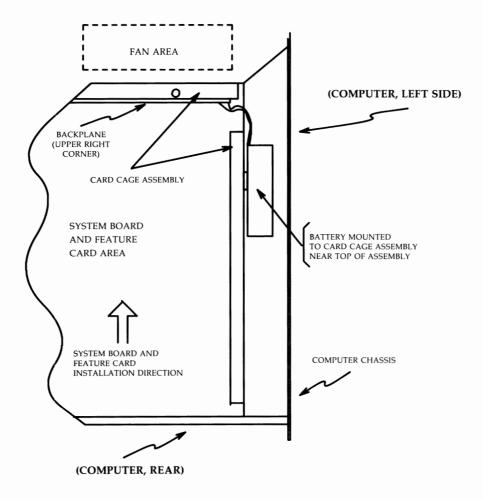

| Figure           |                           | 3B2/600, 700, and 1000 Computer Backup Battery Supply Position          | 2-220 |

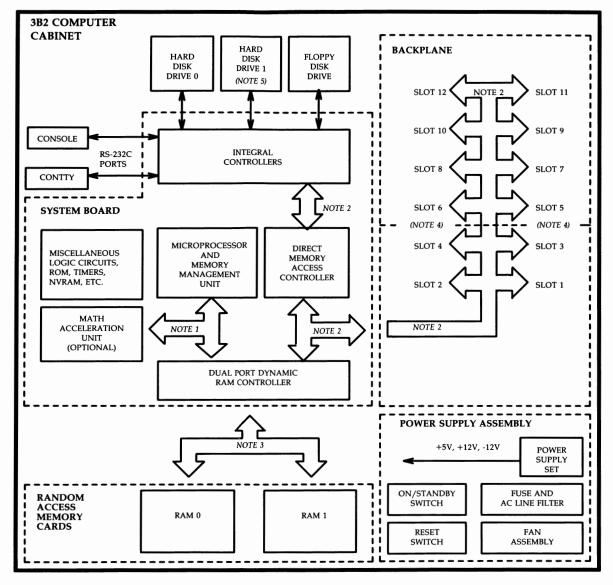

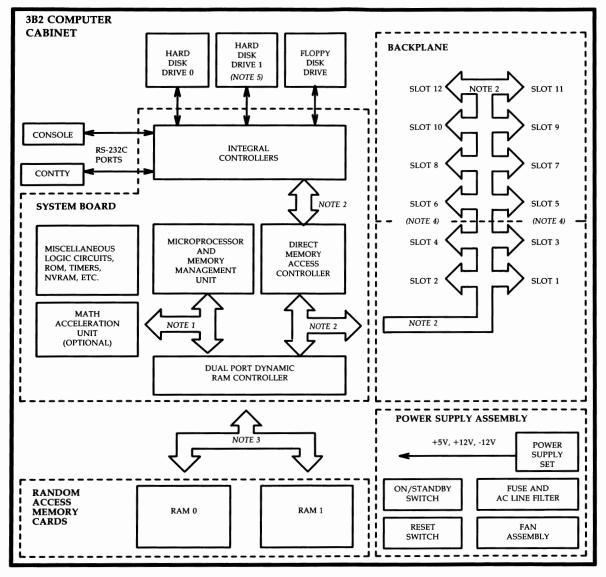

| Figure           |                           |                                                                         | 3-3   |

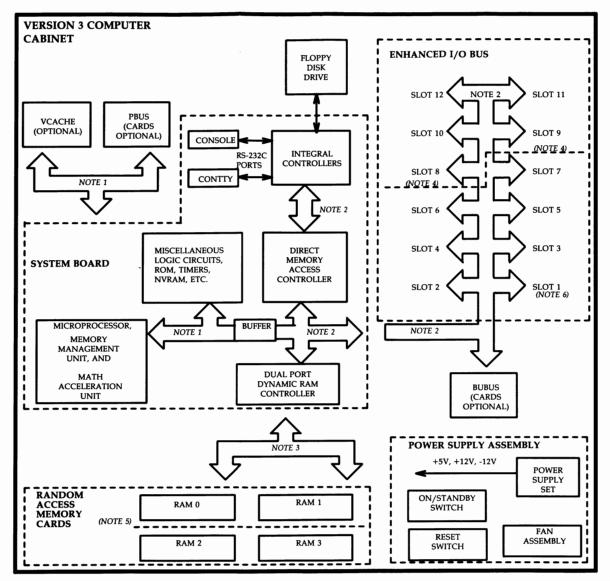

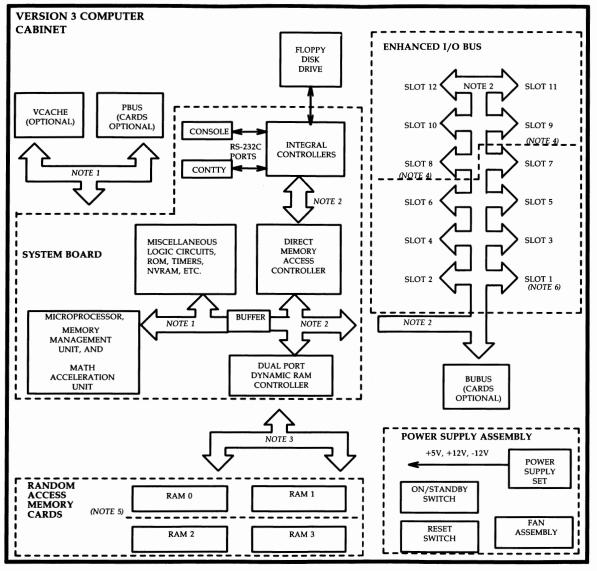

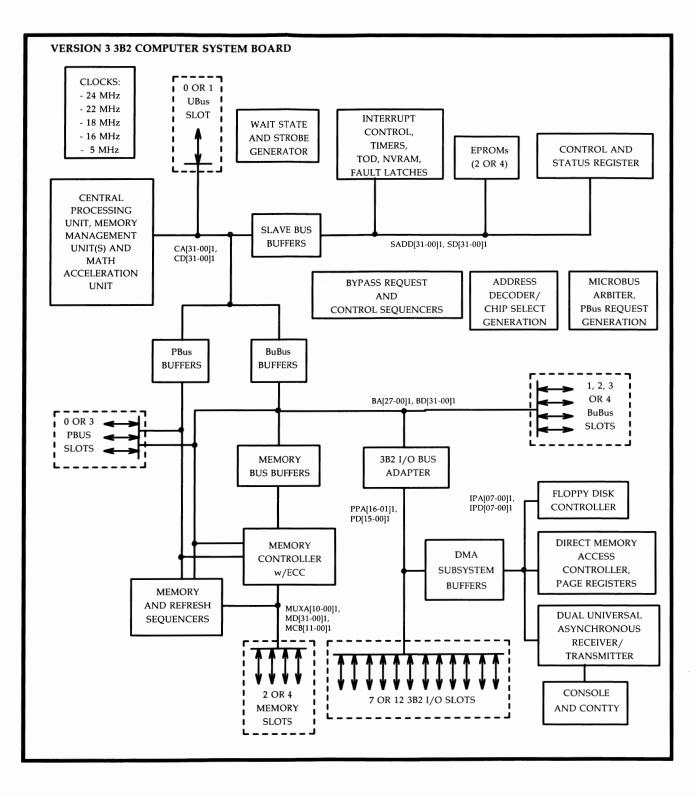

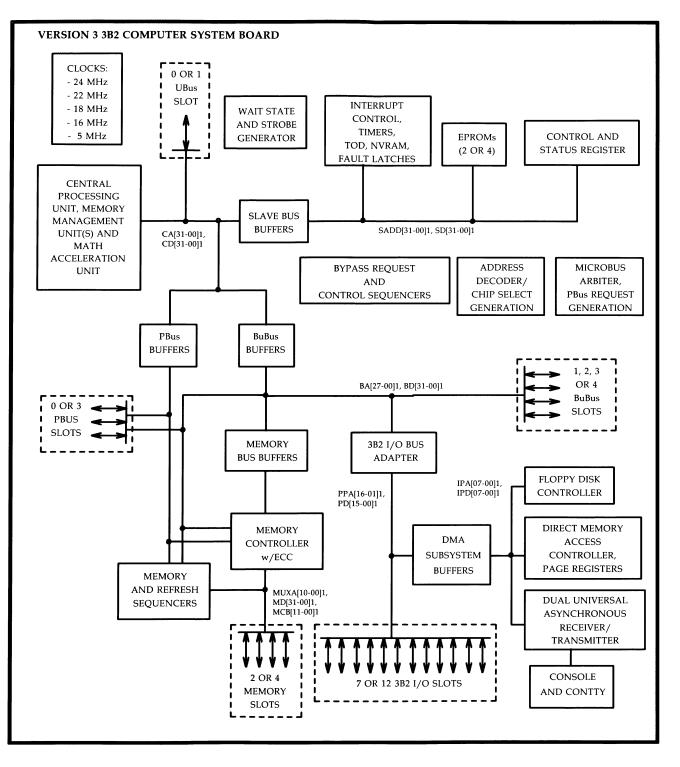

| Figure           |                           | Version 3 Computer—High-Level Functional Block Diagram                  | 3-7   |

| Figure           |                           | Version 2 Computer Address Spectrum                                     | 3-10  |

| Figure           |                           | Version 3 Computer Address Spectrum                                     | 3-11  |

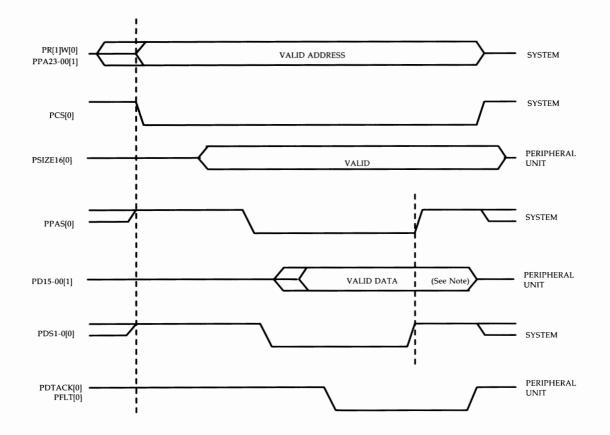

| Figure           | 3- <del>1</del> .<br>3-5: | Input/Output Bus Signals                                                | 3-14  |

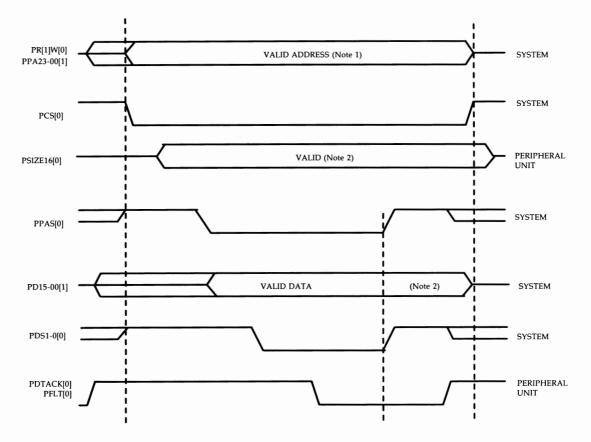

| Figure           | 3-6:                      | System Board Peripheral Controller Read Operation                       | 3-14  |

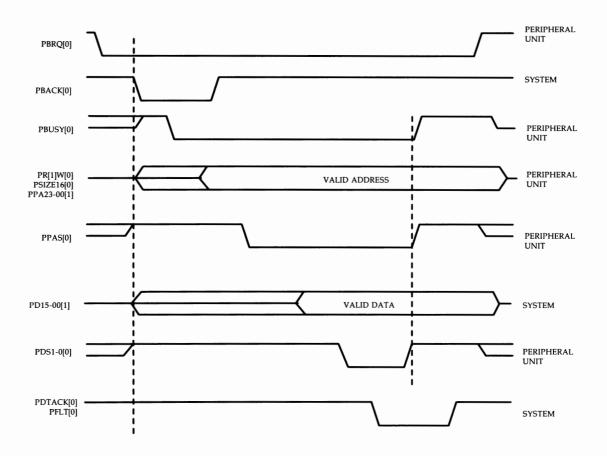

| Figure           |                           | System Board Peripheral Controller Write Operation                      | 3-20  |

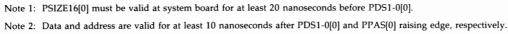

| Figure           |                           | Peripheral Controller Main Memory Read Operation                        | 3-22  |

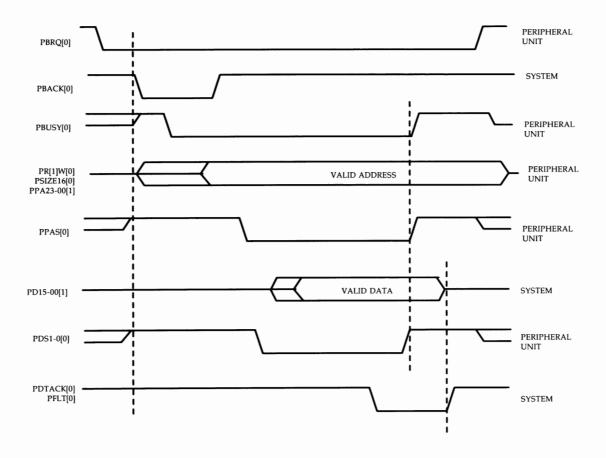

| Figure           |                           | Peripheral Controller Main Memory Write Operation                       | 3-24  |

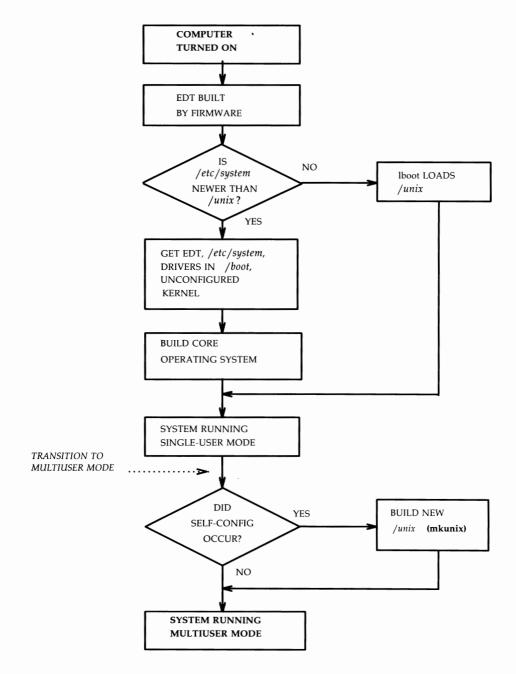

| Figure           |                           | Self-Configuration — Powerup Sequence                                   | 3-27  |

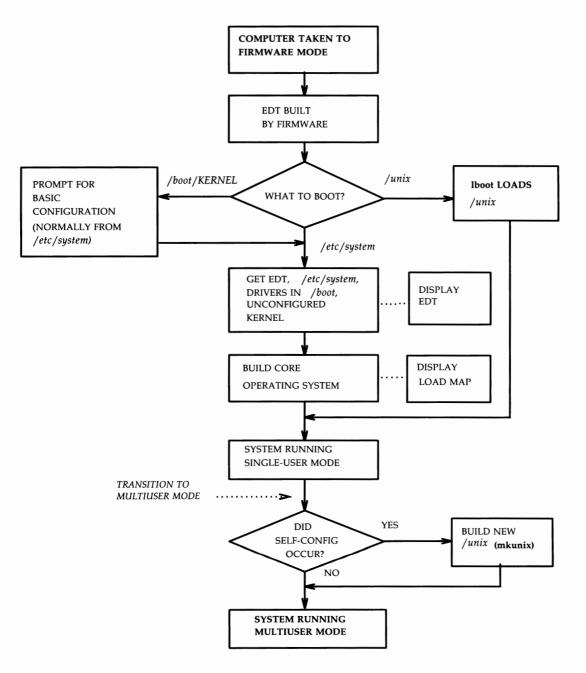

| Figure           |                           | Self-Configuration — Manual Boot Sequence                               | 3-28  |

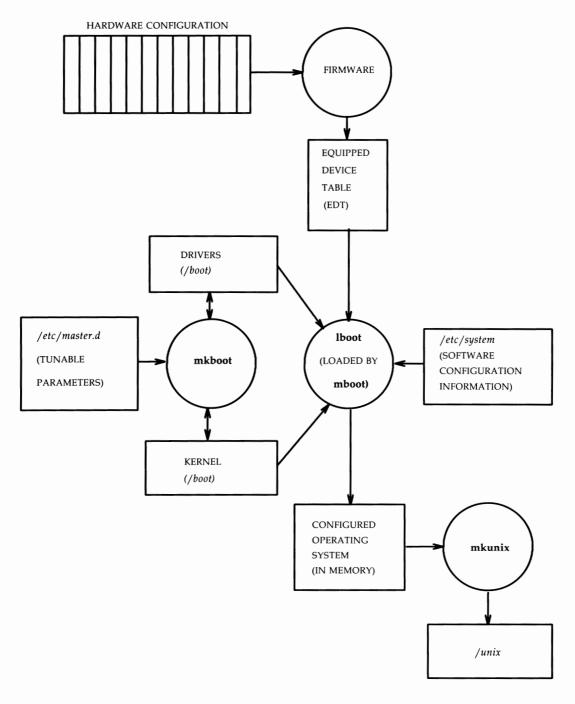

| Figure           |                           | Self-Configuration Process                                              | 3-30  |

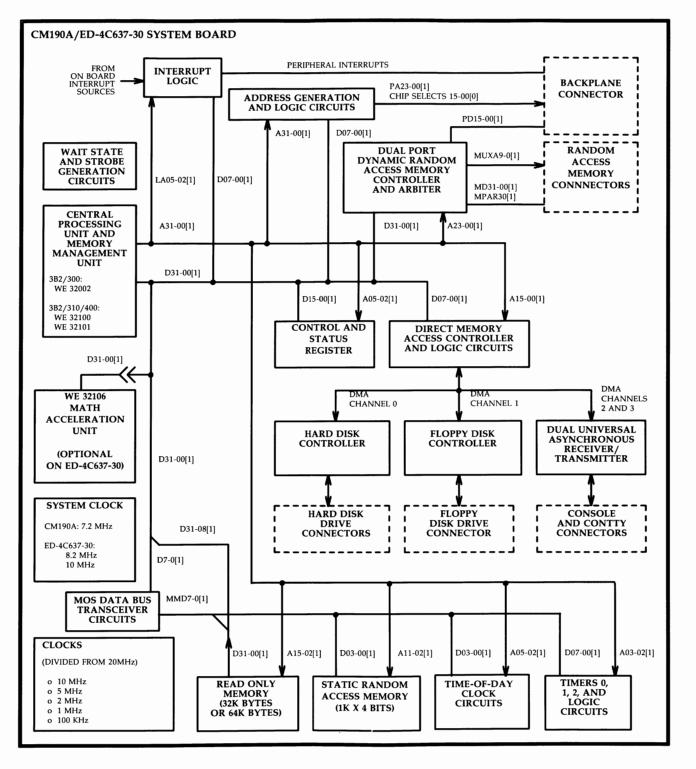

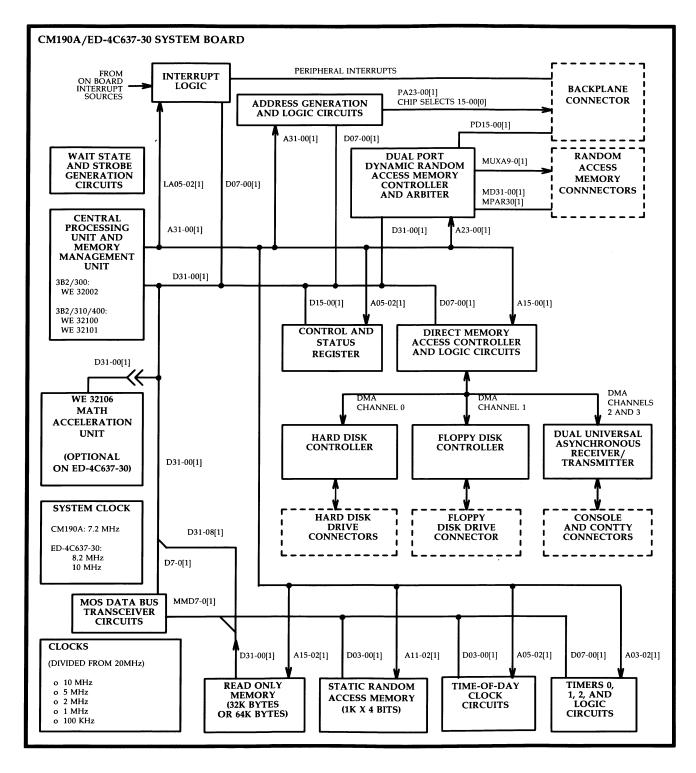

| Figure           |                           | Version 2 3B2 Computer System Board—Functional Block Diagram            | 3-33  |

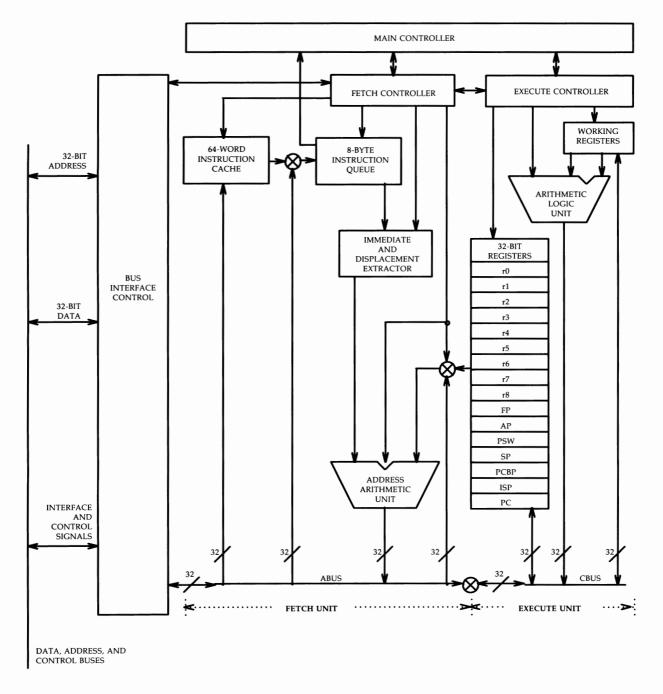

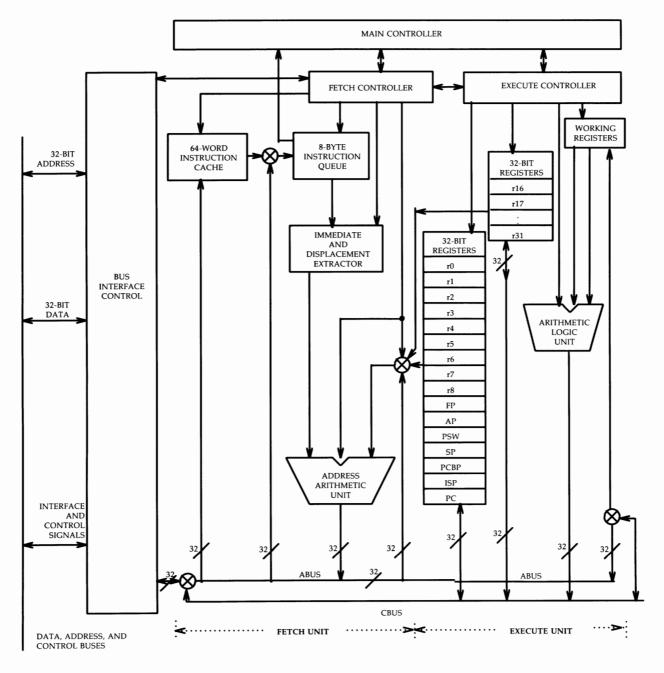

| 0                |                           | System Board CPU—Functional Block Diagram                               | 3-36  |

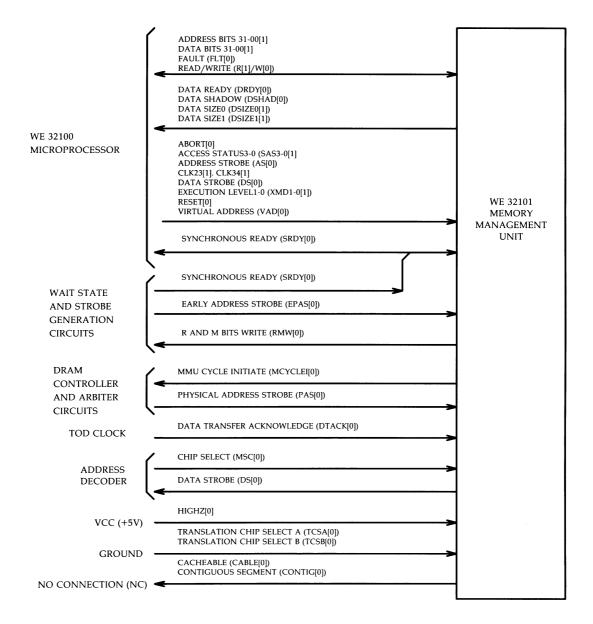

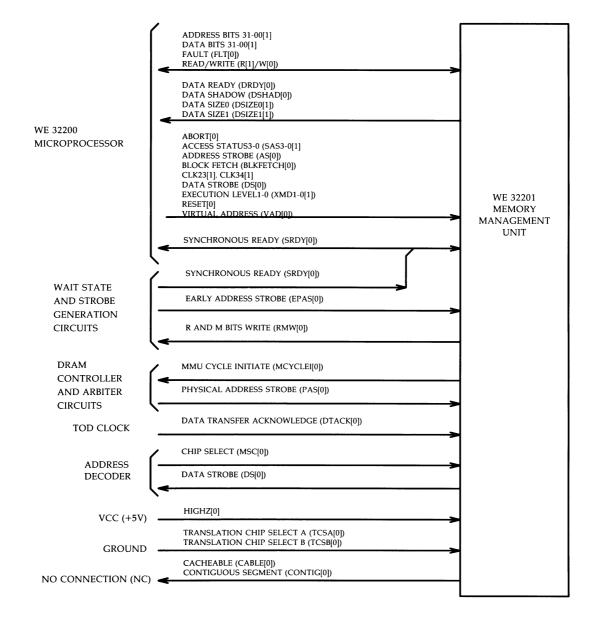

| Figure<br>Figure |                           | WE 32101 MMU Interconnection Diagram                                    | 3-44  |

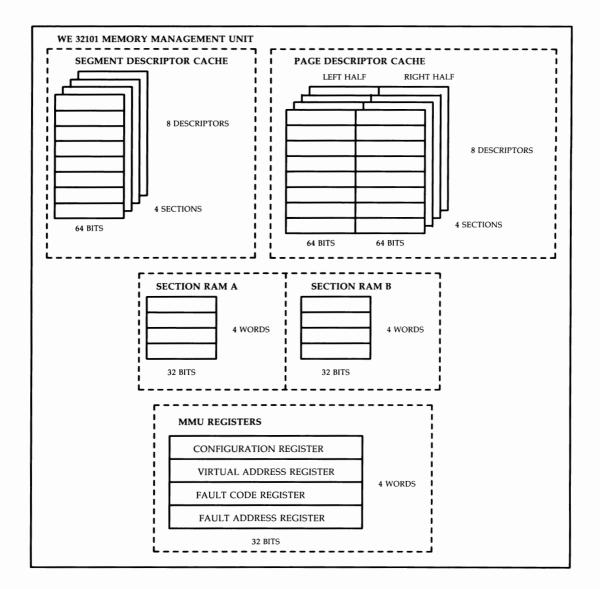

| Figure           |                           | WE 32101 MMU Block Diagram                                              | 3-45  |

| Figure           |                           | MMU Internal Address Spectrum                                           | 3-45  |

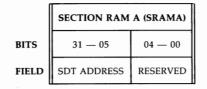

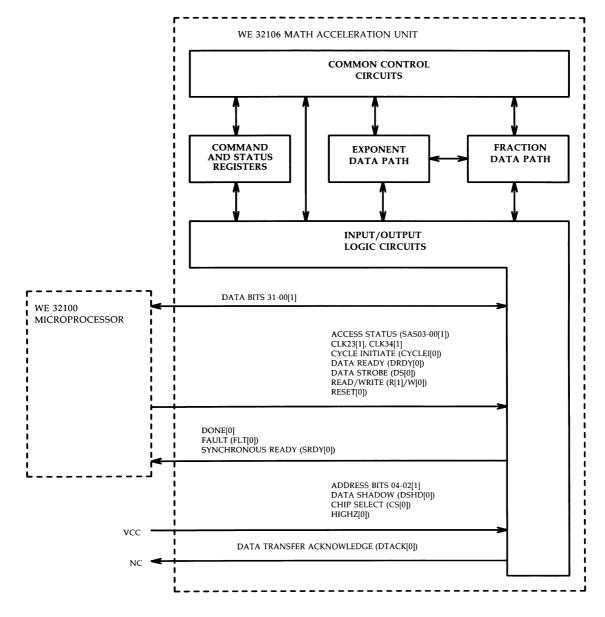

| Figure           |                           | Virtual Address to Physical Address Translation for Contiguous Segments | 3-53  |

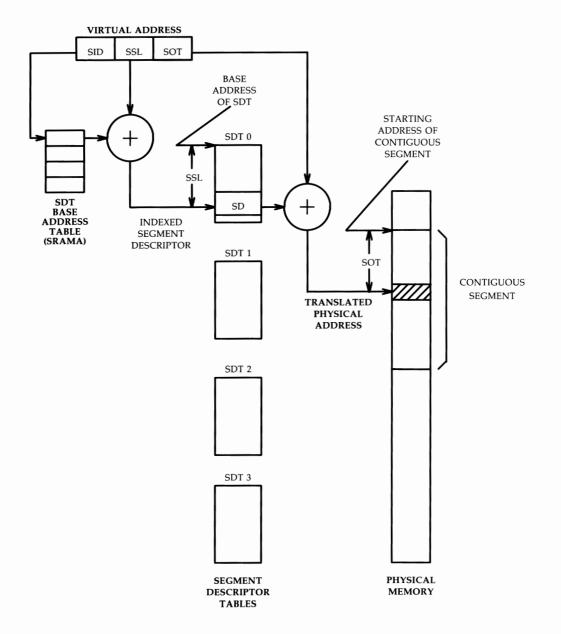

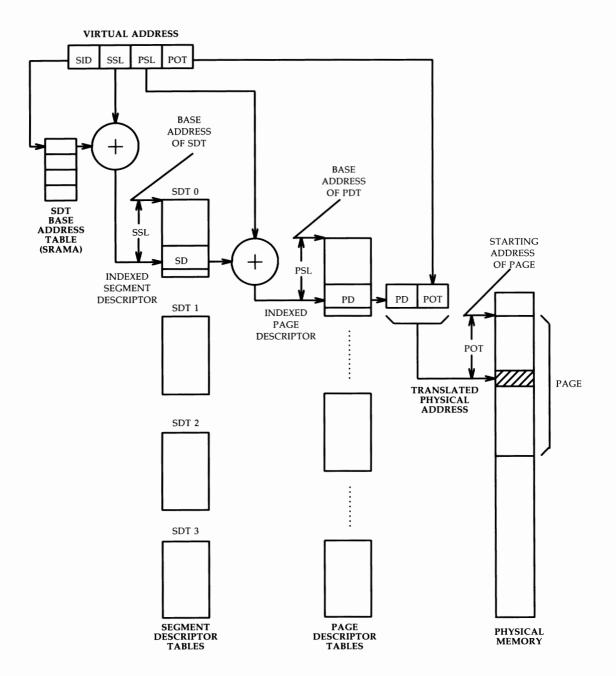

| Figure           |                           | Virtual Address to Physical Address Translation for Paged Segments      | 3-54  |

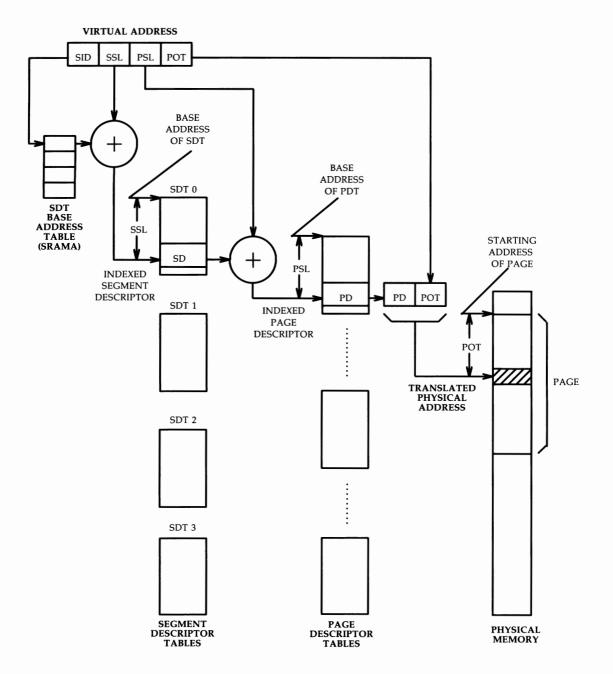

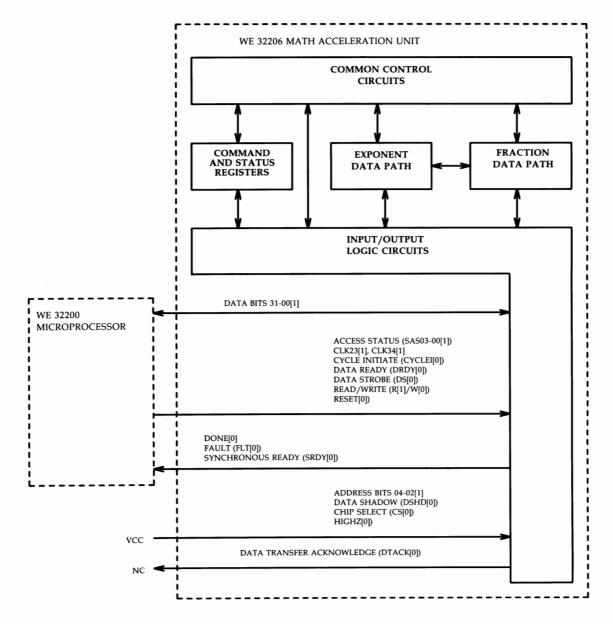

| Figure           |                           | WE 32106 Math Acceleration Unit—Functional Block Diagram                | 3-54  |

| Figure           |                           | Chip Select and Control Signals Address Decode                          | 3-64  |

| •                |                           | Version 2 System Board CSR Bit Assignments                              | 3-68  |

| Figure           |                           | System Board Interrupt Assignments                                      | 3-70  |

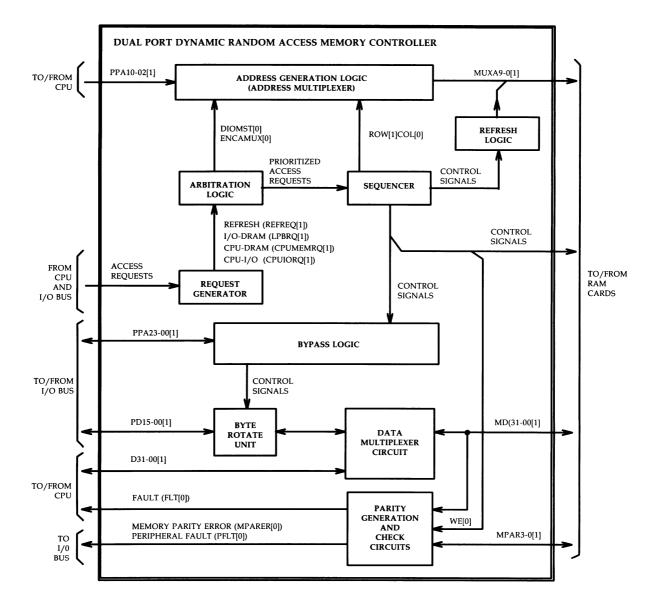

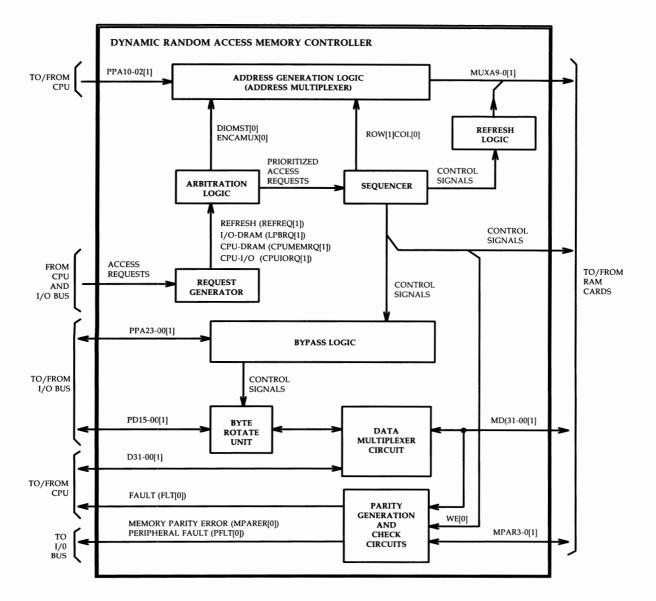

| Figure           |                           | Dual Port Dynamic Random Access Memory Controller—Functional Block      | 3-70  |

| Figure           | 3-24:                     |                                                                         | 2 74  |

| <b>T</b> .       | 0.05                      | Diagram                                                                 | 3-74  |

| Figure           |                           | Data Byte Selection Summary                                             | 3-77  |

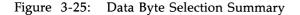

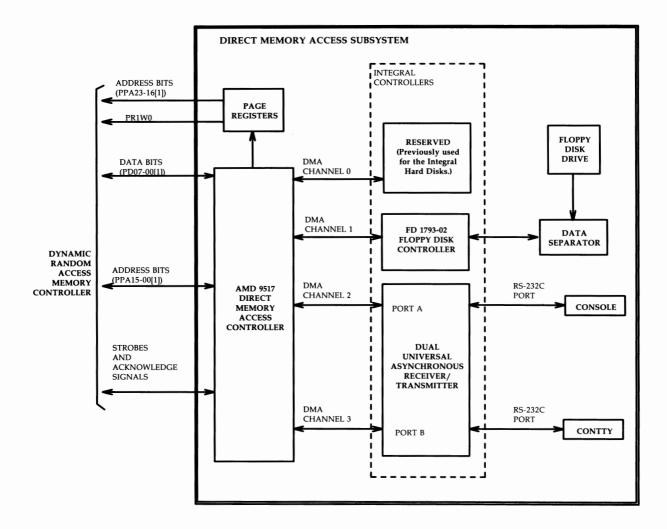

| Figure           |                           | Direct Memory Access Subsystem—Functional Block Diagram                 | 3-79  |

| Figure           |                           | Version 3 3B2 Computer System Board—Functional Block Diagram            | 3-87  |

| Figure           |                           | CM518B/C System Board CPU—Functional Block Diagram                      | 3-90  |

| Figure           |                           | WE 32201 MMU Interconnection Diagram                                    | 3-98  |

| Figure           |                           | MMU Internal Address Spectrum                                           | 3-104 |

| Figure           |                           | Virtual Address to Physical Address Translation for Paged Segments      | 3-106 |

| Figure           | 3-32:                     | WE 32206 Math Acceleration Unit—Functional Block Diagram                | 3-108 |

|                                                                                                                                                                                                      | 3-33:                                                                                                                                                                                                                | Chip Select and Control Signals Address Decode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-118                                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure                                                                                                                                                                                               | 3-34:                                                                                                                                                                                                                | Version 3 System Board CSER Bit Assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-122                                                                                                                                                                                                                         |

| Figure                                                                                                                                                                                               | 3-35:                                                                                                                                                                                                                | Version 3 System Board Interrupt Assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-124                                                                                                                                                                                                                         |

| Figure                                                                                                                                                                                               | 3-36:                                                                                                                                                                                                                | Dynamic Random Access Memory Controller—Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                               |

| Figure                                                                                                                                                                                               | 3-37:                                                                                                                                                                                                                | Data Byte Selection Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                               |

| Figure                                                                                                                                                                                               |                                                                                                                                                                                                                      | Direct Memory Access Subsystem—Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-133                                                                                                                                                                                                                         |

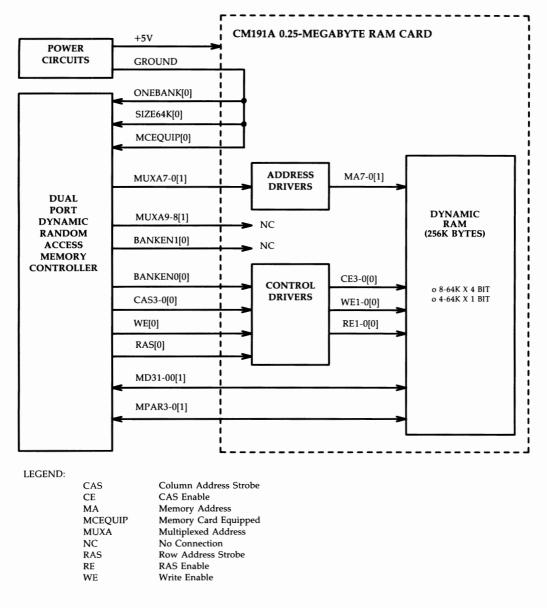

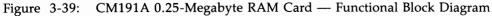

| Figure                                                                                                                                                                                               |                                                                                                                                                                                                                      | CM191A 0.25-Megabyte RAM Card—Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                               |

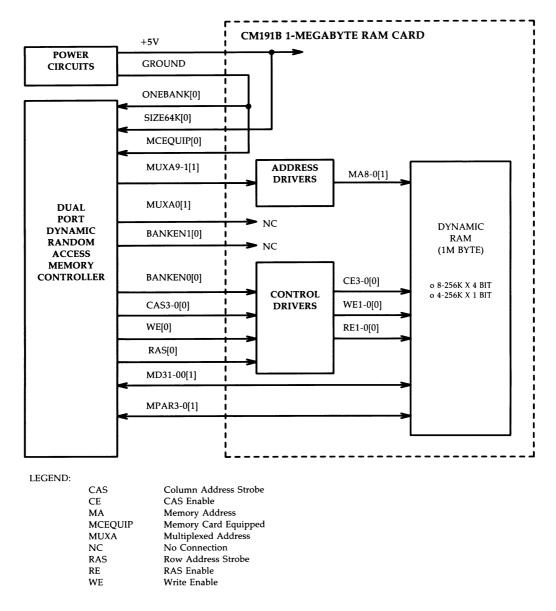

| Figure                                                                                                                                                                                               |                                                                                                                                                                                                                      | CM191B 1-Megabyte RAM Card—Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                               |

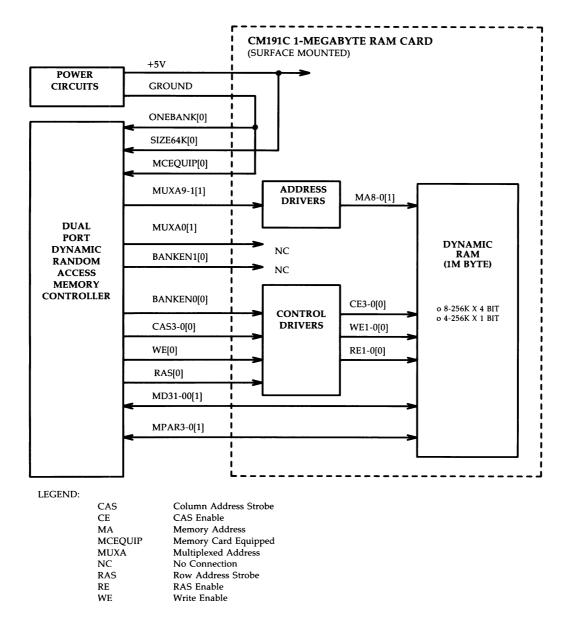

| Figure                                                                                                                                                                                               |                                                                                                                                                                                                                      | CM191C 1-Megabyte, Surface Mounted, RAM Card—Functional Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0 111                                                                                                                                                                                                                         |

| - igure                                                                                                                                                                                              | 0 11.                                                                                                                                                                                                                | Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-142                                                                                                                                                                                                                         |

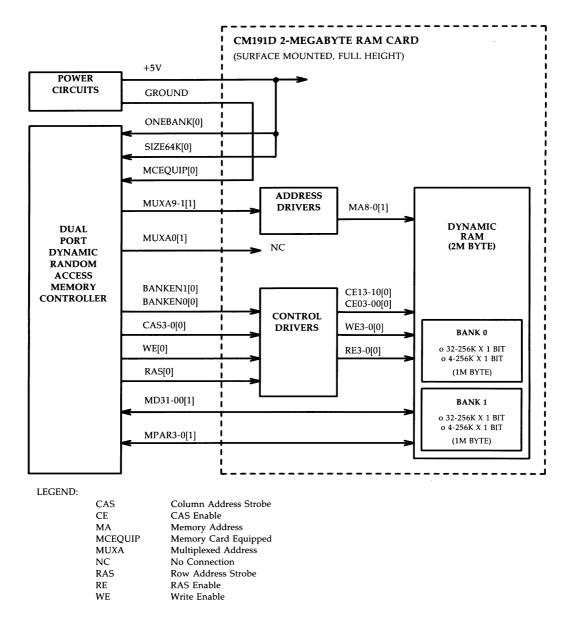

| Figure                                                                                                                                                                                               | 3-42.                                                                                                                                                                                                                | CM191D 2-Megabyte, Surface Mounted, Full Height, RAM Card—                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-142                                                                                                                                                                                                                         |

| riguie                                                                                                                                                                                               | J- <b>4</b> 2.                                                                                                                                                                                                       | Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2 1 4 2                                                                                                                                                                                                                       |

| Figuro                                                                                                                                                                                               | 2 12.                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-145                                                                                                                                                                                                                         |

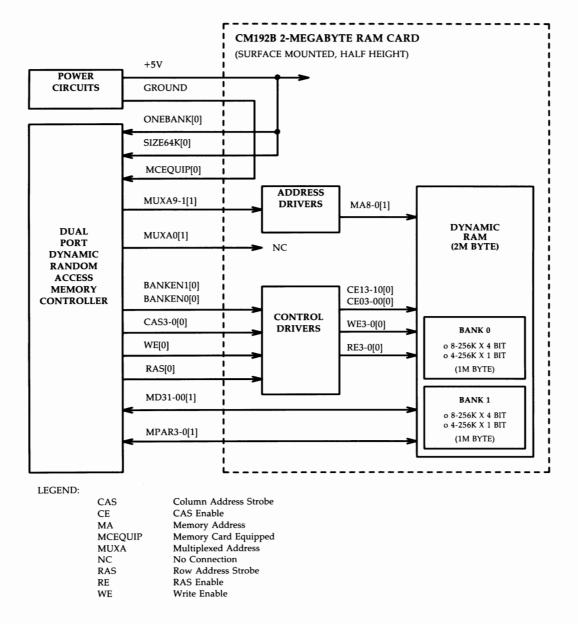

| Figure                                                                                                                                                                                               | 5-45.                                                                                                                                                                                                                | CM192B 2-Megabyte, Surface Mounted, Half Height, RAM Card—                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0 1 4 4                                                                                                                                                                                                                       |

| <b>F</b> !                                                                                                                                                                                           | 2 44.                                                                                                                                                                                                                | Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-144                                                                                                                                                                                                                         |

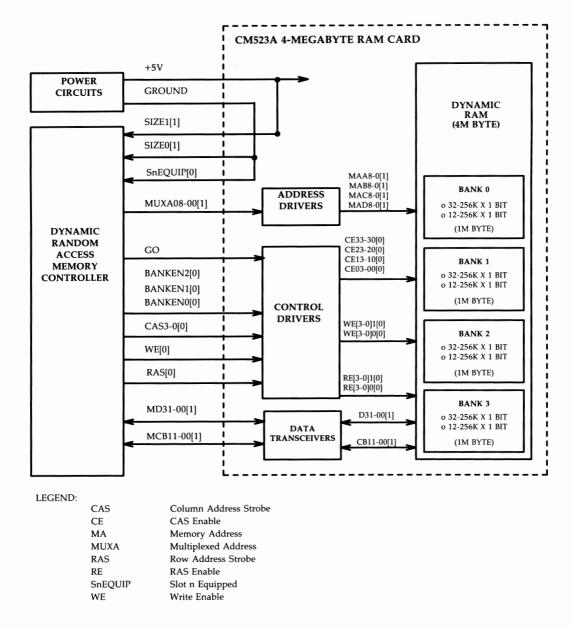

| Figure                                                                                                                                                                                               |                                                                                                                                                                                                                      | CM523A 4-Megabyte RAM Card—Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                               |

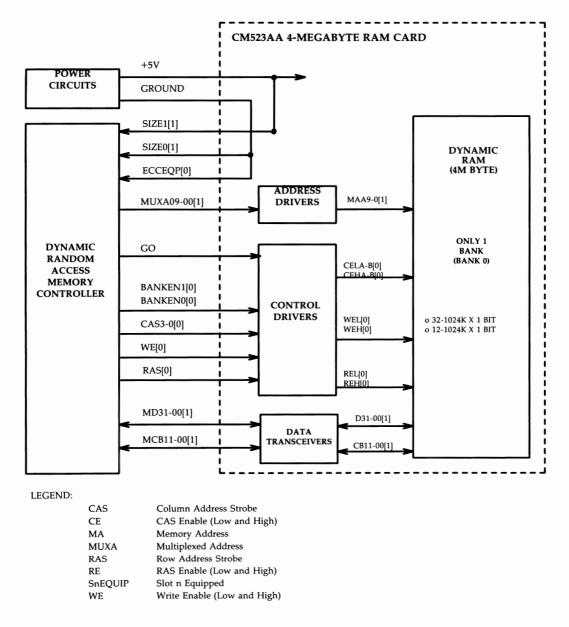

| Figure                                                                                                                                                                                               |                                                                                                                                                                                                                      | CM523AA 4-Megabyte RAM Card—Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-148                                                                                                                                                                                                                         |

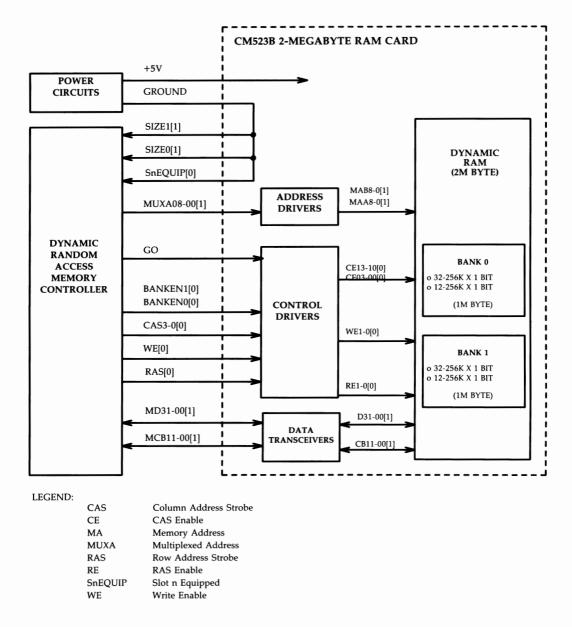

| Figure                                                                                                                                                                                               |                                                                                                                                                                                                                      | CM523B 2-Megabyte RAM Card—Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                               |

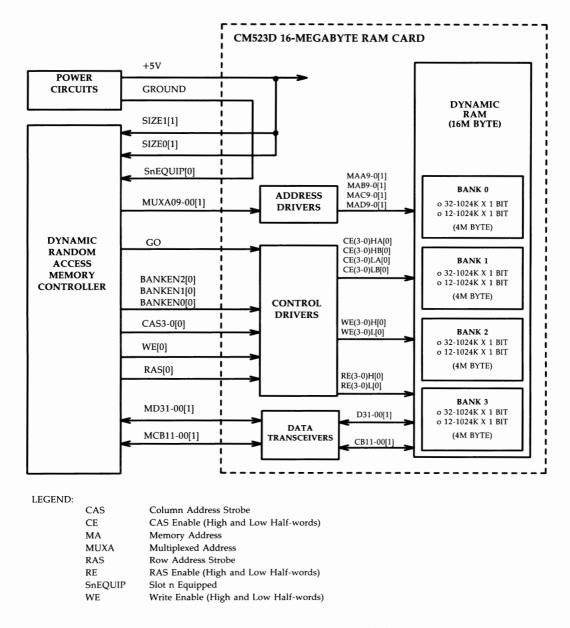

| Figure                                                                                                                                                                                               |                                                                                                                                                                                                                      | CM523D 16-Megabyte RAM Card—Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                               |

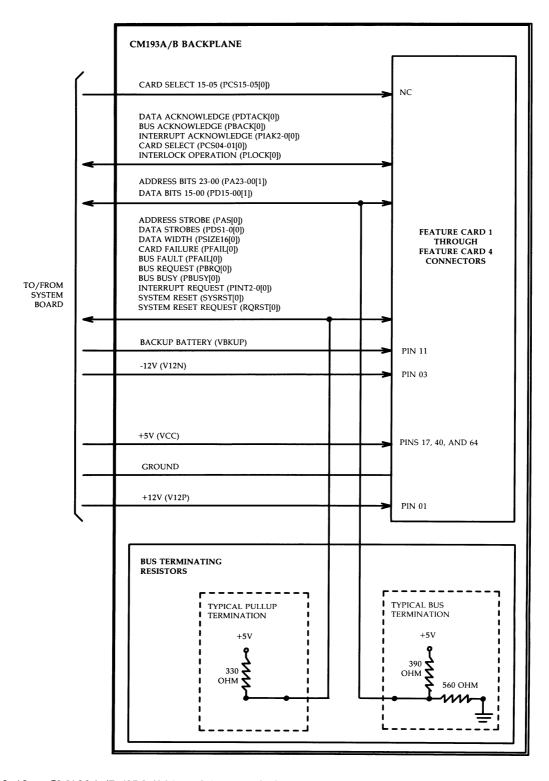

| Figure                                                                                                                                                                                               | 3-48:                                                                                                                                                                                                                | CM193A/B (3B2/300 and 310) Backplane—Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-155                                                                                                                                                                                                                         |

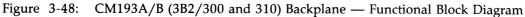

| Figure                                                                                                                                                                                               | 3-49:                                                                                                                                                                                                                | CM194B (3B2/400) Backplane—Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-157                                                                                                                                                                                                                         |

| Figure                                                                                                                                                                                               | 3-50:                                                                                                                                                                                                                | CM519A (3B2/600 and 700) Backplane—Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-159                                                                                                                                                                                                                         |

| Figure                                                                                                                                                                                               | 3-51:                                                                                                                                                                                                                | CM519B (3B2/1000) Backplane—Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-161                                                                                                                                                                                                                         |

| Figure                                                                                                                                                                                               | 3-52:                                                                                                                                                                                                                | CM520A (3B2/500) Backplane—Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                               |

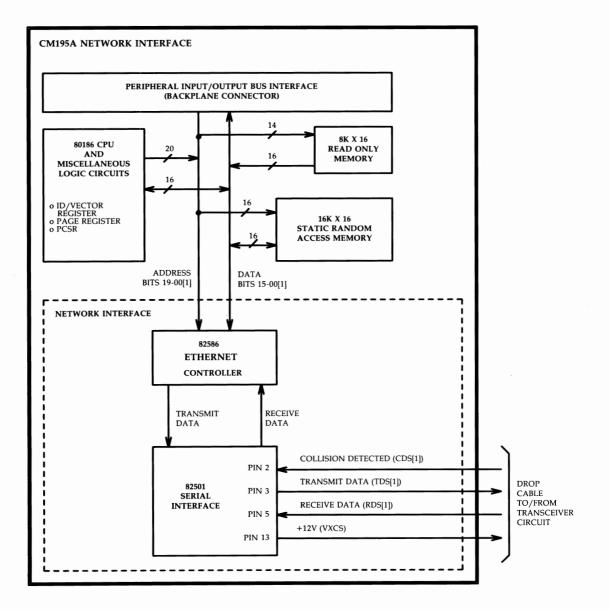

| Figure                                                                                                                                                                                               |                                                                                                                                                                                                                      | CM195A NI Card—Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                               |

| Figure                                                                                                                                                                                               |                                                                                                                                                                                                                      | CM195A NI Card Address Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                               |