# An0030

## **CPU-1432; TFT Digital Interface**

Rev. 1.0 Sep. 2003

#### **ABOUT THIS MANUAL**

This application note contains information about the TFT Digital Interface installed on the CPU-1432.

Via J. Linussio 1 33020 AMARO (UD) ITALY

Phone: +39 0433 485 411 Fax: +39 0433 485 499

web: <a href="http://www.eurotech.it">http://www.eurotech.it</a> e-mail: <a href="mailto:sales@eurotech.it">mailto:sales@eurotech.it</a>

#### **NOTICE**

Although all the information contained herein has been carefully verified, Eurotech S.p.A. assumes no responsibility for errors that might appear in this document, or for damage to property or persons resulting from an improper use of this manual and of the related software. Eurotech S.p.A. reserves the right to change the contents and form of this document, as well as the features and specifications of its products at any time, without notice.

Trademarks and registered trademarks appearing in this document are the property of their respective owners

#### Conventions

The following table lists conventions used throughout this guide.

| lcon    | Notice Type      | Description                                                                                              |  |  |  |

|---------|------------------|----------------------------------------------------------------------------------------------------------|--|--|--|

| i       | Information note | Important features or instructions                                                                       |  |  |  |

| <u></u> | Warning          | Information to alert you to potential damage to a program, system or device or potential personal injury |  |  |  |

(This page is intentionally left blank.)

# **Table of Contents**

| Conventions                                      | 3  |

|--------------------------------------------------|----|

| Table of Contents                                | 5  |

| Chapter 1 CPU-1432 TFT Digital Interface         |    |

| TFT Digital Interface Overview                   | 7  |

| J4 TFT Digital Interface Connector               |    |

| J4 TFT Digital Interface Pin Out                 | 9  |

| J4 TFT Digital Interface signal description      | 10 |

| Chapter 2 BIOS Setup                             | 11 |

| CPU-1432 BIOS Menu                               |    |

| CPU-1432 BIOS Flat Panel parameters              | 12 |

| Defining CPU-1432 BIOS parameters                | 12 |

| Timings Diagrams                                 | 14 |

| Chapter 3 Connecting the TFT-LCD to the CPU-1432 | 16 |

(This page is intentionally left blank.)

## Chapter 1 CPU-1432 TFT Digital Interface

This brief application note contains information about using the CPU-1432 TFT digital interface. The goal is to help users properly connect TFT-LCD panels to the CPU-1432.

## **TFT Digital Interface Overview**

The CPU-1432 allows you to connect various models of LCD-TFT panels via its J4 connector. The following table shows the supported LCD-TFT video resolutions

| Resolution | Simultaneous<br>Colours | Refresh Rate<br>(Hz) |

|------------|-------------------------|----------------------|

| 640x480    | 8bpp 256 colours        | 60                   |

| 640x480    | 16bpp 64K colours       | 60                   |

| 800x600    | 8bpp 256 colours        | 60                   |

| 800x600    | 16bpp 64K colours       | 60                   |

| 1024x768   | 8bpp 256 colours        | 60                   |

| 1024x768   | 16bpp 64K colours       | 60                   |

Table 1. LCD-TFT video resolutions (\*)

(\*)- This list is not meant to be a complete list of all the possible supported TFT video

For further info about other/new supported LCD-TFT flat panels, please contact the Eurotech Customer Support Service.

#### **J4 TFT Digital Interface Connector**

The TFT digital interface is accessible via the J4 connector, which is a 20x2 pitch 1.25mm SMT connector.

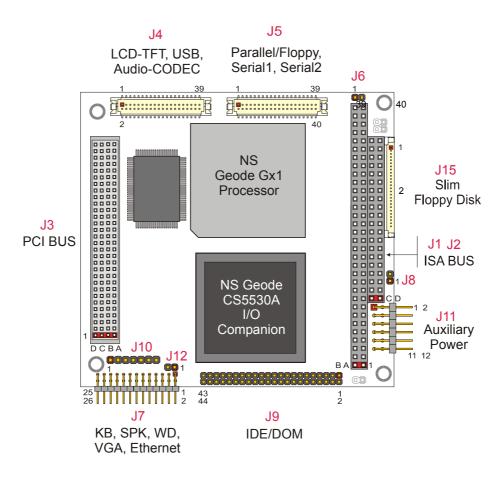

Figure 1. Connectors layout

The following table shows the J4 connector type and its matching models:

| Connector Reference        | Connector Type         |

|----------------------------|------------------------|

| J4 Used Connector          | Hirose DF13-40DP-1.25V |

| J4 Corresponding connector | Hirose DF13-40DS-1.25C |

Table 2. J4 mating connectors

For futher information about connectors (electrical, mecanical, ...), please refer to the Hirose website (<a href="http://www.hirose.com/">http://www.hirose.com/</a>) referring to the DF13 connector family.

## **J4 TFT Digital Interface Pin Out**

The following table describes the signals of the J4 TFT Digital Interface connector:

| PIN | SIGNAL            | SIGNAL       | PIN | <b>FUNCTION</b> |

|-----|-------------------|--------------|-----|-----------------|

| 1   | GND               | Dot Clock    | 2   |                 |

| 3   | GND               | RED5 (MSB)   | 4   |                 |

| 5   | Data Enable       | RED4         | 6   |                 |

| 7   | RED3              | RED2         | 8   |                 |

| 9   | RED1              | RED0 (LSB)   | 10  |                 |

| 11  | BLUE5 (MSB)       | VDD Enable   | 12  |                 |

| 13  | BLUE4             | BLUE3        | 14  | LCD-TFT         |

| 15  | BLUE2             | BLUE1        | 16  |                 |

| 17  | BLUE0 (LSB)       | GREEN5 (MSB) | 18  |                 |

| 19  | Back Light enable | GREEN4       | 20  |                 |

| 21  | GREEN3            | GREEN2       | 22  |                 |

| 23  | GREEN1            | GREEN0 (LSB) | 24  |                 |

| 25  | FP_VSYNC          | FP_HSYNC     | 26  |                 |

| 27  | GND_USB           | USBDP        | 28  | USB             |

| 29  | USBDN             | VDD_USB      | 30  | ООВ             |

| 31  | PC_BEEP           | VDD_CODEC    | 32  |                 |

| 33  | SDATA_OUT         | RSTDRV       | 34  | ALIDIO          |

| 35  | SDATA_IN          | SYNC         | 36  | AUDIO-<br>CODEC |

| 37  | GND1_CODEC        | AC97_CLK     | 38  |                 |

| 39  | GND2_CODEC        | BITCLK       | 40  |                 |

Table 3. J4 TFT Digital Interface connector pinout

For further information about the physical layout of the J4 connector please refer to the Figure 1 layout.

This information is intended to help the user properly build the cable used to connect the Digital interface of the CPU-1432 with the TFT LCD panel selected.

Reducing the cable length can allows users to reduce possible interference to the TFT LCD digital signals.

## J4 TFT Digital Interface signal description

The digital TFT interface signals are described in the following table:

| SIGNAL NAME         | Description                                                                                                                            | <b>Electrical Characteristics</b> |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Dot Clock           | Pixel Port Clock Dot Clock is the pixel dot clock output. It clocks the pixel data.                                                    | TTL 8mA $V_{HMAX}$ = 3.3 $V$      |

| FP_HSYNC            | Flat Panel Horizontal Sync Flat Panel Horizontal Sync establishes the line rate and horizontal Retrace interval for a TFT display.     | TTL 8mA V <sub>HMAX</sub> = 3.3V  |

| FP_VSYNC            | Flat Panel Vertical Sync Flat Panel Vertical Sync establishes the screen refresh rate and vertical retrace interval for a TFT display. | TTL 8mA V <sub>HMAX</sub> = 3.3V  |

| ENA_DISP            | Display Enable indicates the active display portion of a scan line.                                                                    | TTL 8mA V <sub>HMAX</sub> = 3.3V  |

| VDD ENABLE          |                                                                                                                                        | TTL 8mA $V_{HMAX} = 3.3V$         |

| DATA ENABLE         | This is a data valid signal                                                                                                            | TTL 8mA $V_{HMAX} = 3.3V$         |

| BACKLIGHT<br>ENABLE | This is a useful signal which allow you to control the switching on-off of the lamps                                                   | TTL 8mA $V_{HMAX}$ = 3.3 $V$      |

| RED[5:0]            | Graphics Red Pixel Data Bus This bus drives graphics pixel data synchronous to the Dot Clock output.                                   | TTL 8mA V <sub>HMAX</sub> = 3.3V  |

| GREEN[5:0]          | Graphics Green Pixel Data Bus This bus drives graphics pixel data synchronous to the Dot Clock output.                                 | TTL 8mA V <sub>HMAX</sub> = 3.3V  |

| BLUE[5:0]           | Graphics Blue Pixel Data Bus This bus drives graphics pixel data synchronous to the Dot Clock output.                                  | TTL 8mA V <sub>HMAX</sub> = 3.3V  |

| GND                 | Ground                                                                                                                                 | Ground                            |

Table 4. Signal Description - Electrical Characteristics

## Chapter 2 BIOS Setup

To enable the TFT Digital Interface functionality, the user should properly configure the BIOS settings. This section illustrates the BIOS settings the user is allowed to modify for properly controlling the LCD-TFT. For further information on how to use the BIOS functionality, please refer to the CPU-1432 user manual.

#### CPU-1432 BIOS Menu

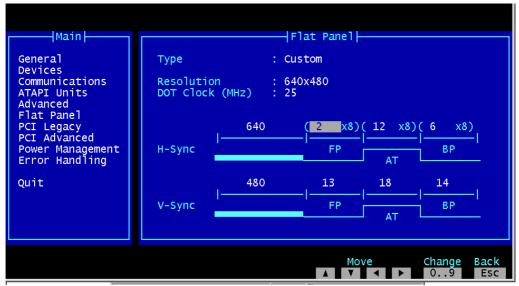

After entering BIOS setup by pressing the F2 Key during the boot time, select the Flat Panel menu using cursors. You will be prompted to the following menu:

Figure 2. BIOS setup - Flat Panel section

#### **CPU-1432 BIOS Flat Panel parameters**

Here a brief description of each field the user is allowed to modify from the BIOS setup program and its default value:

| Field           | De                                  | Default<br>Value  |          |

|-----------------|-------------------------------------|-------------------|----------|

| Туре            | Disabled                            | Disabled          |          |

|                 | Custom                              | Custom parameters |          |

|                 | Hitachi 800x600 (38MHz)             |                   | Disabled |

|                 | LG 800x600 (38MHz)                  |                   | Disabled |

|                 | NEC 800x600 (38MHz)                 |                   |          |

|                 | Sharp 800x600 (40MHz)               |                   |          |

| Resolution      | 640x480 Select the proper graphical |                   |          |

|                 | 800x600                             | resolution        | 640x480  |

|                 | 1024x768                            | 1 George Grand    |          |

| Dot Clock (MHz) | Dot Clock Frequency in MF           | 0                 |          |

| HSync FP        | Front Porch - Horizontal Sy         | 0                 |          |

| HSync AT        | Active Time - Horizontal Sy         | 0                 |          |

| HSync BP        | Back Porch - Horizontal Sy          | 0                 |          |

| VSync FP        | Front Porch - Vertical Sync         | 0                 |          |

| VSync AT        | Active Time - Vertical Sync         |                   |          |

| VSync BP        | Back Porch - Vertical Sync          |                   |          |

Table 5. BIOS Flat Panel Section Options

To properly enter the parameters, the user should analyze the information contained in the TFT-LCD datasheet that the user wishes to connect to the CPU-1432 and insert the data for the various fields.

Sometimes, if connecting both a CRT and TFT-LCD devices, the image shown on the CRT is rescaled and shifted because the parameters for the TFT interface modify the video settings.

### **Defining CPU-1432 BIOS parameters**

To enter the proper parameters into the Flat Panel BIOS settings, refer to the TFT-LCD datasheet. Table 6 shows an example of a timing table referring to a 640x480 TFT-LCD.

| Parameter          |                    | Symbol | Min. | Тур.   | Max. | Unit              | Remarks                 |

|--------------------|--------------------|--------|------|--------|------|-------------------|-------------------------|

| CLK                | Frequency          | 1/to   | 21.0 | 25.175 | 29.0 | MHz               | 39.722 ns (Typ.)        |

|                    | Duty               | tch/tc | 0.4  | 0.5    | 0.6  | -                 | -                       |

|                    | Rise, fall         | terf   | -    | -      | 10   | ns                | -                       |

| Hsync              | Period             | th     | 30.0 | 31.778 | 33.6 | μs                | 31.469 kHz (Typ.)       |

|                    |                    |        | -    | 800    | -    | CLK               |                         |

|                    | Display period the |        |      | 640    |      | CLK               | -                       |

|                    | Front-porch        | thf    | 16   |        | CLK  | Fixed timing mode |                         |

|                    |                    |        | 2    | 16     | -    | CLK               | DE mode                 |

|                    | Pulse width        | thp*   | 10   | 96     | -    | CLK               | Fixed timing mode       |

|                    |                    |        | 10   | 96     | -    | CLK               | DE mode                 |

|                    | Back-porch         | thb*   | 4    | 48     | -    | CLK               | Fixed timing mode       |

|                    |                    |        | 4    | 48     | -    | CLK               | DE mode                 |

|                    | thp                | + thb* |      | 144    |      | CLK               | Fixed timing mode       |

|                    |                    |        | 14   | 144    | -    | CLK               | DE mode                 |

|                    | CLK-Hsync timing   | thch   | 12   | -      | -    | ns                | -                       |

|                    | Hsync-CLK timing   | thes   | 8    | -      | -    | ns                | -                       |

|                    | Hsync-Vsync timing | tvh    | 1    | -      | -    | CLK               | 1CLK = 39.722 ns (Typ.) |

|                    | Vsync-Hsync timing | tvs    | 30   | -      | -    | ns                | -                       |

|                    | Rise, fall         | thrf   | -    | -      | 10   | ns                | -                       |

| Vsync              | Period             | tv     | 16.1 | 16.683 | 17.2 | ms                | 59.94 Hz (Typ.)         |

|                    |                    |        | -    | 525    | -    | Н                 |                         |

| Display period     |                    | tvd    | 480  |        | Н    | -                 |                         |

|                    | Front-porch        | tvf    |      | 12     |      | Н                 | Fixed timing mode       |

|                    |                    |        | 1    | 12     | -    | Н                 | DE mode                 |

|                    | Pulse width        | tvp*   | 1    | 2      | -    | Н                 | Fixed timing mode       |

|                    |                    |        | 1    | 2      | -    | Н                 | DE mode                 |

|                    | Back-porch         | tvb*   | 4    | 31     | -    | Н                 | Fixed timing mode       |

|                    |                    |        | 4    | 31     | -    | Н                 | DE mode                 |

|                    | tvp + tvb*         |        |      | 33     |      | Н                 | Fixed timing mode       |

|                    |                    |        | 5    | 33     | -    | Н                 | DE mode                 |

|                    | Rise, fall         |        | -    | -      | 10   | ns                | -                       |

| DATA               | CLK-DATA timing    | tds    | 8    | -      | -    | ns                | -                       |

| R0 - R5<br>G0 - G5 | DATA-CLK timing    | tdh    | 12   | -      | -    | ns                | -                       |

| B0 - B5            | Rise, fall         | tdrf   | -    | -      | 10   | ns                | -                       |

| DE                 | DE-CLK timing      | tes    | 8    | -      | -    | ns                | DE mode                 |

|                    | CLK-DE timing      | teh    | 12   | -      | -    | ns                |                         |

|                    | Rise, fall         | terf   | -    | -      | 10   | ns                |                         |

Table 6. Timing Characteristic Example for a TFT-LCD

The following instructions are an example showing how to define the values to enter into the Flat Panel BIOS setup according to the timing characteristics in Table 6.

| BIOS Field      | <b>BIOS Value</b> | Notes                                                                                                                                                       |

|-----------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Туре            | Custom            | We would enter custom parameters                                                                                                                            |

| Resolution      | 640x480           | Obtained from the TFT-LCD Data Sheet, this is a characteristic.                                                                                             |

| Dot Clock (MHz) | 25                | Referring Table 6 CLK (1/Tc) Typical value. The reported value 25.175MHz is approximated to 25Mhz                                                           |

| HSync FP        | 2                 | Referring Table 6 HSync Front Porch (thf) Typical value. The reported value 16CLK. So the value you've to enter the BIOS is 2 to obtain 16 = ( 2 x 8 )      |

| HSync AT        | 12                | Referring Table 6 HSync Pulse width (thp*) Typical value. The reported value 96CLK. The value you've to enter the BIOS is 12 to obtain $96 = (12 \times 8)$ |

| HSync BP        | 6                 | Referring Table 6 HSync Pulse Back-porch (thb*) Typical value. The reported value 48CLK. The value you've to enter the BIOS is 6 to obtain 48 = ( 6 x 8 )   |

| VSync FP        | 12                | Referring Table 6 VSync Front Porch (tvf) Typical value. The reported value 12CLK.                                                                          |

| VSync AT        | 2                 | Referring Table 6 VSync Pulse width (tvp*) Typical value. The reported value 2 H.                                                                           |

| VSync BP        | 31                | Referring Table 6 VSync Back Porch (thb*) Typical value. The reported value 31CLK.                                                                          |

Table 7. Flat Panel BIOS parameters

## **Timings Diagrams**

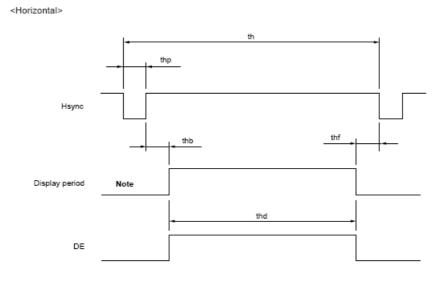

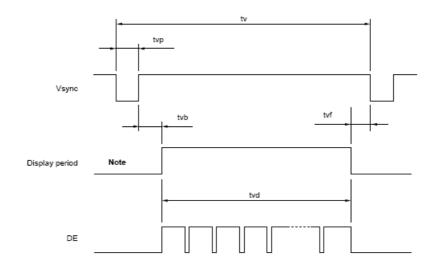

The followings images show a graphical mode to represent timing data. The information is not represented in the same graphical order shown into the Flat Panel BIOS setup, but the contents are the same.

Figure 3. Timing Diagram Horizontal Mode

<Vertical>

Figure 4. Timing Diagram Vertical Mode

The previous figures may be useful to graphically verify if the entered BIOS parameters match the TFT timing diagram.

Regarding the timing, the following relationships should be ensured:

Horizontal Sync.:

Period (th) = Display Period (thd) + Front Porch (thf) + Pulse Width (thp\*) + Back Porch (thb\*)

Vertical Sync. :

Period (tv) = Display Period (tvd) + Front Porch (tvf) + Pulse Width (tvp\*) + Back Porch (tvb\*)

Practically, referring to Table 6 and to Table 7, the results are:

Horizontal Sync : 800 = 640 + 16 + 96 + 48

Vertical Sync : 525 = 480 + 12 + 31 + 2

# **Chapter 3** Connecting the TFT-LCD to the CPU-1432

This section contains a brief checklist of the actions to perform before connecting a TFT-LCD to the CPU-1432.

- Download all information about the TFT-LCD module and its inverter selected;

- □ Verify that the resolution of the TFT panel is compatible with and suppported by the resolution shown in Table 1 of this Application note;

- □ Read carefully the TFT-LCD datasheet, in particular the Electrical Characteristics that must be compatible with the electrical interface of the CPU-1432 TFT LCD interface referred to in Table 4;

- □ Consulting the TFT-LCD datasheet and the Table 3 CPU-1432 connector pin-out, write a table with the connections between the J19 CPU-1432 connector and the TFT-LCD selected; this may be useful when building the connection cable;

- □ Consulting the TFT-LCD inverter datasheet and Table 3 CPU-1432 connector pin-out, make the proper cable.

- □ Refer to the TFT-LCD input signal timing datasheet section to detect the parameters to insert into the CPU-1432 BIOS Flat Panel section and calculate it as described in the Chapter 2 BIOS Setup.

- □ To connect the system, carefully verify the connections cable, the BIOS settings and all the information to prevent erroneous damages to the system.

- After you've verified the information, power up the system verifying all information is properly displayed on the TFT-LCD module. Try some graphical test programs to detect the functionality of the images.