These service instructions are for use by qualified personnel. If nontechnical CVI owners suspect that the unit has degraded, or that some functions are not working, perform the self diagnostic tests (Video menu 9) first then report error messages to your distributor.

Copyright 1986, Fairlight Instruments Pty. Ltd.

All rights reserved.

Contents of this publication may not be reproduced in any form without the written permission of Fairlight Pty Ltd.

Specifications are subject to continual change and enhancement and Fairlight reserves the right to alter specifications without notice

Fairlight Pty Ltd., 15 Boundary Street, Rushcutters Bay, N.S.W 2011 Sydney, Australia

Phone: (02) 331 6333, Telex: 27998 'FAIRLT'

\_tairlight\_

| System Overview             |   |

|-----------------------------|---|

| Main Board<br>Control Board | 2 |

| Video Board - PAL           | 3 |

| Video Board - NTSC          | 4 |

| BNC Connector Board         | 5 |

| Power Supply                | 6 |

| Exploded Diagrams           |   |

• .

# System Overview

#### **CONTENTS**

| Technical specifications | *************************************** | 1.2 |

|--------------------------|-----------------------------------------|-----|

| System Block Diagram     | •••••                                   | 1.3 |

| Introduction and system  | overview                                | 1.4 |

**\$**

### SPECIFICATIONS

Video standard:

NTSC or PAL compatible (note 1).

Field store:

256 x 256 pixels, 14 bit planes, 4096 colours (note 2).

Memory:

128 Kbytes RAM, 32 Kbytes ROM.

Processor:

2MHz 6809.

Communications:

RS232C port (300 - 19200 baud). Internal functions can be

accessed and controlled by ASCII codes.

Expansion:

Processor expansion bus, Digital video cascade in and out.

Composite video inputs:

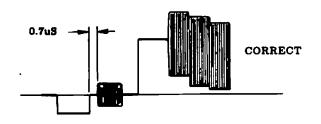

x2, 1Vp-p, loop through x2, 0.7Vp-p, loop through

RGB inputs:

1Vp-p, 75 ohms (note 3).

Composite video output:

RGB output:

0.7Vp-p, 75 ohms.

Stencil (key/matte) in:

0.7V dc slicing level.

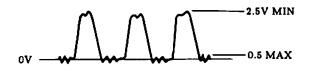

Stencil out:

2Vp-p, 75 ohms.

Resolution:

> 300 lines (composite in - composite out).

256 pixels per line (field store).

Delay:

1300 ns (composite in - composite out).

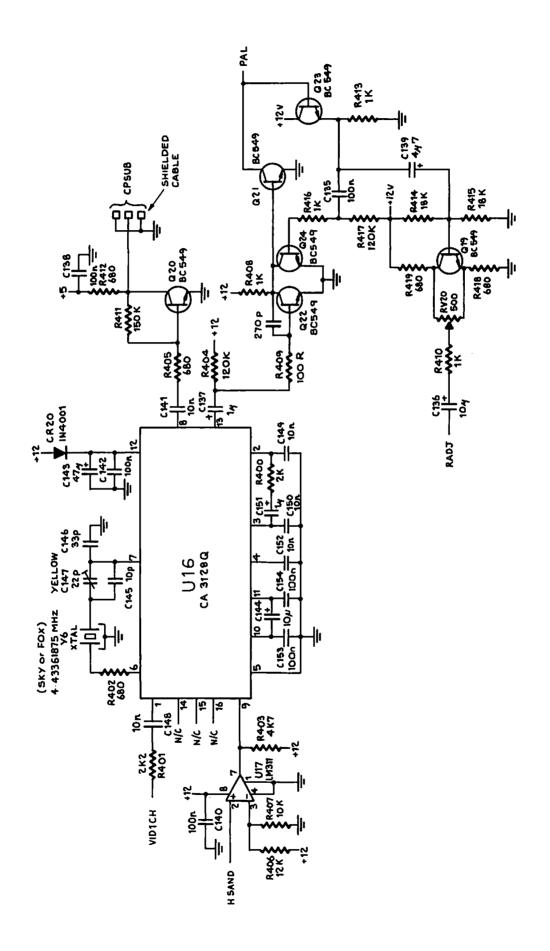

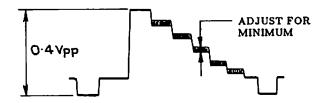

Subcarrier:

Internally generated or external input (loop through)

1V to 4V p-p. 0 - 360 degree phase control.

Synchronization:

Internally generated for stand-alone use. Auto external sync to

composite video I input.

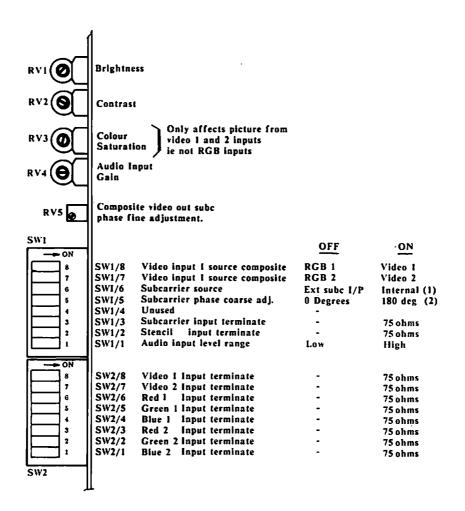

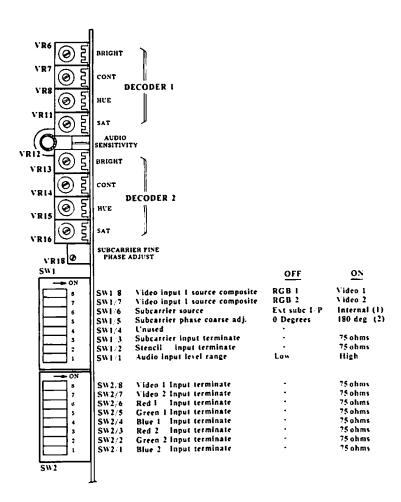

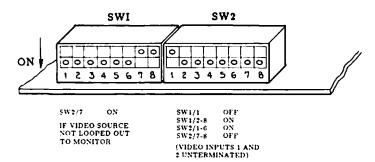

Termination:

Switchable 75 ohm termination inbuilt on all video inputs.

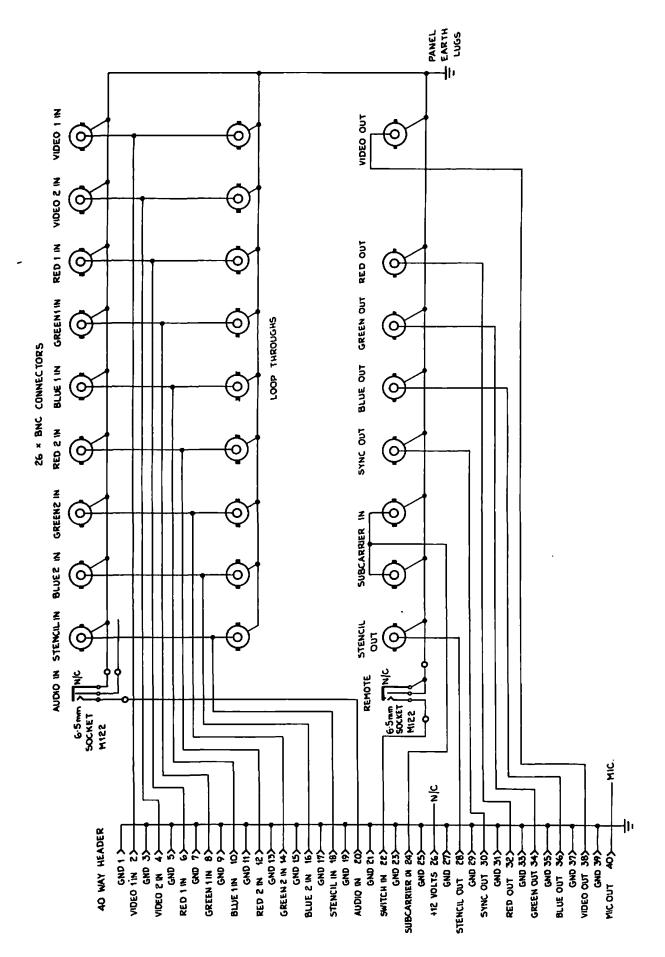

Video connections:

Full complement of BNC connectors (26).

Audio input:

Internal mic, external mic or line. 40W (100 - 120 or 200 - 240 volts).

Power: Dimensions and Weight:

Control panel: 428(W)x178(H)x25(D) mm.

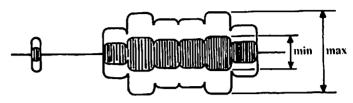

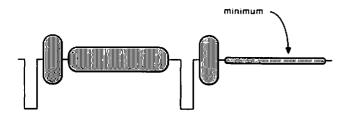

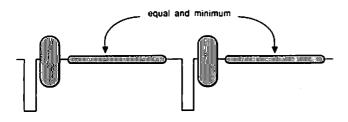

Multicore cable between control panel and electronics unit.

Standard length: 2m optional: 5, 10 or 20m.

Standard EIA rack size, 4 units. 1Kg.

Remote electronics unit: 482(W)x133(H)x270(D) mm.

Standard EIA rack size, 3 units. 6kg.

#### Please note:

- (1) In PAL systems field store displays only 256 lines. This will normally be visible as 3 to 5 black lines at the top and bottom of the digitally stored picture, depending on the monitor vertical scanning adjustments.

- (2) CVI will not squeeze or zoom LIVE images.

- (3) If used in a studio installation where the CVI output is to be mixed with other sources, or where broadcast style output is required, an external PAL/NTSC coder and SPG should be used.

- These specifications are subject to change and are presented as a guide only.

**RACK MOUNT UNIT**

# INTRODUCTION AND SYSTEM OVERVIEW

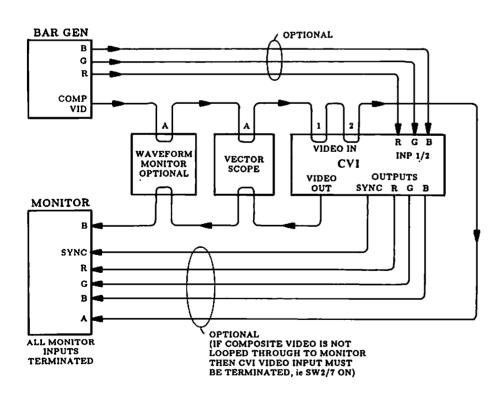

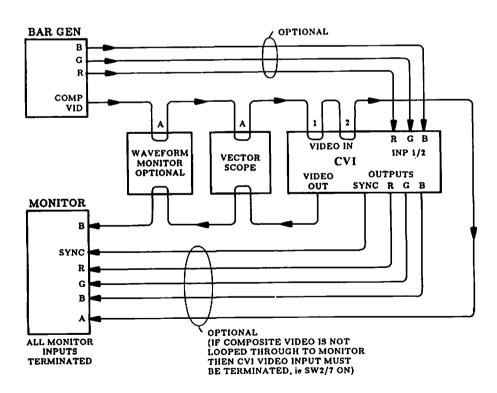

The Computer Video Instrument is a computer controlled field store. It is compatible with either PAL or NTSC systems and can be used with most video sources including cameras, VTR's and VCR's. Two genlocked RGB or composite video inputs can be used. Composite and RGB outputs are provided.

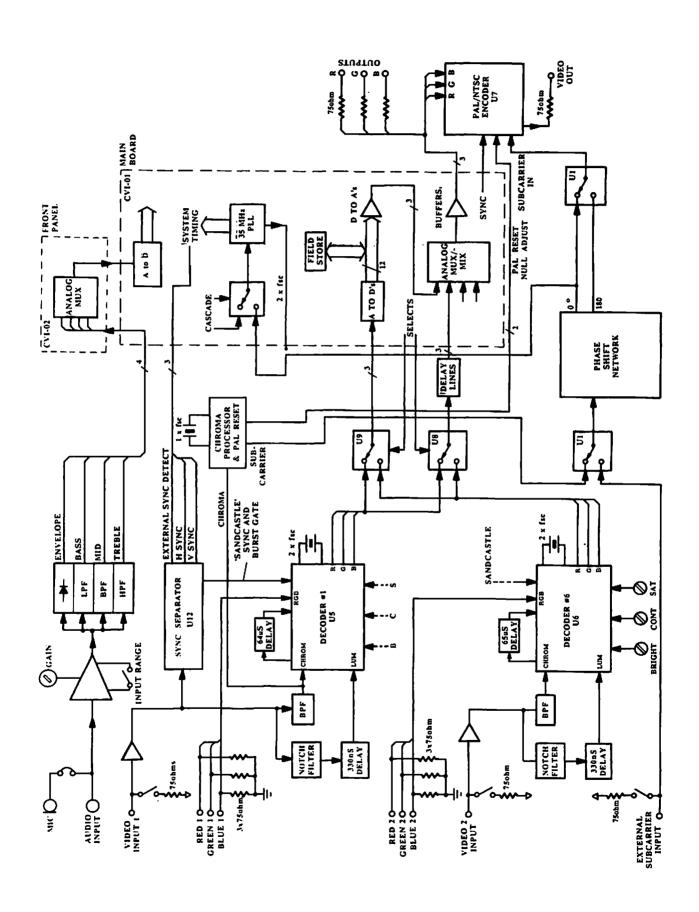

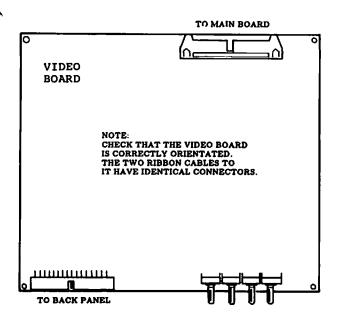

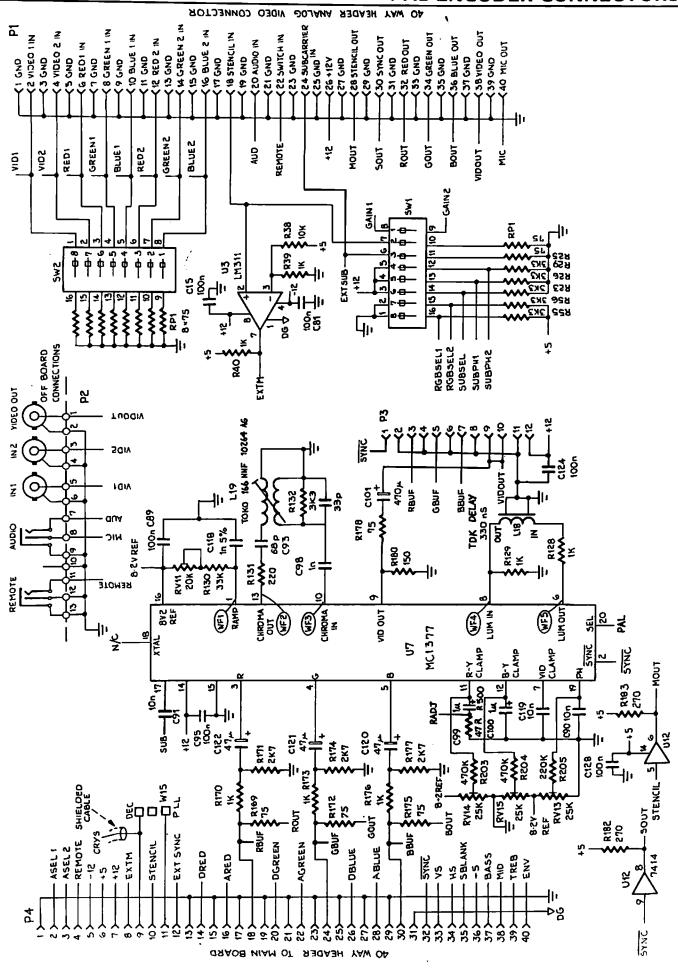

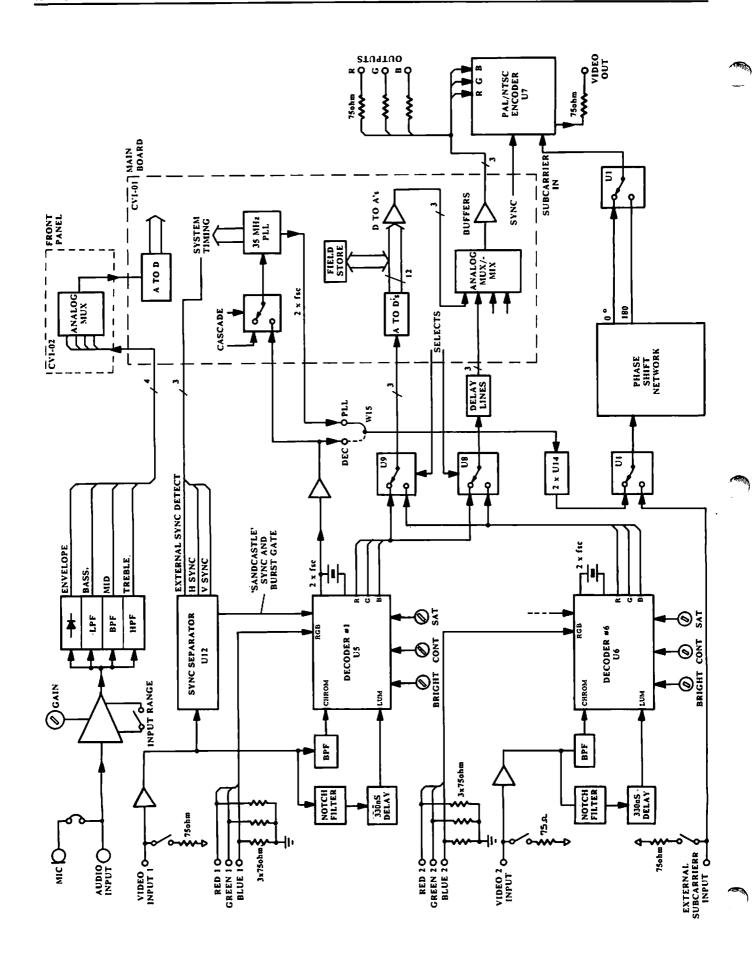

The video signal is processed initially on the Video Board before being sent to the Main switching/mixing or processing. The signal is then returned to the Video Board for further processing before being output.

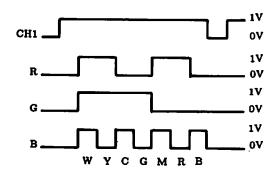

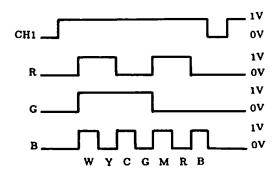

The system uses separated red, green and blue colour components for processing by the computer instead of luminance and colour difference components used in other digital video systems. This reduces the amount of computation necessary. RGB component signals are therefore used throughout the system in both analog and digital form.

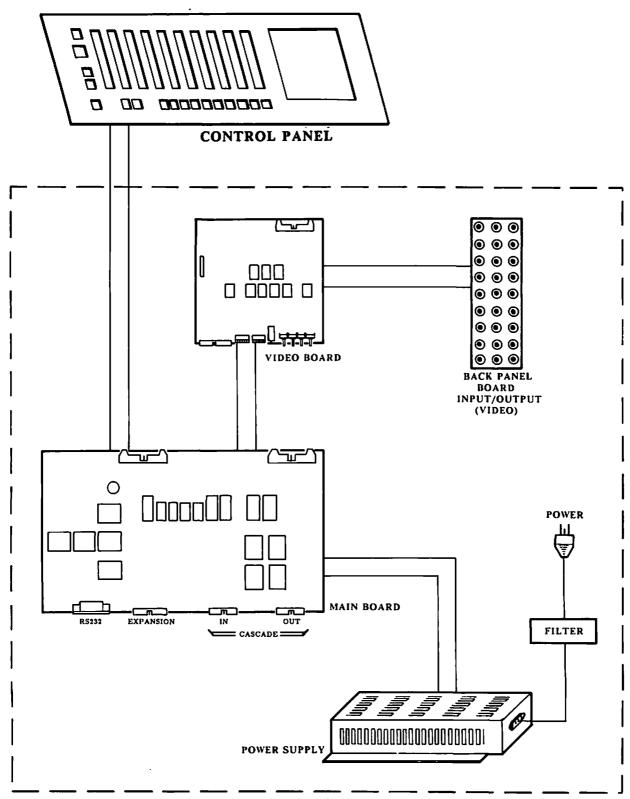

The system comprises five main sections: Video Board, Main Board, BNC Connector Board, Control Panel and Power Supply.

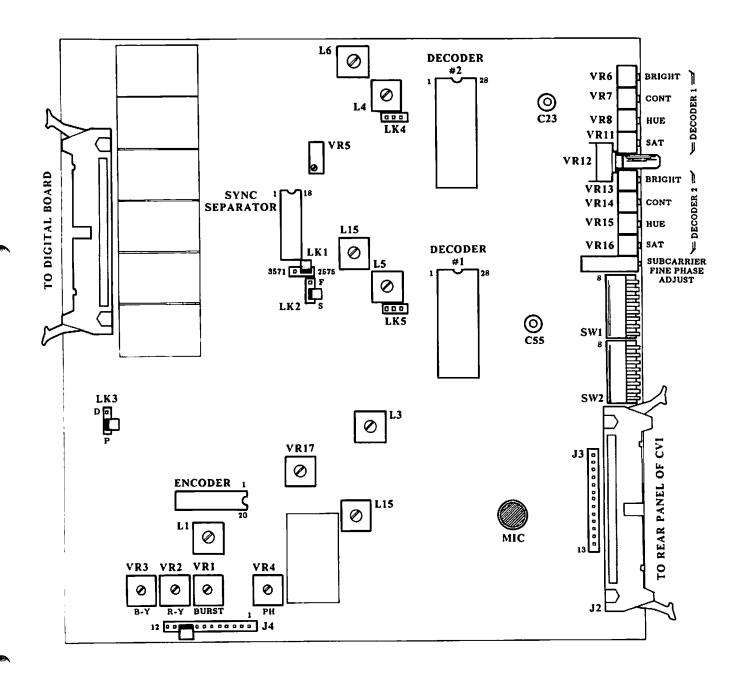

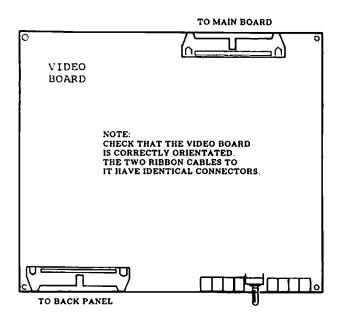

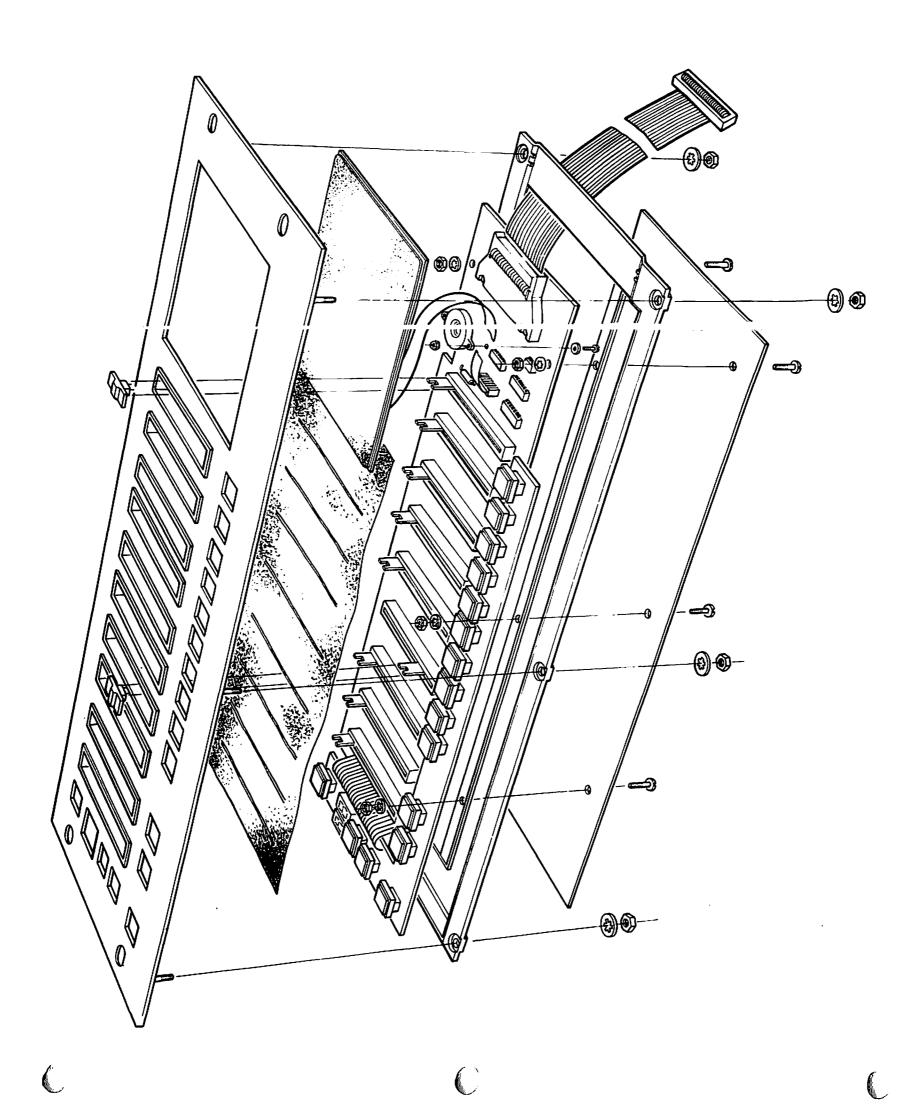

The CVI is housed in a standard 19" rackmounting case. The Video Board and Power Supply Assembly are mounted on the top of the central tray which slides out for servicing and adjustment. The Main Board is mounted on the underside of this tray. The BNC Connector Board is mounted on the back panel. The Control Panel is housed in a separate rack-mounting assembly.

Separate PAL and NTSC versions of the Video Board are available. The Main Board. Control Panel, BNC Connector Board and Power Supply are used for both TV standards.

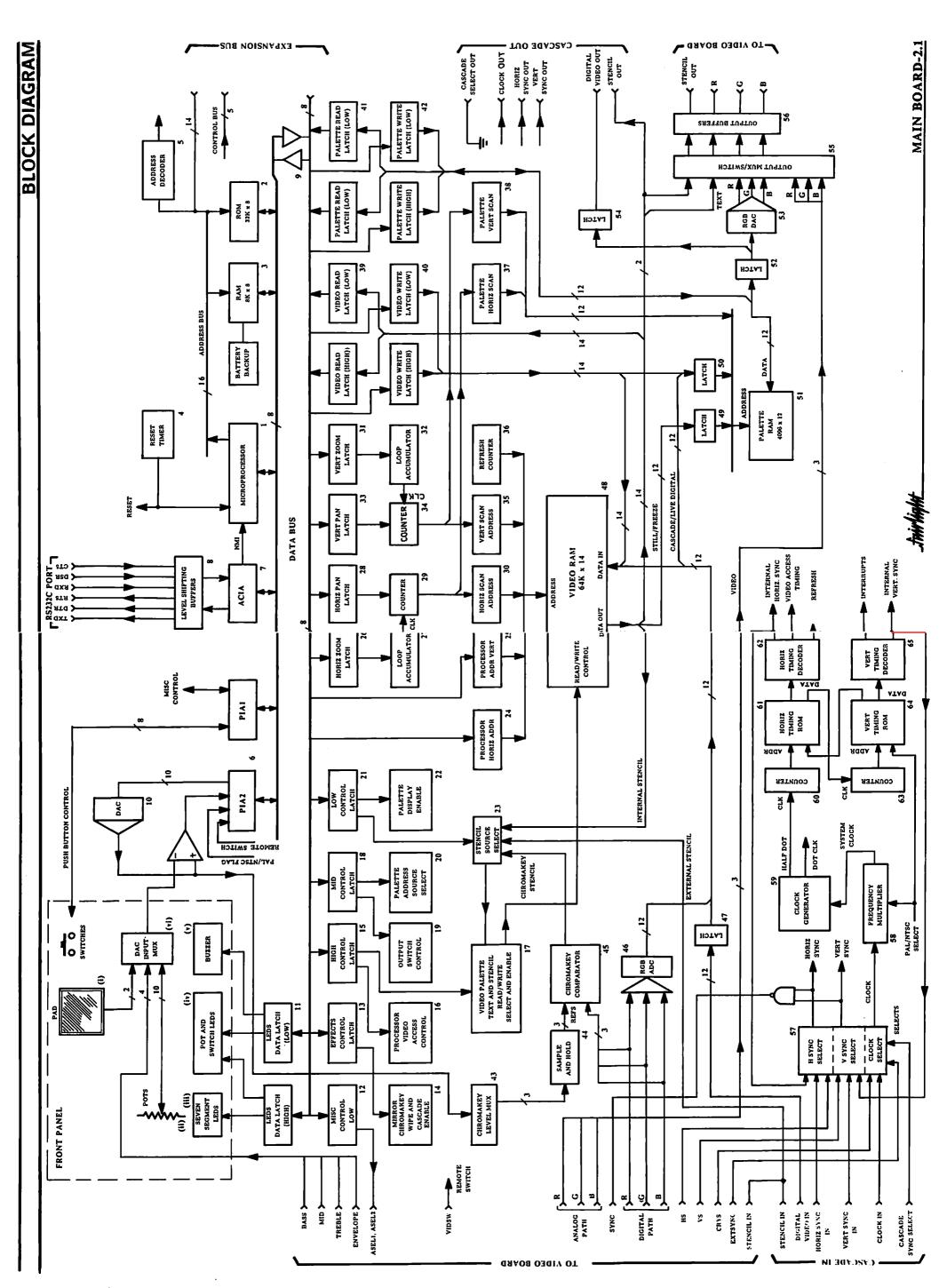

The functions of each are now described. Refer to the block diagram.

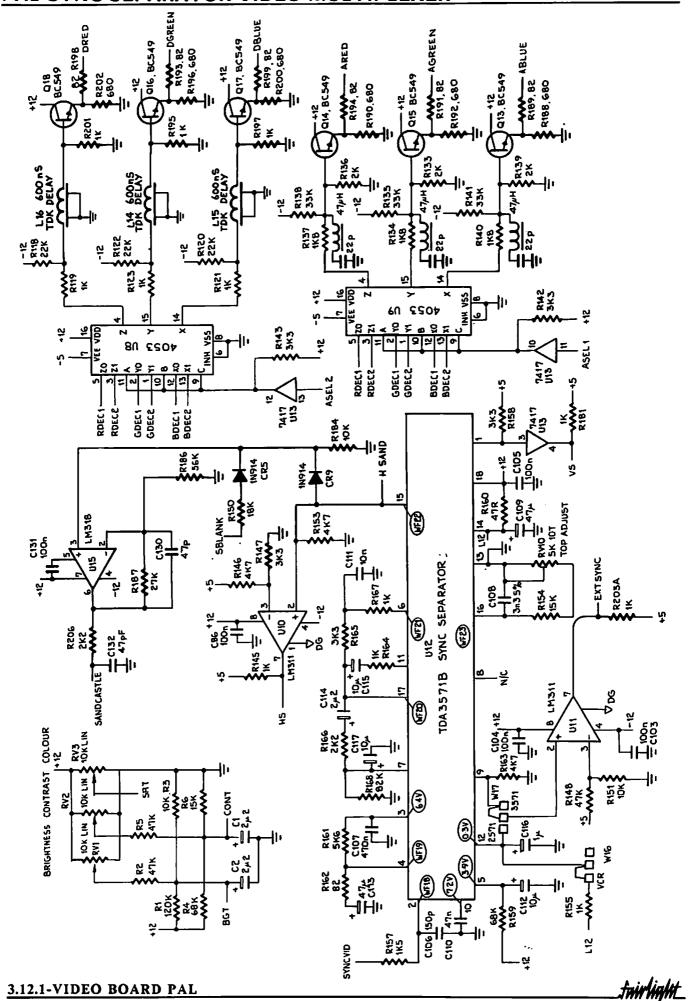

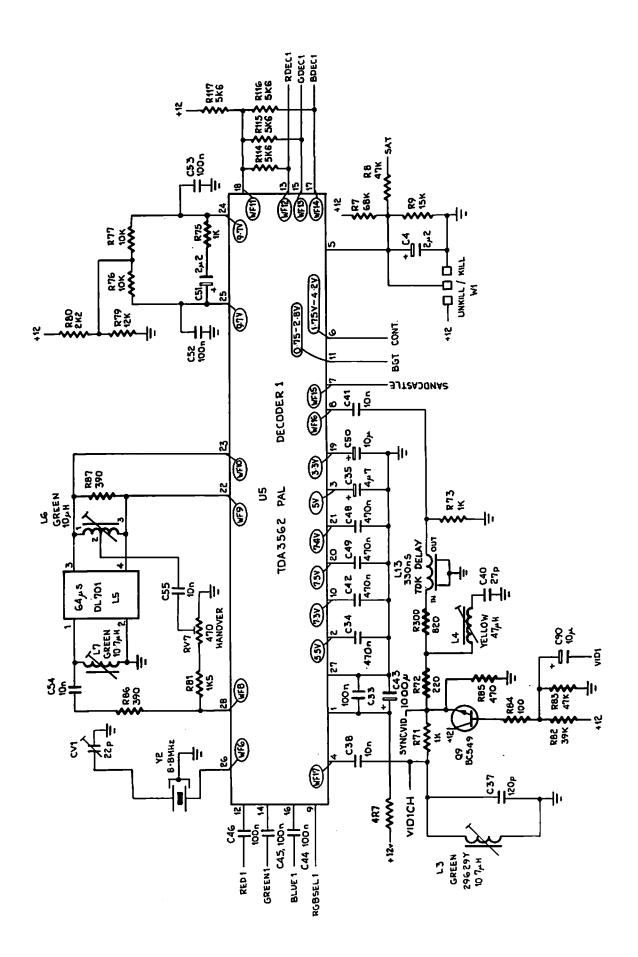

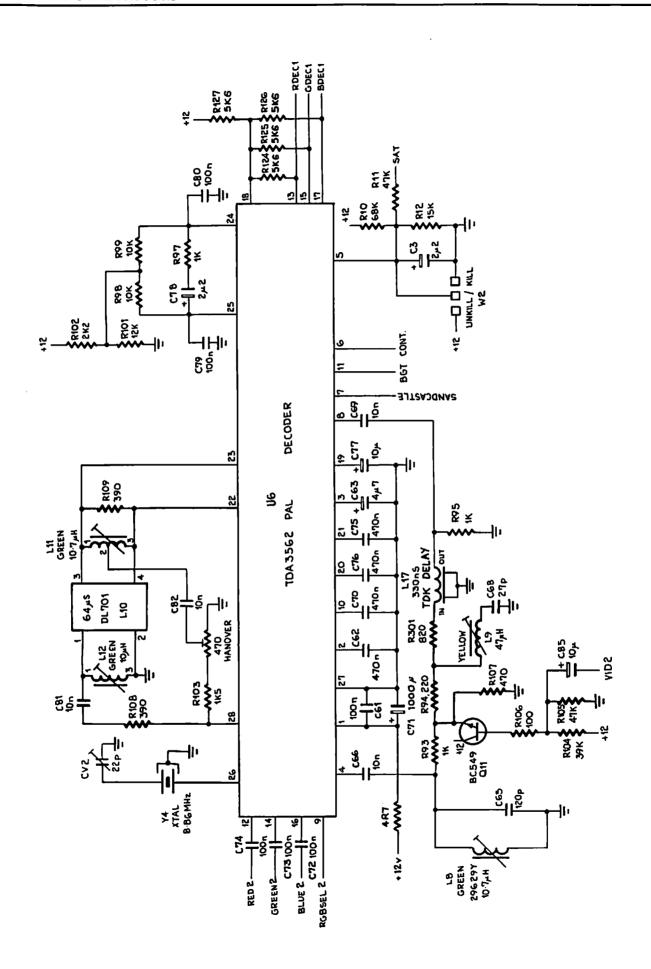

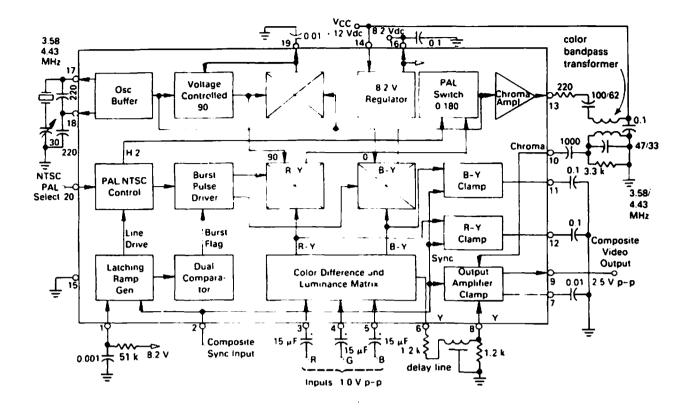

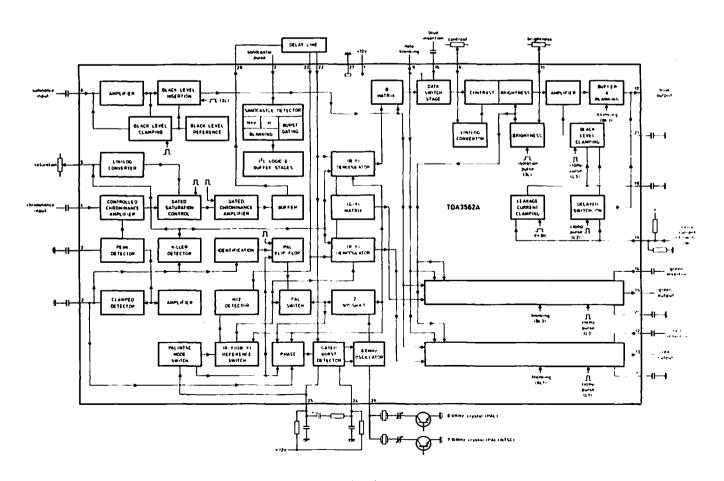

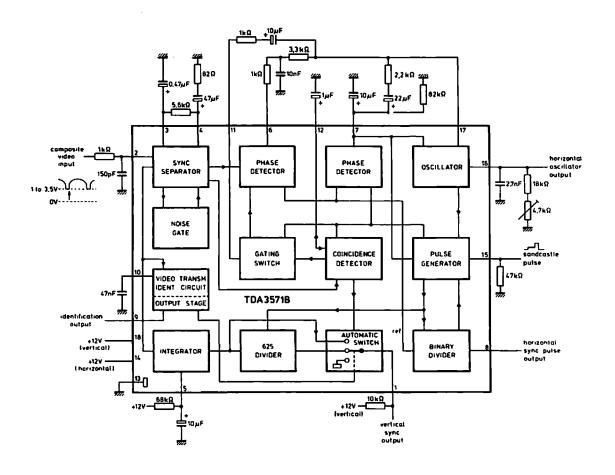

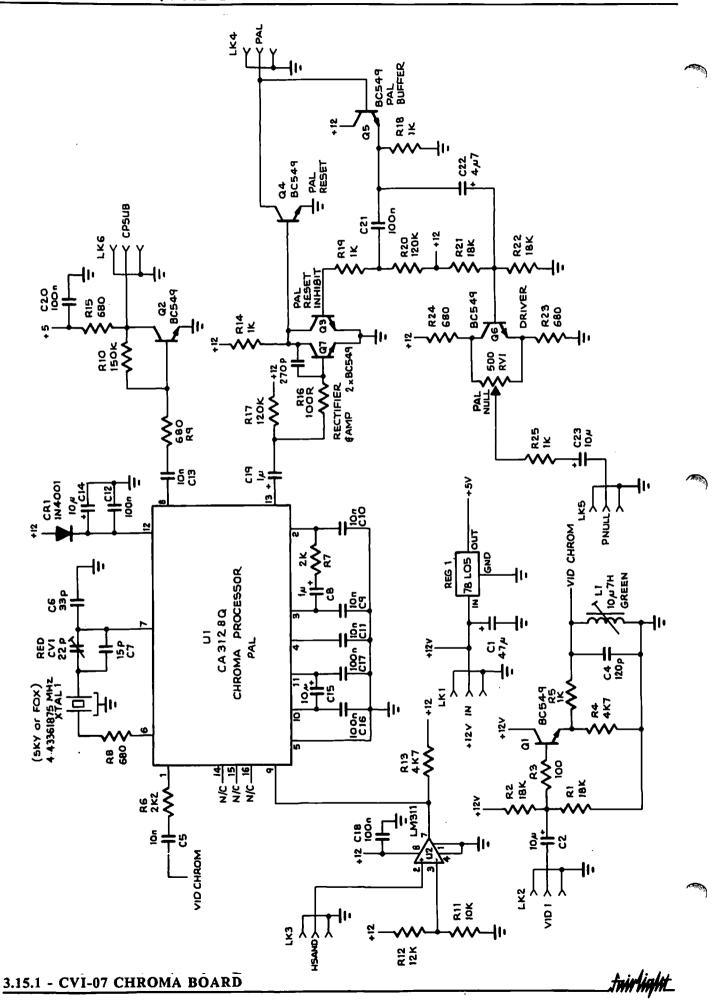

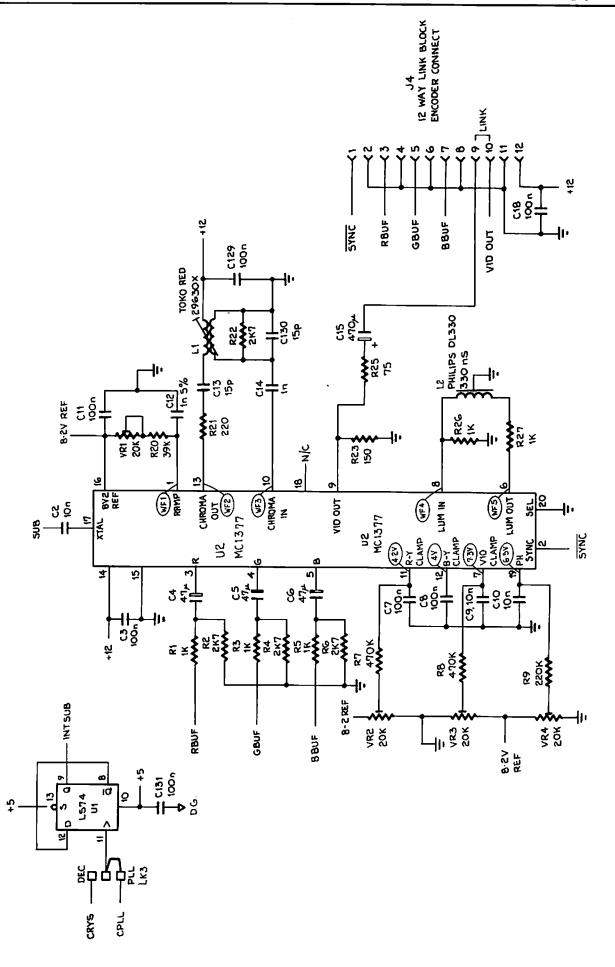

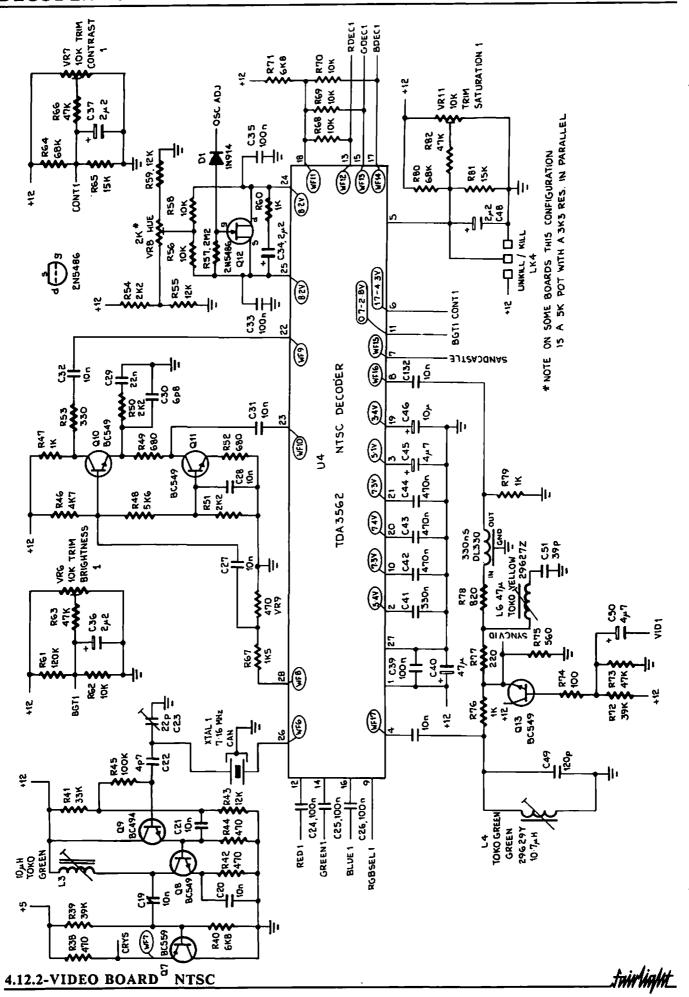

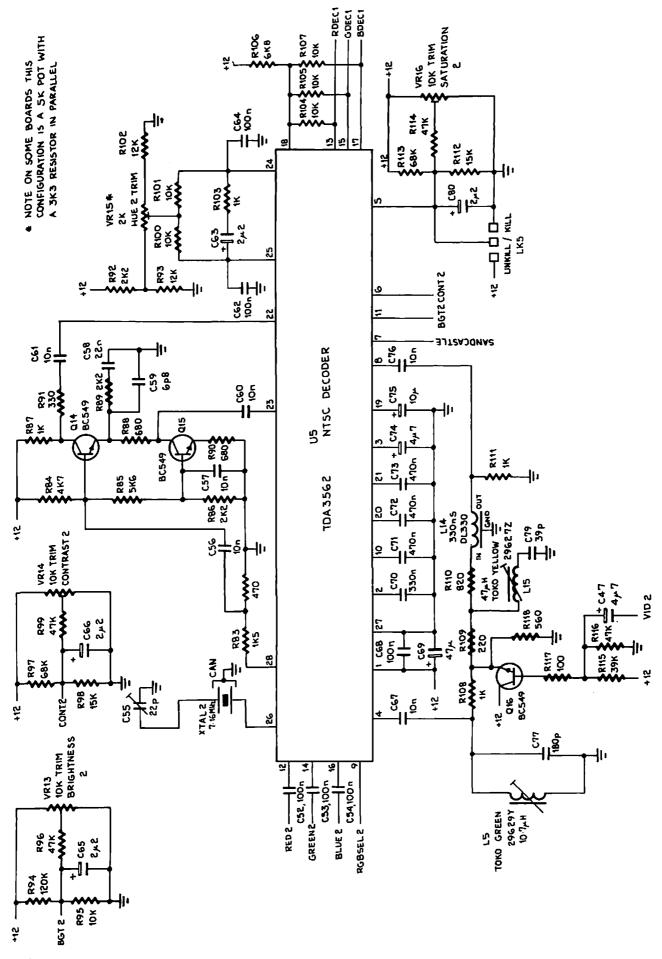

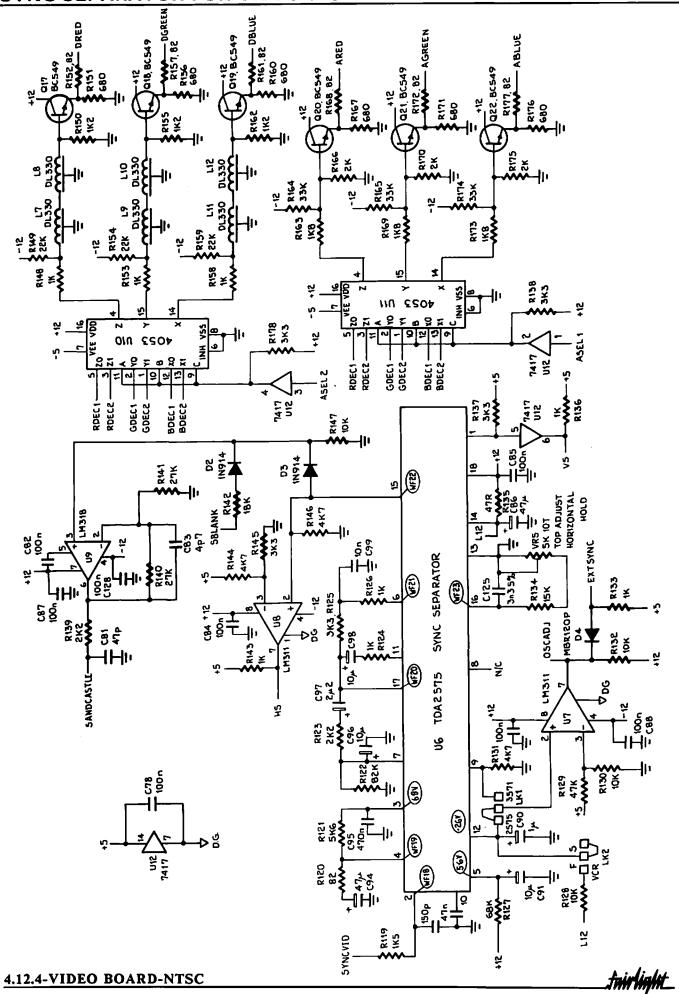

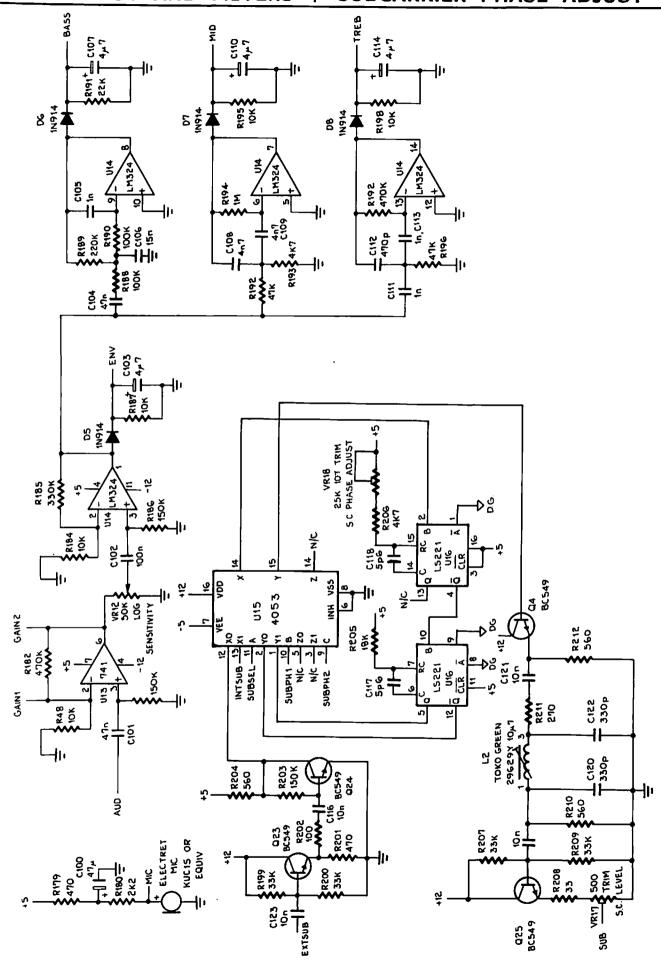

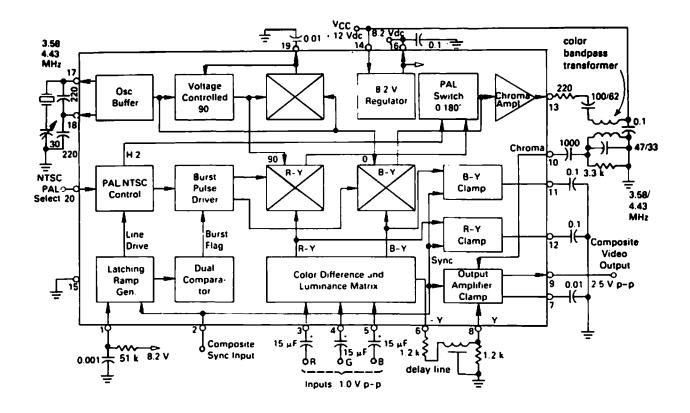

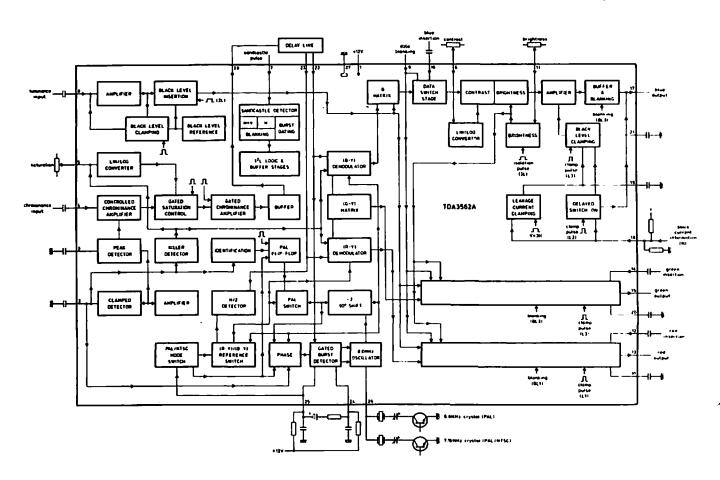

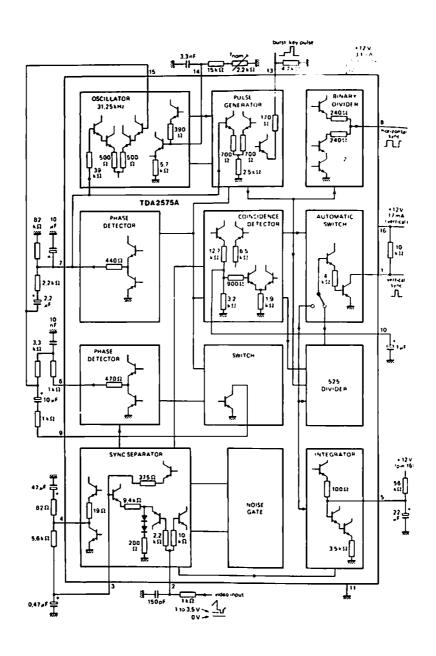

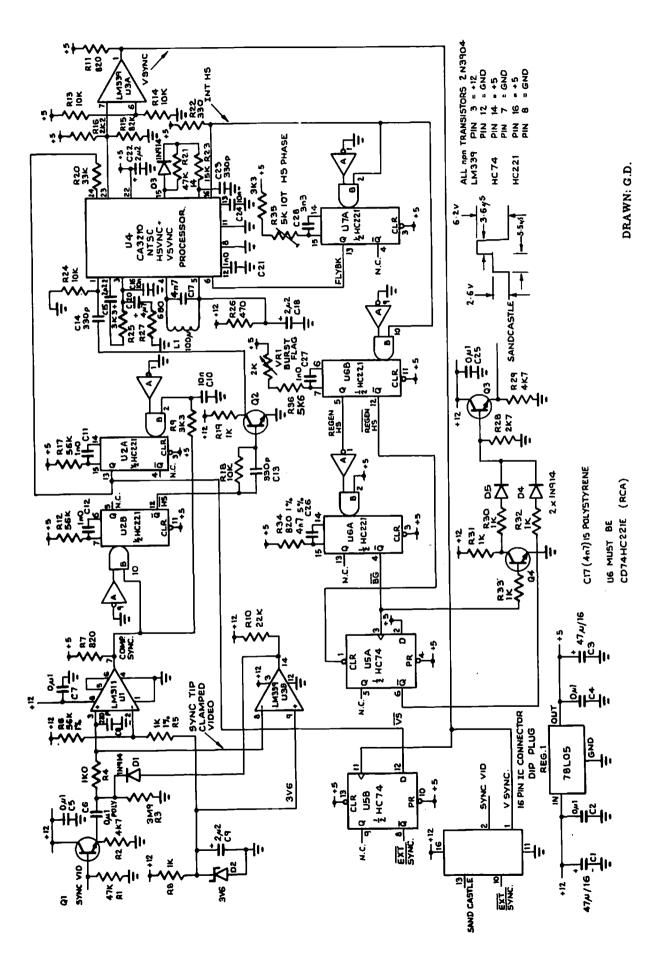

#### Video Board

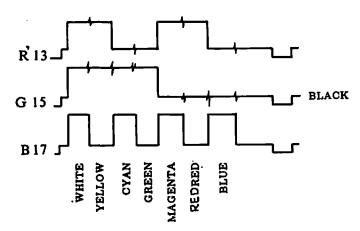

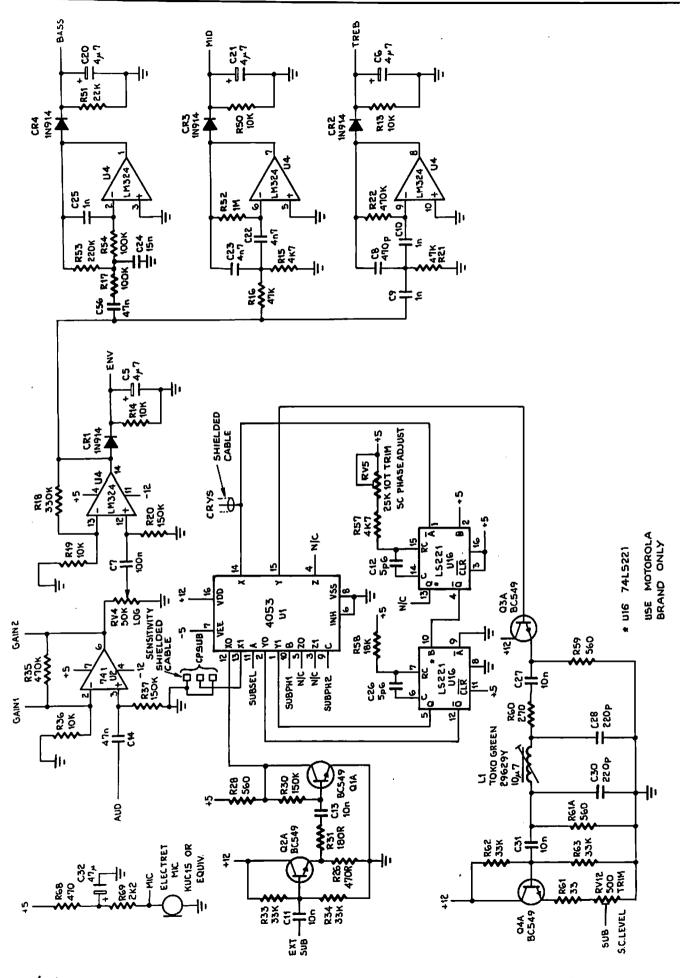

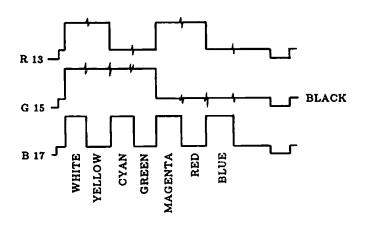

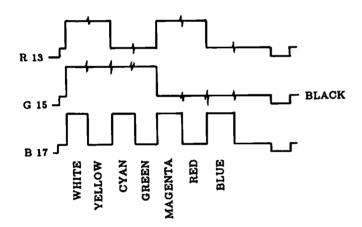

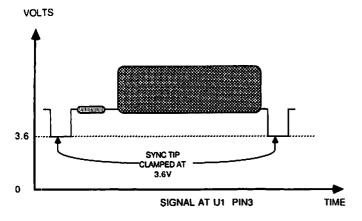

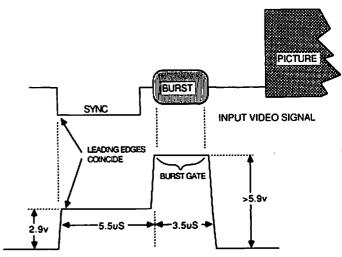

This card contains the composite video decoders, sync separator, colour subcarrier oscillator, encoder, delay lines, buffers, RGB multiplexers and audio filters. It connects to the Main Board via a forty way ribbon cable. The main functions performed on this card

- decoding the input composite video signals to red, green and blue analog signals.

- these signals to the selected - switching analog and digital paths.

- generating the subcarrier signal to be used by the Main Board as a reference frequency.

- generating horizontal and vertical sync signals from the incoming video signals.

- generating the audio control signals from

- the internal microphone or external audio input.

- encoding the final analog RGB signals from the Main Board into a composite video signal.

#### Main Board

This card contains the microcomputer, field store, analog-to-digital and digital-to-analog converters, chroma-key circuitry, control, timing and interface circuitry.

The main functions performed on this card

- conversion of analog RGB signals to digital signals.

- generating the internal and chroma-key stencils.

- generating the timing and control signals for the whole system.

- communicating with external devices via the RS232 port.

- monitoring the status of the control panel.

- displaying and updating the menu displays.

- digitised video -storing a field of information.

- processing the digital signals for such effects as colorisation, freeze, zoom, pan, stretch, mirror, etc.

- generating the final analog RGB signals from the digital and analog RGB signals.

#### Control Panel

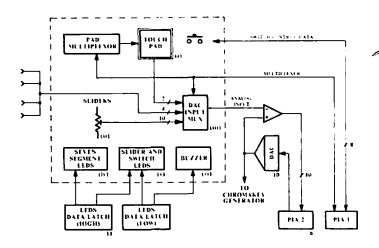

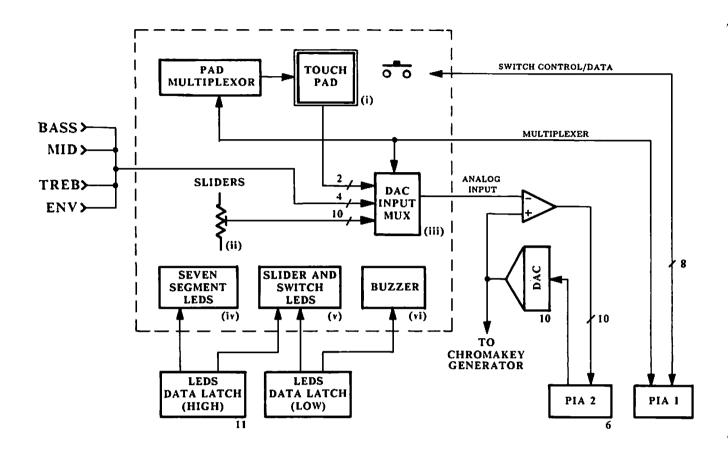

This unit contains the switches, control sliders, graphics pad and preset display. It connects to the Main Board via a forty way ribbon cable upto twenty metres in length.

The main functions performed by the Control Panel are:

- generating the control signals from the switches and sliders.

- deriving position information from graphics pad.

- displaying the preset number.

- indicating the status of various functions on the switch LEDs and buzzer.

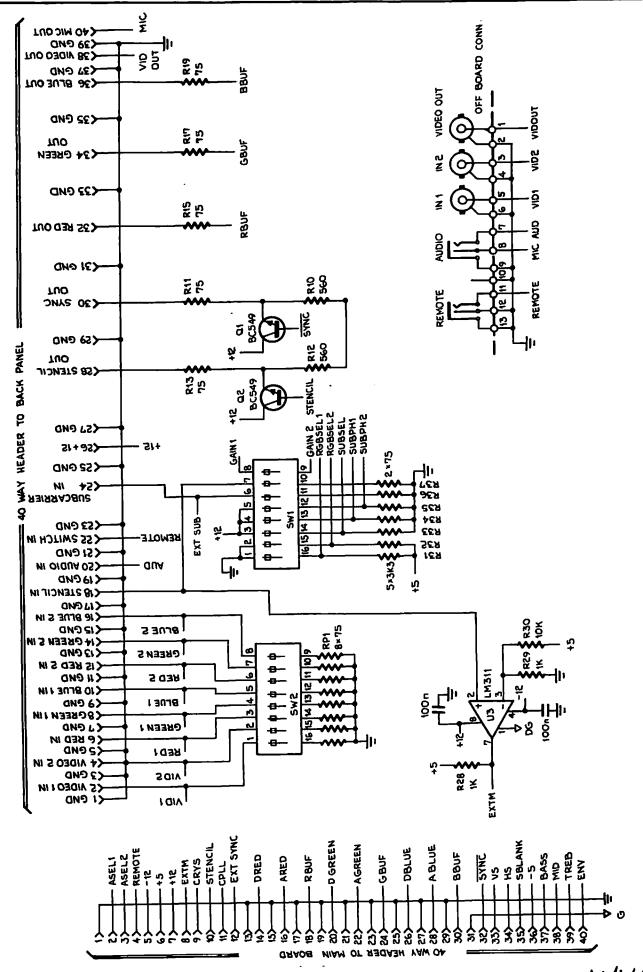

#### BNC Connector Board

This board contains all the input and output connectors. It connects to the Video Board via a forty way ribbon cable.

Power Supply

This unit consists of a switch mode power supply unit, on/off switch and mains socket and filter. It provides the +12v, +5v, -12v and OV supply rails required by the CVI. It connects to the Main Board via a fourteen way ribbon cable.

# Main Board Control Board

2

#### **CONTENTS**

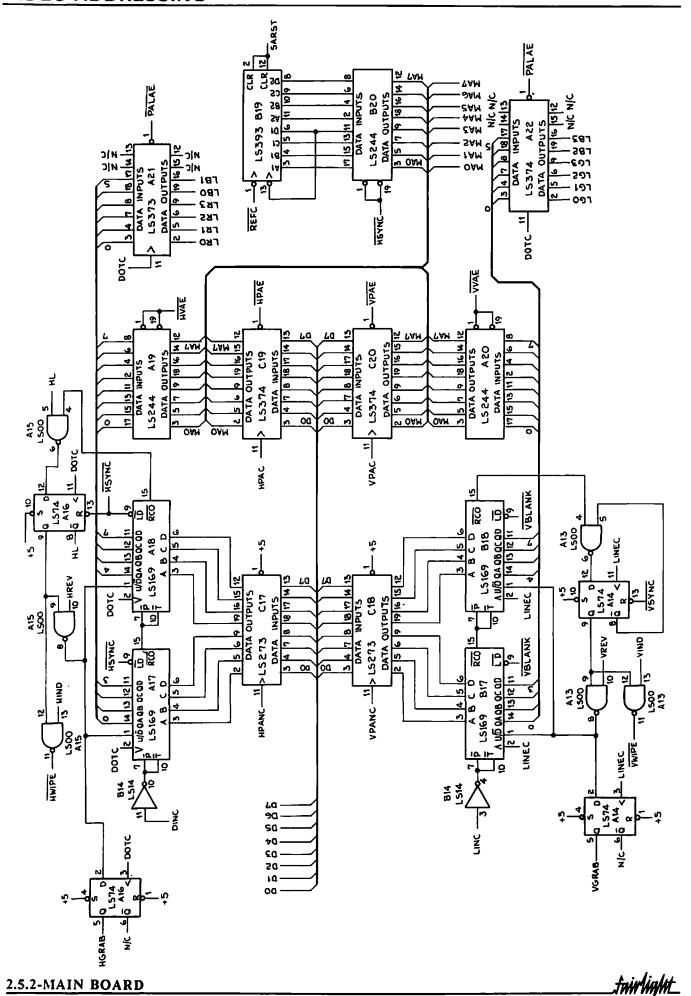

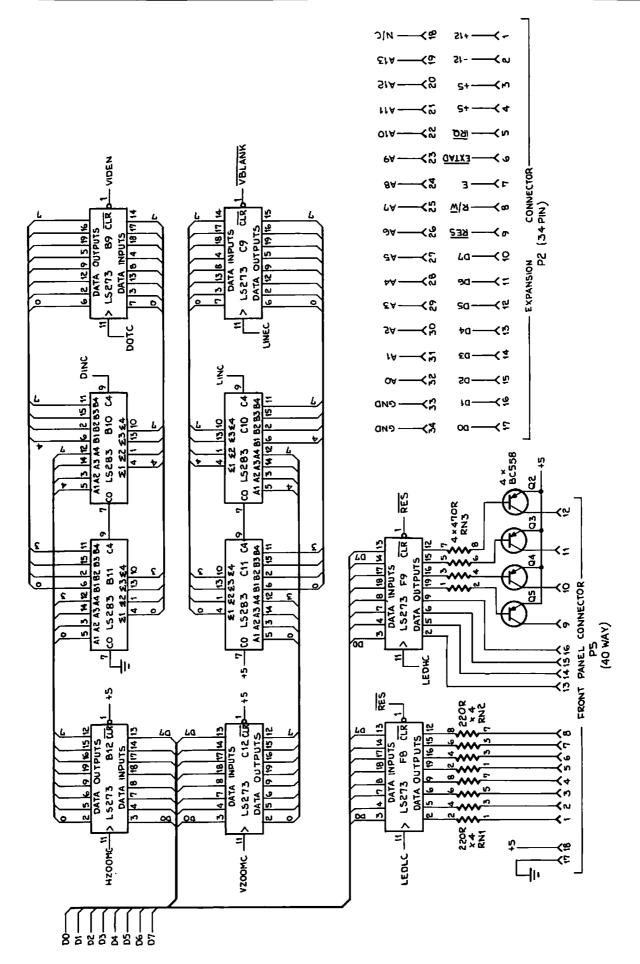

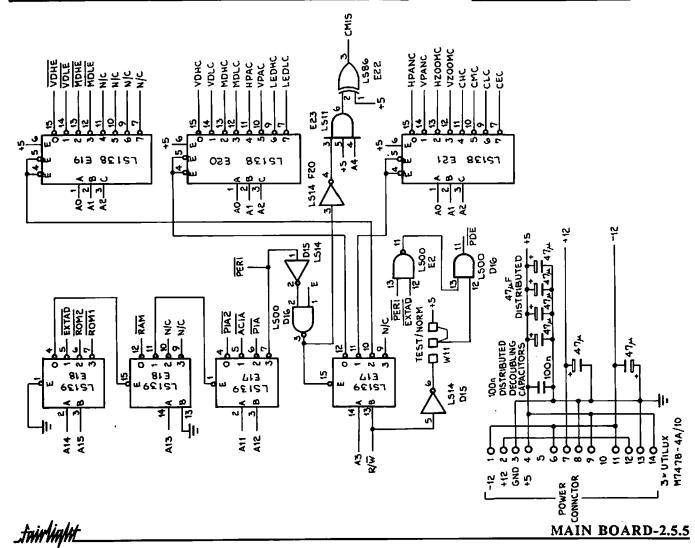

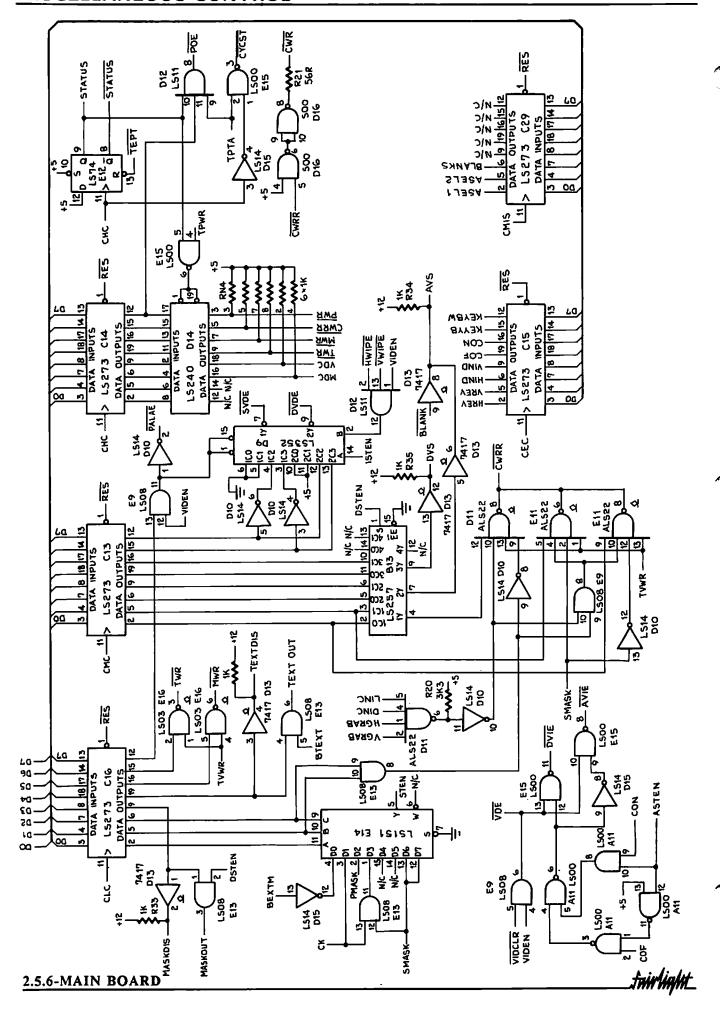

| Block diagram                 | 2.1    |

|-------------------------------|--------|

| Block diagram descriptions    | 2.2    |

| Alignment procedure           | 2.3    |

| Component overlay             | 2.4    |

| Circuit diagrams              | 2.5    |

| Timing diagrams               | 2.6    |

| CONTROL BOARD Block diagram   | 2.7    |

| Block diagram descriptions    | 2.7    |

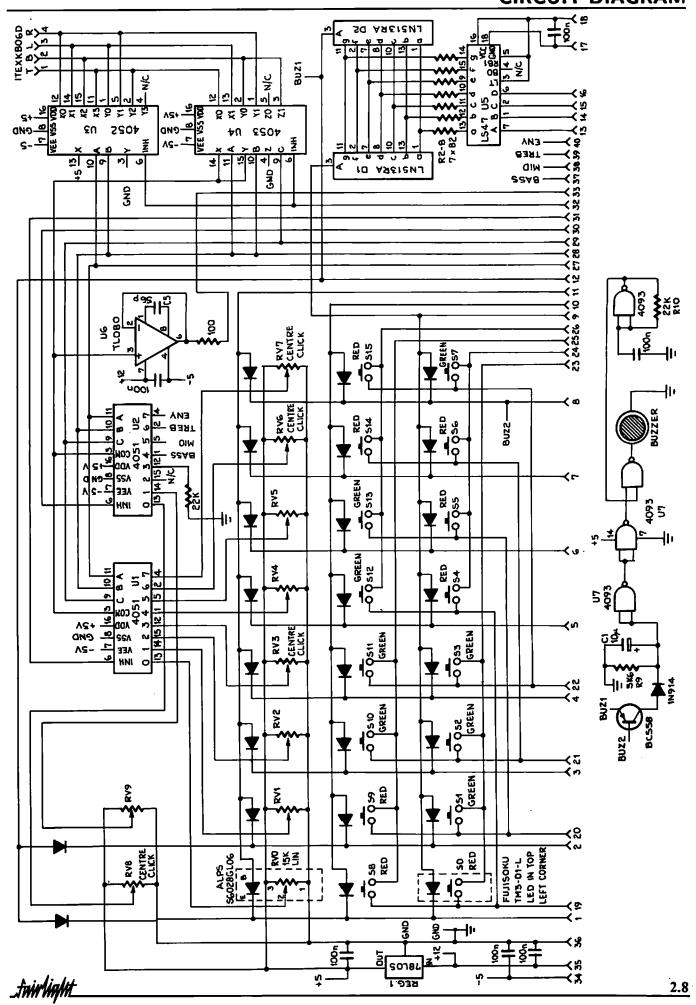

| Circuit diagram               | 2.8    |

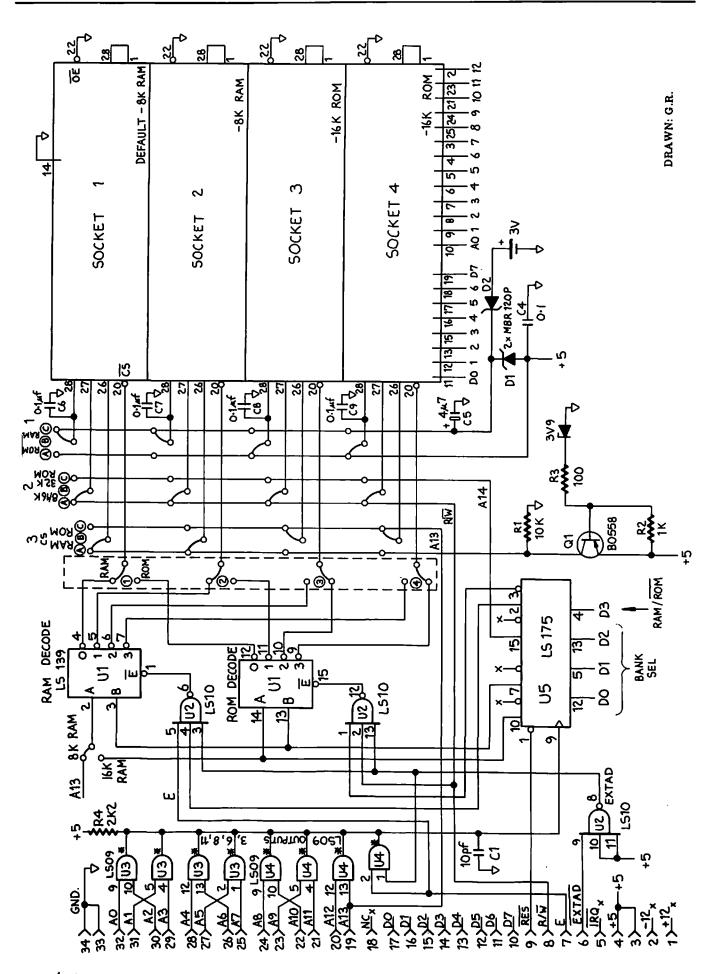

| CVI-07 MEMORY EXPANSION MODUL | Æ      |

| Block diagram                 | 2.10   |

| Functional description        | 2.10   |

| Circuit diagram               | 2.10.2 |

C

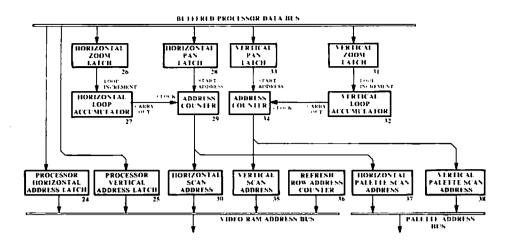

NOTE: For easy reference, the numbers preceeding each paragraph coincide with the block under description on Main Board Block Diagram - Page 2.1.

The numbers in brackets [] refer to the ICs under description. See overlay Page 2.4.

The numbers in parenthesis () refer to Circuit Diagrams No CVI 01, Sheets 1-10, Page 2.5-2.5.9

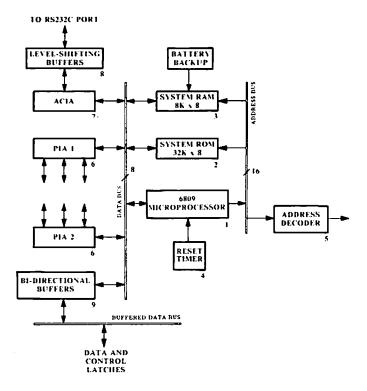

1. 6809 microprocessor runs at 2MHz, asynchronously to the video timing. The processor controls 32K of ROM, 8K of static RAM, two PIA's and one ACIA, as well as four read-only and seventeen write-only latches on a buffered data bus. Processor RAM or ROM may be expanded by up to 16K by using the expansion port.

IRQ interrupts are generated once per frame to initiate hardware configuration activity. All the control latches are set during the IRQ interrupt. FIRQ interrupts are generated four times per frame to update the control-panel LEDs without flicker. NMI interrupts are generated when a character is received or transmitted from the serial port (7). Further synchronisation to the video timing is achieved by polling PIA inputs as required. [A7 (CVI01 Sheet 1)]

- 2. System ROM is 32Kx8. The two 16K chips are removable to accommodate software upgrades. [B7,C7 (CVI01 Sheet 1)]

- 3. System RAM is 8Kx8 of static RAM. Battery backup retains the preset and sequencer data on power-down. [D7 (CVI01 Sheet 1)]

- 4. Reset timer provides the power-up reset pulse to the processor and to much of the digital circuitry. [F19 (CVI01 Sheet 1)]

- 5. Address decoder decodes the address bus into enable signals for each of the processor peripherals, for the expansion bus, and for each of the twentyone processor-accessible 8-bit latches. [E17,E18,E19,E20,E21 (CVI01 Sheet 6)]

- 6. Parallel interfaces control the analog input multiplexer on the control-panel, the chromakey level multiplexer and control-panel switch decoding. The PIA's also provide software access to hardware timing signals and control the IRQ and FIRQ interrupts to the processor. [F12,F16 (CVI01 Sheet 1)]

- 7. Asynchronous communications interface has programmable baud-rate with timing generated from an external crystal. It is programmed for RS232C communications. The ACIA causes NMI interrupts to the processor on data transfer. [A4 (CVI01 Sheet 1)]

- 8. Data buffers convert the TTL ACIA signals to +/-12V line signals and vice versa. [A1,A2 (CVI01 Sheet 1)]

- 9. Bi-directional buffers isolate the processor data bus from the hardware latches, and provide current-drive capability. [A12 (CVI01 Sheet 1)]

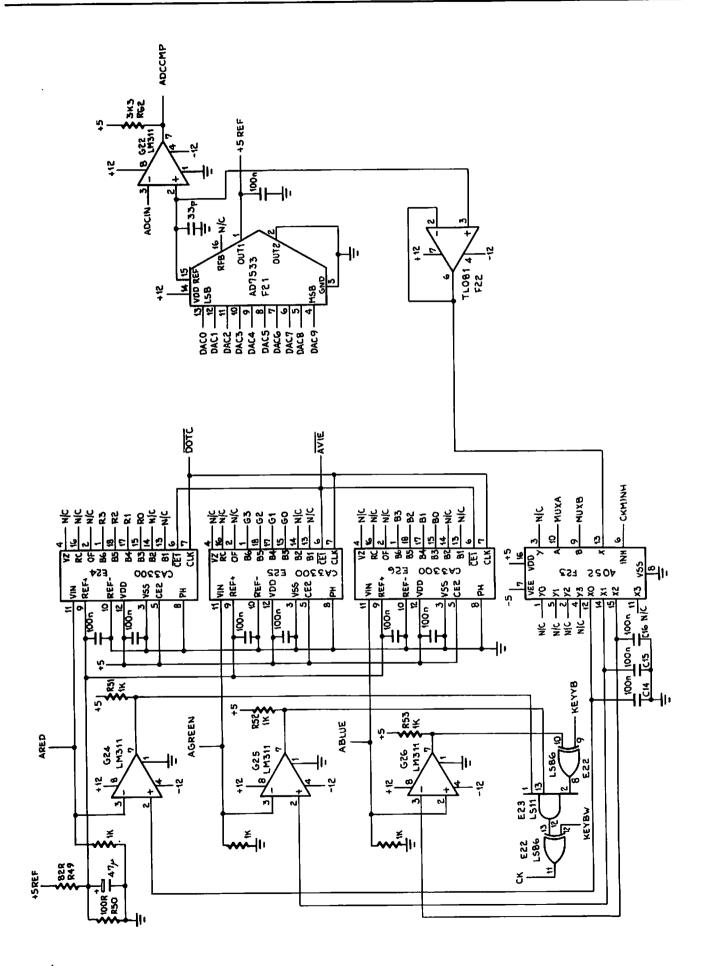

- 10. Analog-to-digital converter is implemented with a 10-bit DAC, a comparator and a successive-approximation algorithm. An analog-to-digital conversion is performed only when an input has changed since the previous reading. The DAC also sets the chromakey levels. [F21,G22 (CVI01 Sheet 9)]

\_twirlight\_

# **BLOCK DIAGRAM DESCRIPTIONS**

- 11. LEDs data latch (16-bit) controls the data and multiplexing sequence for the control-panel LEDs and the buzzer. Four transistor drivers provide current drive. [F8,F9 (CVI01 Sheet 5)

- 12. Miscellaneous control latch (8-bit) controls the multiplexer that selects the video source for each of the analog and digital paths. The multiplexer is located on the video board. The latch also enables extended vertical blanking. [C29 (CVI01 Sheet 7)]

- 13. Effects control latch (8-bit) enables mirror, wipe, chromakey and cascade effects. The bits of the latch each enable or control dedicated hardware logic. [C15 (CVI01 Sheet 7)]

- 14. Effects control is performed by the effects control latch (13).

Horizontal and vertical mirrors are created by enabling counting-direction reversal in the video-address counters (29,34).

Horizontal and vertical wipes are created by enabling carry-out from the video-address counters to swap between the still and live digital image sources.

Cascade of a digital image from another CVI is enabled by selecting data from the cascade input latch (47) instead of from the ADC (46).

Chromakey-type selection (blue or luminance) is made by altering the logical combinations of the chromakey comparator outputs (45). [(CVI01 Sheets 3 & 7)]

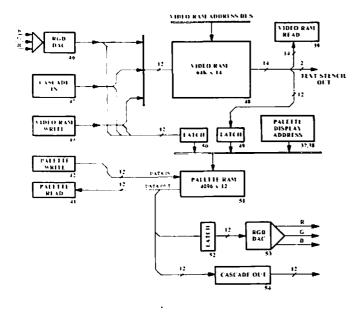

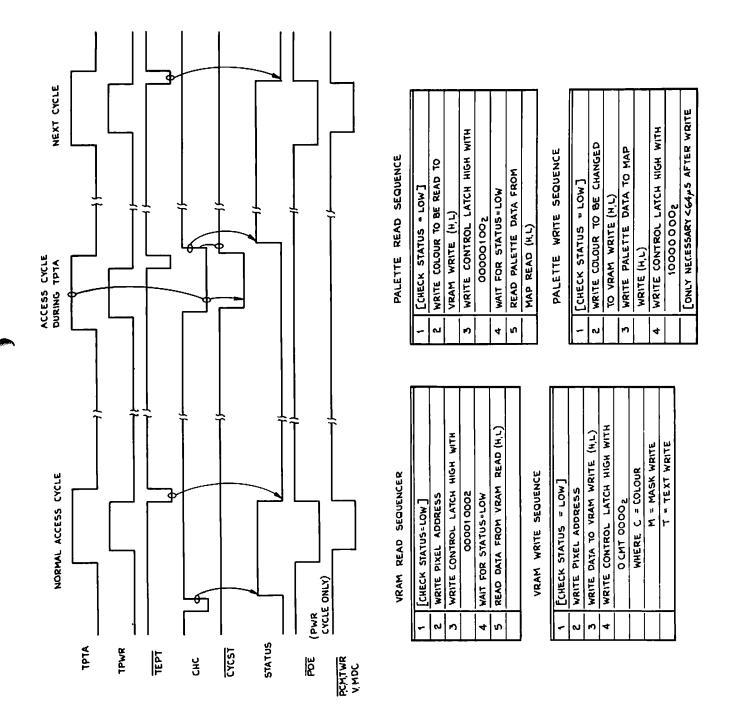

- 15. High control latch (8-bit) stores the processor read/write control signals for the video, stencil, text and palette memories (48,51). [C14 (CVI01 Sheet 7)]

- 16. Processor video access control: Processor access to the video and palette memories is restricted by the horizontal timing generator (62) to once in each video line. A hardware status flag is set when a control word is written to the high control latch (15). The flag is subsequently cleared after the data transfer is completed in the next processor access cycle. The processor reads the flag through PIA1, and hence avoids overwriting unwritten data or reading old data. [E12 (CVI01 Sheet 7)]

- 17. Video and palette RAM read/write control: The latched signals from the high control latch are used during the processor access cycle to enable the processor data latches (39,40,41,42) and to generate read or write pulses to the

appropriate sections of memory. [D14 (CVI01 Sheet 7)]

- 18. Mid control latch (8-bit) stores control signals which operate the output switch (55), determine whether stored or direct image data addresses the palette, and determine whether incoming image data is written to the video RAM. [C13 (CVI01 Sheet 7)]

- 19. Output switch control: Four latched bits from the mid control latch are used to select RGB outputs from either the digital or analog path or both for when the stencil is on and for when it is off. The four bits are combined with the stencil to form two control signals to the output switch (55). [B13 (CVIO1 Sheet 7)]

- 20. Palette address source select hardware determines whether the palette address data (and hence the output of the digital path) is taken from the video RAM (still or freeze) or directly from the digital input (live digital or cascade). [D9 (CVI01 Sheet 7)]

- 21. Low control latch (8-bit) stores data that determines which stencil is to be used and whether the stencil, text page or the palette is displayed. [C16 (CVI01 Sheet 7)]

- 22. Palette display enable logic allows the video address counters (29,34) to address the palette via the palette scan latches (37,38). This causes the output of the digital path to be an ordered display of the palette RAM that can respond to pan and zoom. [(CVI01 Sheet 7)]

- 23. Stencil source select uses three bits from the low control latch to select the active stencil from the internal, external and chromakey stencils. [E14 (CVI01 Sheet 7)]

- 24. Processor horizontal address latch (8-bit) contains the high-order address during a video RAM access by the processor. Data is transferred through the video read or write latches (39 or 40) under the control of the processor video access control logic (16). [C19 (CVI01 Sheet 3)]

- 25. Processor vertical address latch (8-bit) contains the low-order address during a video RAM access by the processor. [C20 (CVI01 Sheet 3)]

- 26. Horizontal zoom latch (8-bit) holds the input data for the loop accumulator (27) that controls horizontal pixel zooming. [B12 (CVI01 Sheet 5)]

- 27. Horizontal loop accumulator (8-bit) increments once each pixel period by the value stored in the horizontal zoom latch. The carry-out from the accumulator enables clocking of the horizontal video address counter. Hence a small value in the zoom latch causes one pixel to be displayed many times, resulting in stretch. [B9,B10,B11 (CVI01 Sheet 5)]

- 28. Horizontal pan latch (8-bit) holds the start address for the horizontal video address counter (29). In slide mode the start address is increased each frame. [C17 (CVI01 Sheet 3)]

- 29. Horizontal address counter increments through horizontal video addresses at a rate determined by the horizontal zoom logic (26,27). Counting begins at the address stored in the horizontal pan latch and continues to the end of the video line. The carry-out is used to determine the position of horizontal mirrors and wipes when they are activated. [A15,A16,A17,A18 (CVI01 Sheet 3)]

- 30. Horizontal scan address latch (8-bit) holds

- the address from the horizontal address counter. [A19 (CVI01 Sheet 3)]

- 31. Vertical zoom latch (8-bit) holds the input data for the loop accumulator (32) that controls vertical pixel zooming. [C12 (CVI01 Sheet 5)]

- 32. Vertical loop accumulator (8-bit) increments once each line period by the value stored in the vertical zoom latch. The carry-out from the accumulator enables clocking of the vertical video address counter. [C9,C10,C11 (CVI01 Sheet 5)]

- 33. Vertical pan latch (8-bit) holds the start address for the vertical video address counter (34). In slide mode the start address is increased each frame. [C18 (CVI01 Sheet 3)]

- Vertical address counter increments through vertical video addresses at a rate determined by the vertical zoom logic (31,32). Counting begins at the address stored in the vertical pan latch and continues to the end of the video field. The carry-out is used to determine the position of vertical mirrors and when wipes they activated. are [A13,A14,B17,B18 (CVI01 Sheet 3)]

- 35. Vertical scan address latch (8-bit) holds the address from the vertical address counter. [A20 (CVI01 Sheet 3)]

- 36. Refresh counter continually refreshes the dynamic video RAM during the horizontal blanking periods by cycling through the row addresses. [B19,B20 (CVI01 Sheet 3)]

- 37. Palette horizontal scan latch (6-bit) takes addresses from the horizontal pan/zoom counter (29). If the palette display logic (22) enables the latch then the addresses are applied to the palette RAM to give an ordered palette display. [A21 (CVI01 Sheet 3)]

38. Palette vertical scan latch (6-bit) takes addresses from the vertical pan/zoom counter (34). If the palette display logic (22) enables the latch then the addresses are applied to the palette RAM. [A22 (CVI01 Sheet 3)]

- 39. Video read latch (16-bit) contains the 14 bits of data after a processor read from the video RAM. [C21,C22 (CVI01 Sheet 2)]

- 40. Video write latch (16-bit) is the write-data latch for the video RAM and the address latch for the palette RAM. The control word written to the high control latch determines which function is required. [C23,C24 (CVI01 Sheet 2)]

- 41. Palette read latch (16-bit) contains the 12 bits of data after a processor read from the palette RAM. [C27,C28 (CVI01 Sheet 4)]

- 42. Palette write latch (16-bit) contains the 12-bits of data for a processor write to the palette RAM. [C25,C26 (CVI01 Sheet 4)]

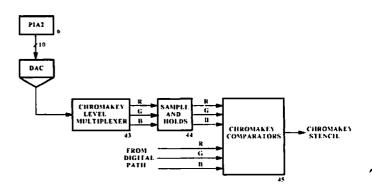

- 43. Chromakey level multiplexer updates the red, green and blue analog chromakey levels to the three sample-and-hold circuits every field under processor control. The analog levels are supplied from the DAC (10) and the multiplexer is controlled from PIA1. [F23 (CVI01 Sheet 9)]

- 44. Sample and holds hold the chromakey reference levels set by the processor. [(CVI01 Sheet 9)]

- 45. Chromakey comparator compares the incoming red, green and blue levels with the chromakey references. The comparator outputs are combined logically with the chromakey-type controls from the effects latch (13) to generate the chromakey stencil. [G24,G25,G26 (CVI01 Sheet 9)]

- 46. RGB digital-to-analog flash converter digitises each of the red, green and blue signals to four bits. The 12-bit output may be stored in the video RAM (still/freeze) or used to address the palette (live digital). [E24,E25,E26 (CVI01 Sheet 9)]

- 47. Cascade input latch (16-bit) enables image data to be cascaded from another CVI. The latch is enabled via the effects control latch (13). [A23,A24 (CVI01 Sheet 4)]

- 48. Video RAM is 64Kx14 bits of dynamic RAM. The 64K locations correspond to the 2,56x256 pixel locations. Each pixel location has 12 bits of colour information, one bit for the stencil information and one bit for the menu page. [D17,D18 ... D29,D30 (CVI01 Sheet 2)]

- 49. Palette address latch (12-bit) allows direct digital image data or processor data to address the palette RAM. This latch is enabled from the palette-address selection logic (20). [B23,B24 (CVI01 Sheet 4)]

- 50. Palette address latch (12-bit) allows stored image data from the video RAM (48) to address the palette RAM. This latch is enabled from the palette-address selection logic (20). [B21,B22 (CVI01 Sheet 2)]

- 51. Palette RAM is 4Kx16 bits of static RAM of which 4Kx12 bits are used. It performs a colour transformation, allowing each colour to be mapped to any other colour. The 12-bit address is pixel colour data from the video RAM or from the direct video inputs. The 12-bit data output is the transformed or colourised value of the addressing colour. Data is written to the palette RAM only by the processor, through the video and palette write latches (40,42). [A25,A27,B25,B27 (CVI01 Sheet 4)]

- 52. Palette output latch (16-bit) clocks the transformed colour data from the palette RAM to the RGB digital-to-analog converter and to the cascade output. [A28,B28 (CVI01 Sheet 4)]

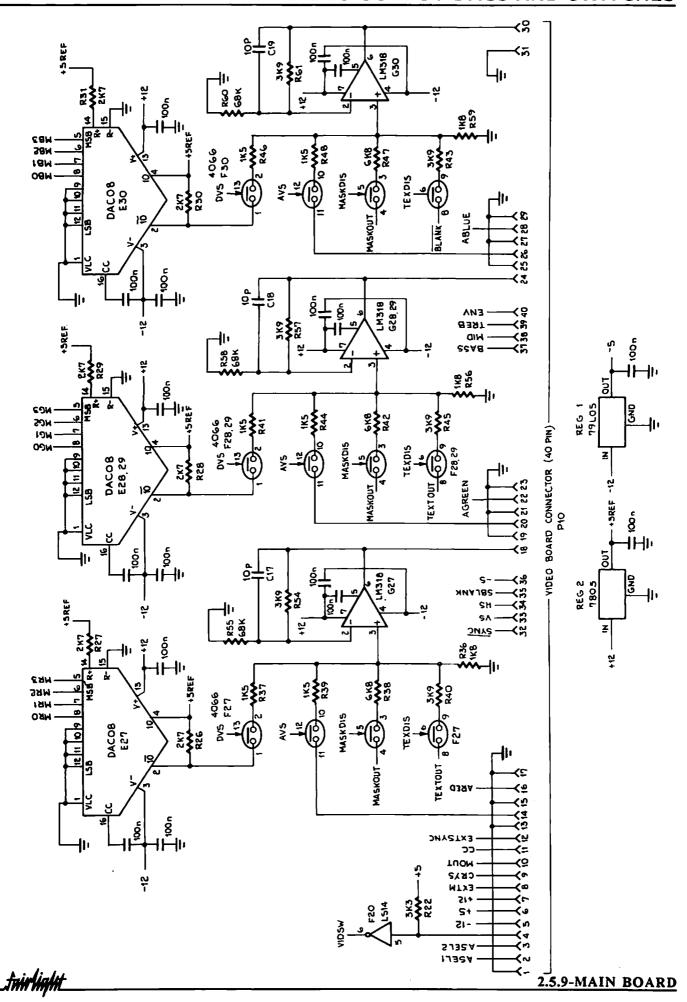

- 53. RGB digital-to-analog converter converts the twelve bits of colour information from the digital path back into three analog signals (red, green and blue). [E27,E28,E30 (CVI01 Sheet 10)]

- 54. Cascade output buffer (16 bit) buffers the digital video outputs to a second CVI. [A29,B29 (CVI01 Sheet 4)]

- 55. Video output switch combines the digital and analog paths, the stencil and the menu page into the final image format. Each of the red, green and blue outputs is formed by the selective analog addition of the digital path, analog path, stencil and text signals. This enables such functions as menus, show-stencil, video-mix, live digital, still, video, etc. The adder is controlled by the output-switch control logic (19) and by the low control latch (21). [E27,E28,E30 (CVI01 Sheet 10)]

- 56. Output buffers buffer the output of the video switches. [G27,G28,G30 (CVI01 Sheet 10)]

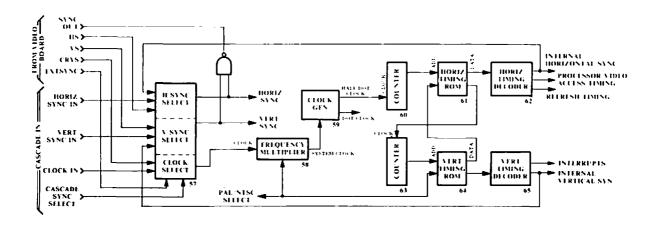

- 57. Sync source select circuit selects the source of the system sync signals according to the status of EXTERNAL SYNC and CASCADE SYNC lines. EXTERNAL SYNC is enabled if an input is connected to the CVI Video 1 input. CASCADE SYNC is enabled if an input is connected to the Cascade In port. System sync signals are selected, as appropriate, from the internal syncs (62,65), from the sync derived from the external video signal, or from the cascade syncs. The twice-subcarrier signal is selected either from the clock on the video board or from the cascade input clock. [B3,B4,B5 (CVI01 Sheet 8)]

- 58. Frequency multiplier uses a phase-locked loop to multiply the twice-subcarrier clock by four for PAL or five for NTSC to give the 35MHz system clock. [F1,F4 (CVI01 Sheet 8)]

twirlight

# **BLOCK DIAGRAM DESCRIPTIONS**

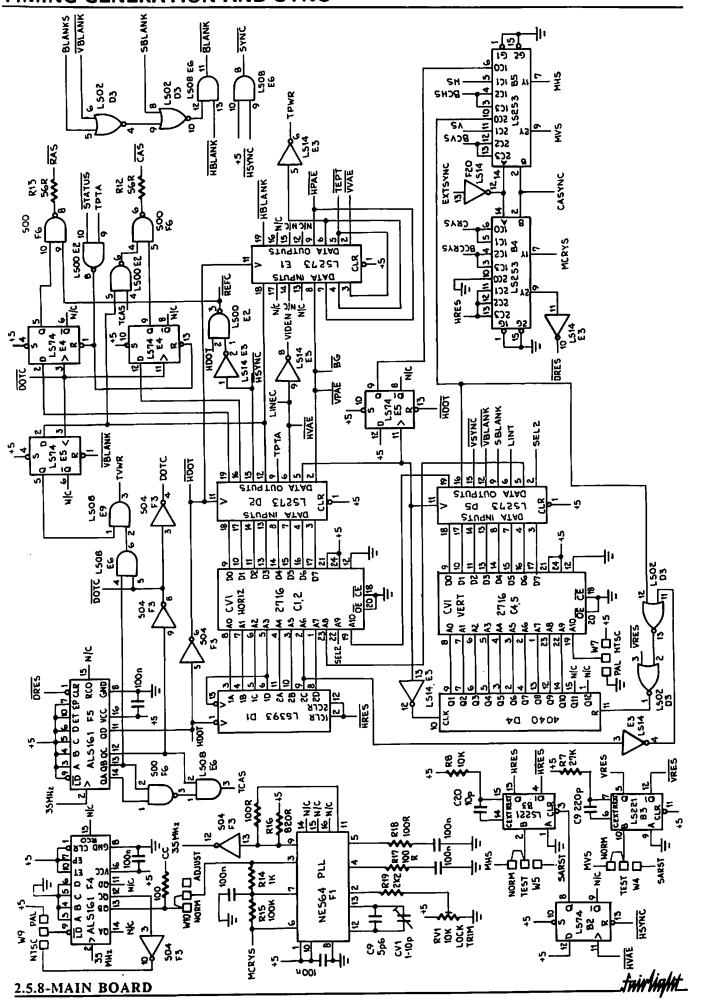

- 59. Clock generator uses the 35MHz system clock from the frequency multiplier to generate a number of hardware clocks. The pixel (dot) clock is the system clock divided by 8. [F5 (CVI01 Sheet 8)]

- 60. Horizontal timing counter addresses the horizontal timing ROM sequentially. It is clocked at twice the pixel rate, and is cleared by the system horizontal sync pulse from the sync selector (57). [D1 (CVI01 Sheet 8)]

- 61. Horizontal timing ROM is 2Kx8 bits. It contains the data to generate eight horizontal control signals for one video line in both PAL and NTSC formats. The highest address bit of the ROM, which selects between PAL and NTSC timing data, is controlled by the vertical timing ROM. [C1 (CVI01 Sheet 8)]

- 62. Horizontal timing decoder combines the eight timing signals from the horizontal timing ROM to generate all the horizontal video and digital timing signals for the system, including the refresh timing and processor video access timing. [D2,E1,E4,E5 (CVI01 Sheet 8)]

- 63. Vertical timing counter addresses the vertical timing ROM sequentially. It is clocked by the line pulse from the horizontal timing ROM, and is cleared by the system vertical sync pulse from the sync selector (57). [D4 (CVI01 Sheet 8)]

- 64. Vertical timing ROM is 2Kx8 bits. It contains the data to generate eight vertical control signals for one video field in both PAL and NTSC formats. The highest address bit of the ROM selects between PAL and NTSC timing data. [C4 (CVI01 Sheet 8)

- 65. Vertical timing decoder combines the eight timing signals from the vertical timing ROM to generate all the vertical video and digital timing signals for the system, including processor interrupts. [D5 (CVI01 Sheet 8)]

\_twirlight\_

()

#### PAL

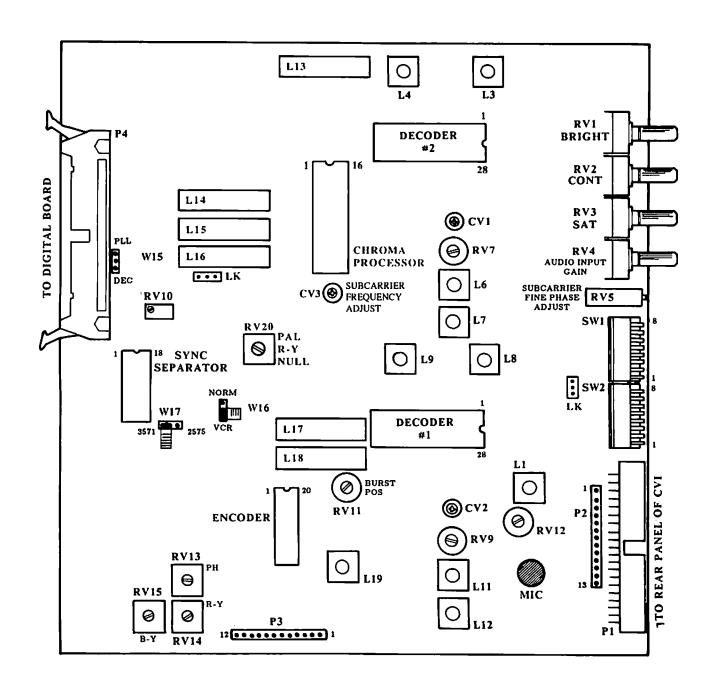

#### **Equipment Required**

- Frequency meter, 100 MHz

- CVI-03 PAL aligned video board.

- Component overlay page 2.4.

#### Setup

- Remove the video board connector from P10.

- Set link W10 to ADJUST.

- Set link W7 to the position closest to link W8.

- Set link W9 to the position farthest from link W10.

- Set the link at board matrix F11 to the position closest to E10.

- Set RV1 to mid-range.

- Set RV2 fully clockwise.

#### Procedure

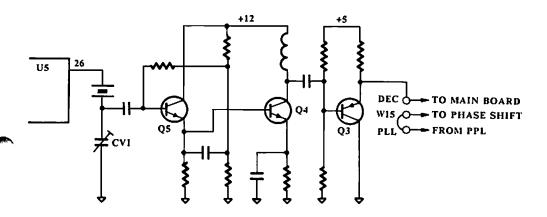

- Measure the frequency at the NORM pin of W10.

- Adjust CV1 so that the frequency is 8.867MHz.

- Set link W10 to NORM.

- Reconnect the video board connector to P10.

- Measure the frequency at the NORM pin of W10. It should be 8.86723 MHz (+/- 10 Hz).

#### NTSC

#### Equipment required

- Frequency meter, 100MHz.

- CVI-03 NTSC aligned video board.

- Component overlay page 2.4.

#### Setup

- Remove the video board connector from P10.

- Set link W10 to ADJUST.

- Set link W7 to the position farthest from link W8.

- Set link W9 to the position closest to link W10.

- Set the link at board matrix F11 to the position closest to E12.

- Set RVI to mid-range.

- Set RV2 fully clockwise.

#### Procedure

- Measure the frequency at the NORM pin of W10.

- Adjust CV1 so that the frequency is 7.159MHz.

- Set link W10 to NORM.

- Reconnect the video board connector to P10.

- Measure the frequency at the NORM pin of W10. It should be 7.15909 MHz (+/- 10 Hz).

tairlight

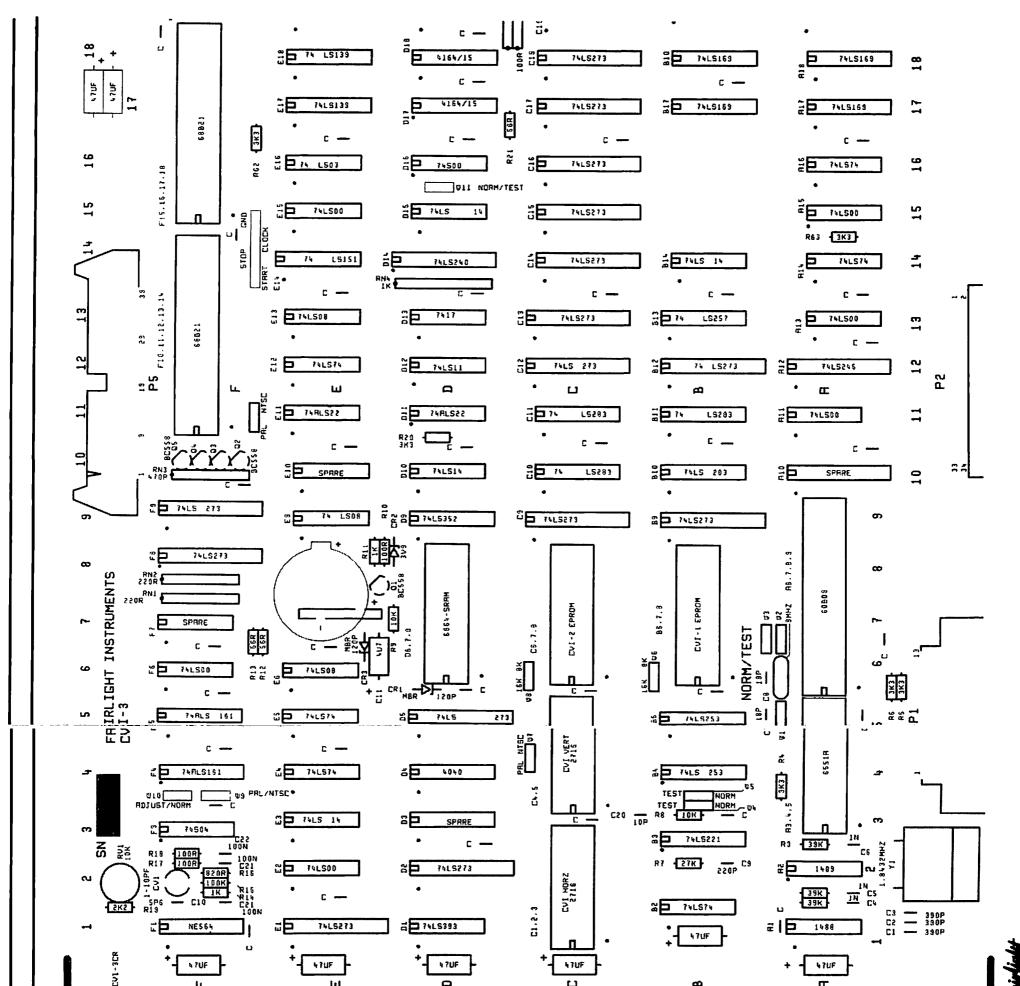

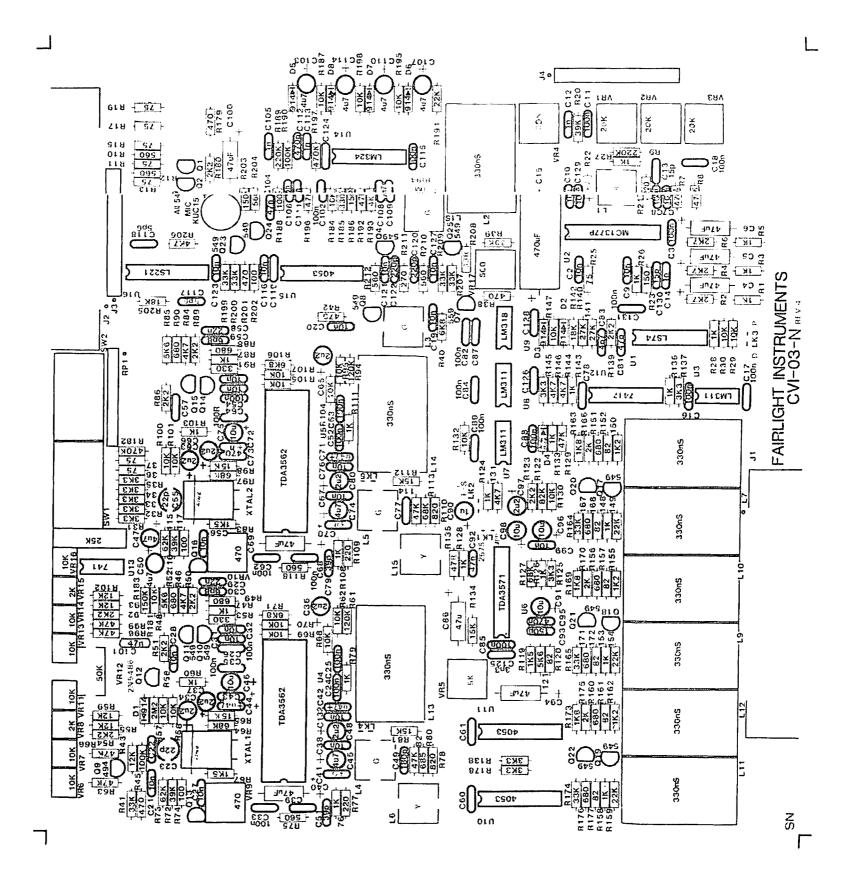

## **COMPONENT OVERLAY**

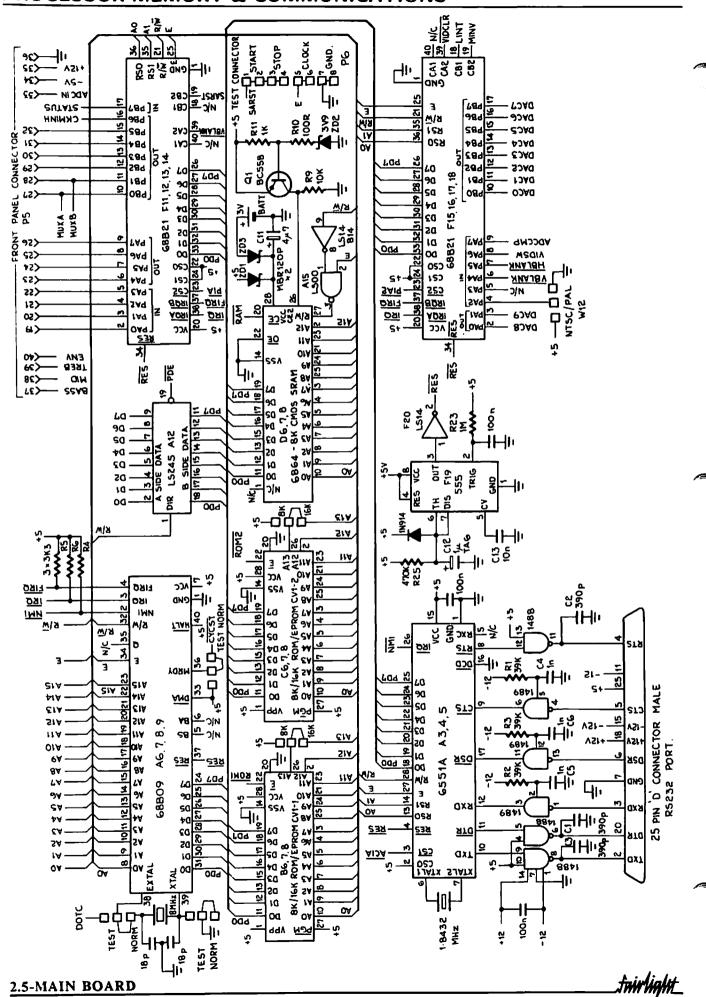

# PROCESSOR MEMORY & COMMUNICATIONS

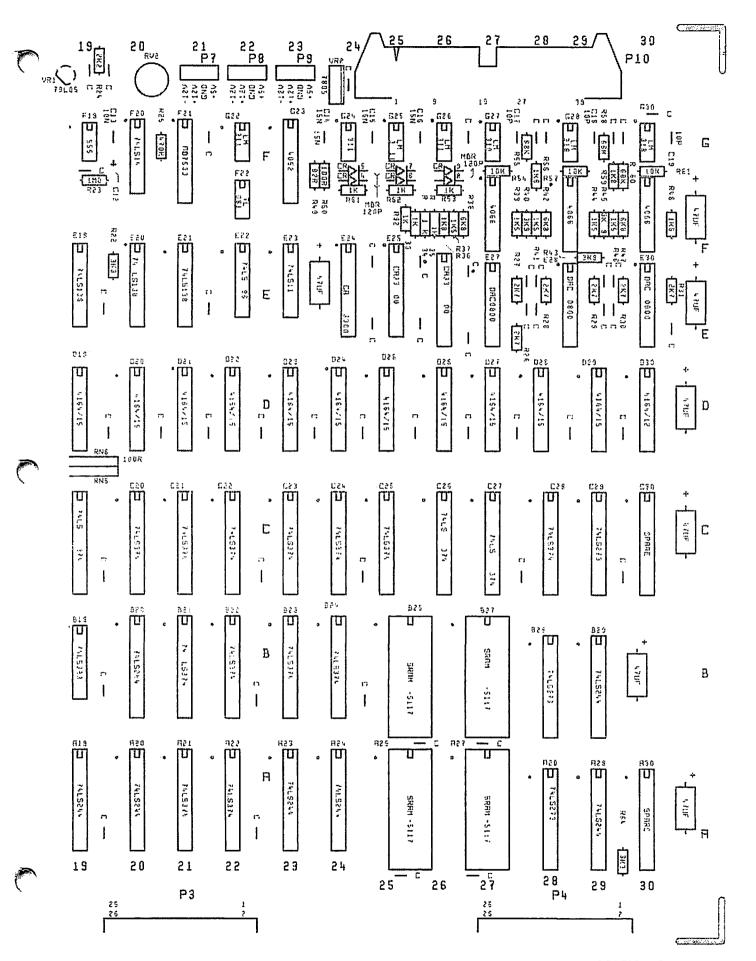

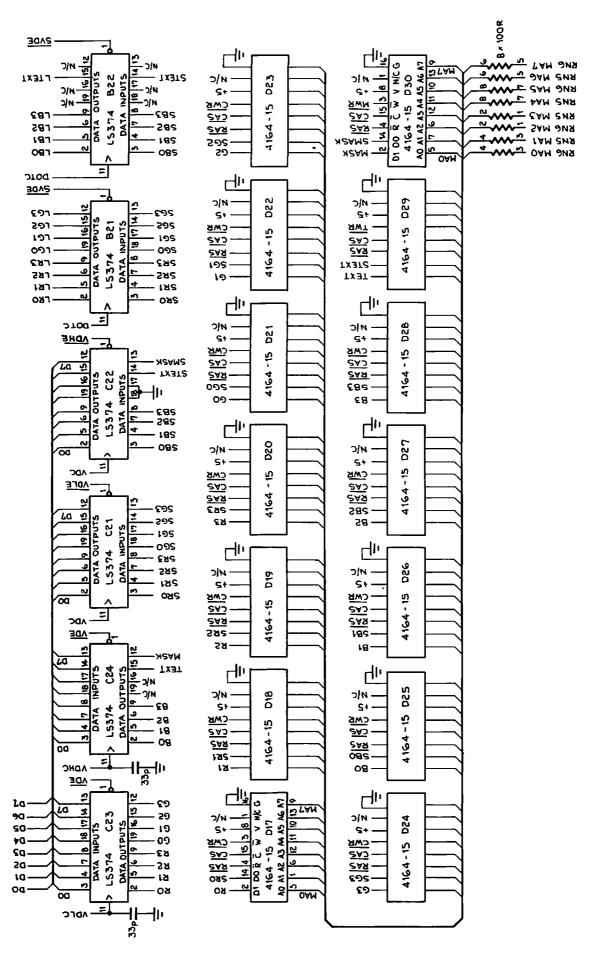

# **MEMORY ARRAY**

\_tairlight

#### VIDEO I/O AND PALETTE 13 STENCIL OUT VIDEO OUTPUTS DIGITAL T HORIZONTAL A SELECT OUT S SYNC OUT 3 CLOCK OUT CASCADE OUTPUT P4 (26 PIN) GREEN BLUE 6 23 89 12 26 83 13 26 83 15 80.07 15 80.07 16 80.07 У'n **B** \$ STURINO ATAC 12544 A29 **44581** 658 MOUT-BVS BHS STUGNI STUGNI ATAO CC 17 চাত Ū = @ 0 4 MOHE -EOM MB3 MR3 30 SBM IBM PMASK <u>₹</u> MB3 BTEXT ISTEN E S 5 15 6 9 19 16 15 DATA OUTPUTS NBO 18 L5374 C28 99 69 41 Nez 5 2010 89 SOM 리 정치 히 ō 악 ው NGI ETUGTUO ATAG **STUGTUO** ATAG NCO 828. £7521 24251 **8**SA МКЗ STURNI ATAD STURNI ATAO <u>00</u> MES ISTEN 13 ASTEN 400 MKI NBO YOW. - (20 POE ) ð, Ø PKR PWR MOLE 2 2 4 5 50 40 8 2 85 삥 t\$ OUTPUTS MIN 2K\*8 SRAM LS374 C27 2K ×8 SRAM A27 16 5117 827 \$ 85 814 LS14 ল 52 3 MDC 한 뚫 읾 <u>8M4</u> 5 ঞ ε **{}**} 4 5 Ō 02 02 02 03 02 8 2 2 2 3 OATA WPUTS LS374 C26 DATA OUTPUTS <u>\*</u> SRAM 94 825 5117 SRAM 5117 **A25** 9 €8 ķ Ş Ą 8 4 8 3 2 \$ *B*S 98 18 38 200 ٤Đ erugruo 8 9 LB3 СS жом-597 19 F.3 9 STUATUO ATAG **BMB** 법 762S7 458 **7**6297 28 CASYNC ATAO STUGNI **ATAG** 18 DOTC TTT 물물물물 200 0 00 5 4 18 17 17 ₽ DATA OUTPUTS KO. L5374 C25 ઉ 3 8 , 45년 미국 등 등 B14 LS14 إو 2 BYS 2 BYS 3 BYS 3 BYS 3 BYS 3 BYS 8 別 DATA EXTM σ S RG3 **© ETUGTUO** STURTUO ATAG £SA 4S4 77257 18. 18. = STUQNI ATAQ MOLC CCRYS MVS 6 10 CVS CVS CHS 6 14 CHS P3 (26 PIN) SHJ. Ş 불 25 E 25 E 83 /26 R3 / 18 ۳ ં જે Ţº La INPUT 90 72 T STENCIL IN TO CLOCK IN 3 CASCADE SYNC SELECT 大QNS HORIZONTAL SYNC IN **5**0 CONNECTOR 92 ۲q 8 સુ CASCADE VERTICAL SYNC IN £a

RED

20 19

trirlight.

**GKEEN**

NIDEO

STUQNI

BLUE

MAIN BOARD-2.5.3

DIGITAL

.twirlight\_

# ADDRESS DECODING

| ADDRESS         WRITE FUNCTION           3800         VRAM DATA HIGH           3802         PALETTE DATA HIGH           3803         PALETTE DATA HIGH           3804         HORIZONTAL ADDRESS           3805         VERTICAL ADDRESS           3806         LEDS HIGH           3807         LEDS HIGH           3808         VERTICAL ADDRESS           3809         VERTICAL PAN           3809         VERTICAL PAN           3809         VERTICAL PAN           3806         CONTROL HIGH           3807         CONTROL HIGH           3808         CONTROL LOW           3809         CONTROL LOW           3806         CONTROL LOW | VIDEO 1/O ADDRESS MAP                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | NCTION READ FUNCTION                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | HIGH VRAM DATA HIGH                   |

| W   W   W   W   W   W   W   W   W   W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LOW VRAM DATA LOW                     |

| [X]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | HGH PALETTE DATA HIGH                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LOW PALETTE DATA LOW                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ADDRESS                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ODRESS                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | - L                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | — — — — — — — — — — — — — — — — — — — |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | М00                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | O)                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Mo                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | FECTS                                 |

| 3810 CONTROL MISC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | MISC.                                 |

| ADDRESS MAP | ٥        | 1/0 ADDRESS MAP | SS MAP    |

|-------------|----------|-----------------|-----------|

| 0000 - 1FFF | RAM      | 2000 - 27FF     | PIA2      |

| 357 - 0005  | ofı      | 2800 - 2FFF     | ACIA      |

| 4000 ~ 7FFF | EXTERNAL | 3000 - 37FF     | PIA1      |

| 8000 - BFFF | ROM 2    | 3800 - 3FFF     | VIDEO 1/O |

| C000 - FFFF | ROM 1    |                 |           |

|             |          |                 |           |

\_tairlight\_

# **VIDEO OUTPUT DACS AND SWITCHES**

• •

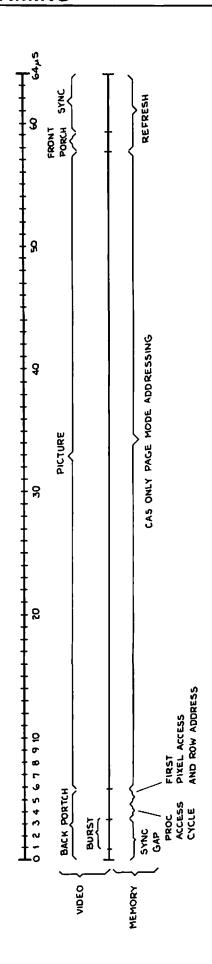

| No OF CC CYCLES / LINE   283-7516   227-301                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PARAMETER              | PAL      | NTSC      | UNITS      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------|-----------|------------|

| ENCY ES 30  ICY 15625 15750  G4 63-492  AE 625 525  IR 4-7  IR 05  IR 05 | No OF CC CYCLES / LINE | 283-7516 | 227 - 301 |            |

| CY (\$625 (\$750)  64 65-492  AF 625 525  RON (\$05 1:55  1:50 5:6  5:0 5:0  CE 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | FRAME FREQUENCY        | 22       | 30        | H2         |

| 4.7 625 525 18 625 525 18 625 525 19 625 625 625 625 625 625 625 625 625 625                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | LINE FREQUENCY         | 15625    | 15150     | Hz         |

| 1.8 625 525 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 625 18 6 | LINE PERIOD            | 64       | 63.492    | ST         |

| 18.05<br>1.55<br>1.55<br>10N<br>5.6<br>5.6<br>51.95<br>10D<br>56.95<br>100<br>6E 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | No LINES/FRAME         | 625      | 525       | MHz        |

| 15.5<br>1.55<br>10N 5.25<br>10N 5.25<br>10N 5.49<br>10DE 300<br>6E 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | COLOUR CARRIER         | 4.7      |           | St         |

| 1.55<br>10N 5.25<br>10N 5.25<br>10E 5.6<br>5.6<br>5.6<br>5.6<br>5.6<br>5.6<br>5.6<br>5.6<br>5.6<br>5.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | BLANKING               | 12.05    |           | ST         |

| 10N 5.25<br>10N 5.25<br>5.6<br>5.6<br>51.95<br>100<br>6E 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | FRONT PORCH            | 1.55     |           | ST         |

| 10N 5.25<br>5.6<br>5.6<br>51.95<br>UDE 300<br>GE 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | BACK PORCH             | 5.8      |           | ST         |

| 5.6<br>51.95<br>UDE 300<br>GE 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | BURST DURATION         | 5.25     |           | F.S        |

| S1.95 UDE 300 GE 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | BURST START            | 5.6      |           | ×5         |

| GE 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ACTIVE VIDEO           | 51.95    |           | ST         |

| GE 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | BURST AMPLITUDE        | 300      |           | ٦ <u>٠</u> |

| 300                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SIGNAL VOLTAGE         | 100      |           | 7 &        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SYNC VOLTAGE           | 300      |           | Λth        |

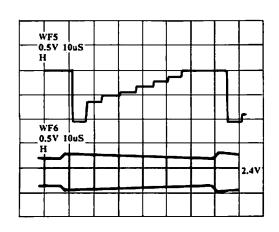

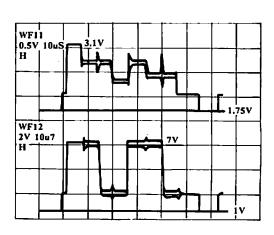

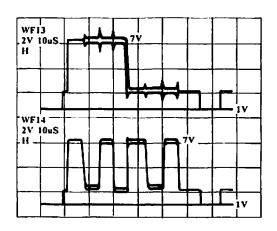

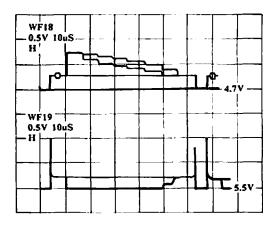

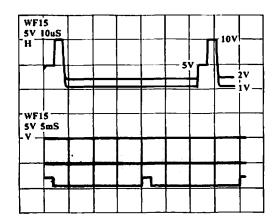

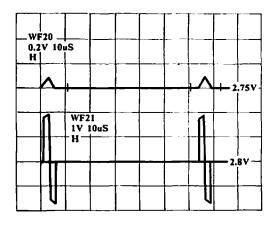

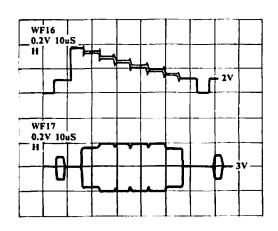

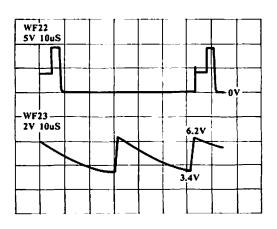

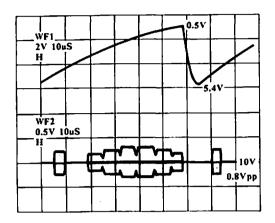

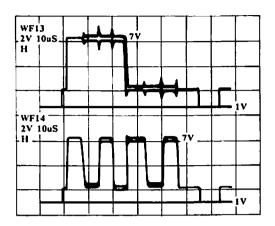

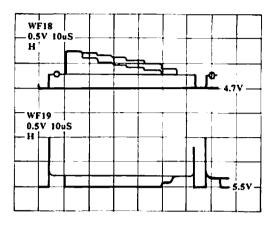

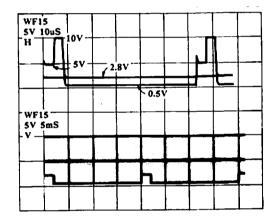

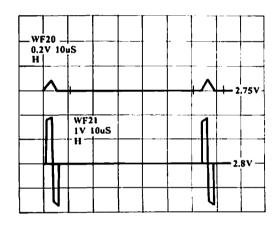

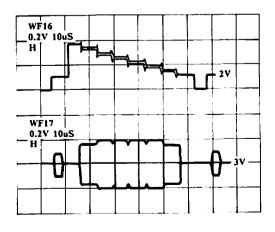

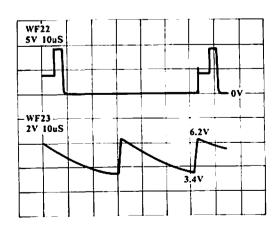

## PROCESSOR TRANSFER CYCLE

strivlight.

- 1. Touch-sensitive pad, under the control of two multiplexers, produces four voltages which are decoded to determine the pad touch position. The multiplexers are controlled from PIA1. [U3,U4]

- 2. Front panel pots each generate a voltage according to the slider position, which may be digitised by the ADC under software control.

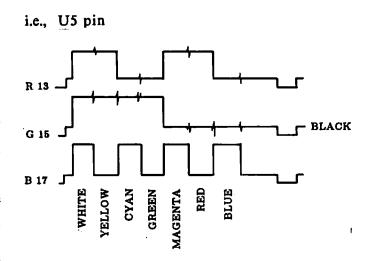

- 3. Seven-segment leds are controlled by a seven-segment decoder/driver using four bits from the LEDs control latch. [U5,D1,D2]

- 4. Front-panel leds on the pots and switches are arranged in a 4x8 multiplexing matrix controlled by 12 bits from the LEDs control latch. Each LED is updated 50-60 times per second.

- 5. Buzzer oscillator is enabled using a position in the front-panel multiplexing matrix (4). [U7]

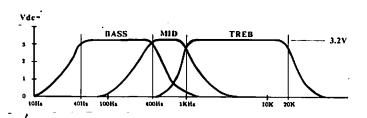

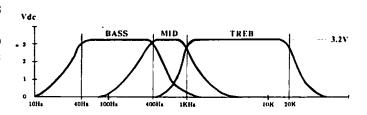

- 6. Analog-input multiplexer selects the input to the analog-to-digital converter from the front-panel slider voltages, the touch-pad voltages and the audio-analyser levels (bass, mid-range, treble and envelope). The multiplexer is controlled from PIA1. [U1,U2,U6]

### **CIRCUIT DIAGRAM**

. **!** . • . •

### BLOCK DIAGRAM D0-7 D0-3 CONTROL ADDR DECODE U3,U4 \$ 7FFF CONTROL SOCKET SOCKET SOCKET LATCH US Expansion Socket Bank, ROM/RAM Select To Pins - 28,27,26,20 RAM RAM Chip Selects DECODE EXTAD (Module Select) ROM DECODE ROM Chip Selects R/W JUMPER LINKS POWER DOWN RAM BACKUP BATTERY

General

The memory expansion module plugs into the "expansion bus" socket on the back of the CVI. It allows up to 128K bytes of EPROM or 64K bytes of static battery RAM (or various mixes of EPROM and RAM) to be added to the CVI system memory. The memory on the module exists as a number of 16K byte banks which are selected under software control to appear in the 16K expansion bus address space, at 4000 to 7FFF.

### Functional description

- 1) Control address decode. The 16 input AND gate formed of U3 and U4 decodes the top address within the 16K byte expansion module address space. This is used to select the mode control register.

- 2) The mode control register. U5, is a 4 bit, write only latch. By writing to this register, the processor selects which of the "socket(s)" appears in the 16K byte address space, and whether they are ROM or RAM.

### **FUNCTIONAL DESCRIPTION**

| radie 1. The functions of the control register a | The functions of the control register | аге: |

|--------------------------------------------------|---------------------------------------|------|

|--------------------------------------------------|---------------------------------------|------|

| B1 | В0 | JUMPER<br>8K/16K RAM | SOCKETS SELECTED |                                 |  |