# **Reference Manual**

**Preliminary Copy**

## **Reference Manual**

1

4

t :

# **Preliminary Copy**

4755 Walnut Street Boulder, Colorado 80301 (303) 449-8803 TLX: 752267 FHL BLDR TWX: 910-997-0429 EASYLINK: 62317580

PART NUMBER 202 24500

•

### FCC Compliance

This equipment generates and uses radio frequency energy and if not installed and used properly, i.e., in strict accordance with the operating instructions, reference manuals, and the service manual, may cause interference to radio or television reception. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial installation. If this equipment does cause interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- 1) Reorient the receiving antenna.

- 2) Relocate the equipment with respect to the receiver.

- 3) Move the equipment away from the receiver.

- 4) Plug the equipment into a different outlet so that equipment and receiver are on different branch circuits.

If necessary, consult your dealer service representative for additional suggestions.

The manufacturer is not responsible for any radio or TV interference caused by unauthorized modifications to this equipment. It is the responsibility of the user to correct such interference.

### POWERFRAME COMPONENTS

•

•

·

#### CHAPTER 3

#### 11/23+ MICROCOMPUTER

#### INTRODUCTION

The compact 11/23+ microcomputer system is designed to increase system performance and provide efficient backplane utilization. This low-cost, 16-bit microcomputer can address up to four full megabytes of parity MOS MSV11-P memory while offering full processor functionality. It is compatible with a wide range of software and hardware design, using the Extended Q-Bus.

The 11/23+ CPU module contains diagnostic and bootstrap ROM, a memory management unit, line-time clock, two asynchronous serial lines, and three sockets for the Commercial Instruction Set (CIS) and Floating Point Instruction Set options. Because of this unique packaging density, most applications will fit in a single PowerFrame unit.

SPECIFICATIONS

IdentificationKDF11-BSizeQuadDimensionsCPU chassis is 13.2 cm high × 48.3<br/>cm wide × 68 cm deep (5.2 in × 19<br/>in × 26.8 in)Power Consumption+5V+5V5%, at 6.4 A max. (at 4.5 A typ)<br/>+12VBus Loads2 AC unit loads

۰.

1 DC unit load -40 C to 66 C (-40 F to 151 F), 10% Non-operating Environment to 90% relative humidity, noncondensing Operating Environment 5 C to 50 C (41 F to 122 F), 10% to 95% relative humidity Maximum outlet temperature rise of 5 C (9 F) above 60 C (140 F) To 15.25 km (50,000 feet) for non-Altitude operating environment. To 2.44 km (8000 feet) for operating environment. Instruction Timins Based on 75 ns intervals (see Appendix) J) Interrupt Latency 5.7 microseconds (typical) 12.6 microseconds, max. (except EIS) 54.225 microseconds, max. (including EIS) Interrupt Service Time 8.625 microseconds (memory management off) 9.750 microseconds (memory management on) DMA Latency 1.35 microseconds, max. NOTE: Interrupt and DMA latencies assume a KDF11-B with memory management enabled and using MSV11-P Memory.

DESCRIPTION Central Processor

The 11/23+ central processing unit is contained on two LSI chips, control and data, which reside on a single 40-pin carrier (a dual in-line package). The standard Memory Management Unit (MMU) is contained on one LSI chip which also resides on a 40-pin carrier. 11/23+ contains sockets for these two carriers, plus three extra sockets which are reserved for the Commercial Instruction Set (CIS) or floating point options.

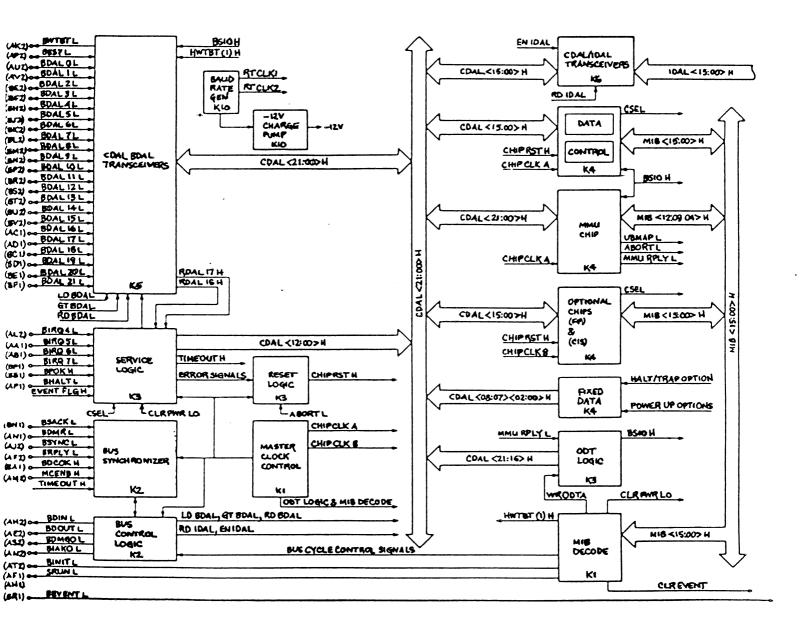

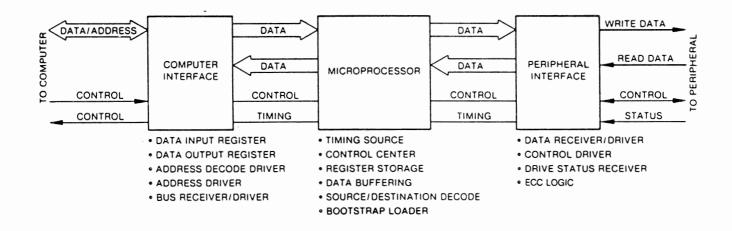

The architecture of the 11/23+ is highly expandable because of its internal bus structure. The control and data chips communicate with each other, as well as with the external 11/23+ logic, over the Micro Installation Bus (MIB) <15:00> and Chip Data and Address Line (CDAL) <21:00> bus. 11/23+ logic interfaces

these chips to the Internal Data and Address Line (IDAL) <15:00> bus and the external Extended Q-Bus. The IDAL bus provides additional loading capacity on the chip set bus. For an illustration of the positions of these busses, please refer to Figure 3-1, the 11/23+ functional block diagram.

FIGURE 3-1 - Functional Block Diagram

The 11/23+ boot and diagnostic ROMs, line clock, and serial line units reside on the IDAL bus. Memory and additional peripherals interface to the Extended Q-Bus. Bidirectional interfaces (CDAL/IDAL) transceivers and CDAL/BDAL transceivers on the 11/23+ CPU module connect the CDAL <21:00> bus with the IDAL <15:00> bus. 11/23+ logic supporting LSI chip set includes the master clock control logic, MIB decode logic, fixed data logic, service logic, reset logic, and ODT logic. Logic pertaining to the Extended Q-Bus includes the bus control logic, bus synchronizer, and the CDAL/BDAL transceivers. Logic pertaining to the IDAL transceivers. Logic pertaining to the IDAL data synchronizer, and the CDAL/BDAL transceivers. Logic pertaining to the IDAL address decode, the boot/diagnostic ROMs, the line clock logic, the console and second SLU logic, the baud rate generator, and the -12V charge pump circuits.

Floating Point Option

Forty-six floating point instructions are available as a microcode option (KEF11-A) on the 11/23+ processor to supplement the integer arithmetic instructions in the basic instruction set. The Floating Point Instruction Set executes floating point operations much faster than equivalent software routines. It also provides both single-precision (32-bit) and double-precision (64-bit) operands, and conserves memory space by executing in microcode instead of software. This option implements the same Floating Point Instruction Set available with the 11/34, 11/60, and 11/70 minicomputers.

Commercial Instruction Set

The Commercial Instruction Set (CIS), a microcode option, adds character string instructions to the basic 11/23+ instruction set. These character string operations implement functions of commercial data and text processing applications. CIS microcode resides in six MOS/LSI chips which are mounted on a single double-width 40-pin carrier.

Line Clock

Line frequency clock provides the system with timing information at fixed intervals. The intervals are synchronized with the line frequency of the user's input power. The line clock generates bus request level 6 interrupts to the processor at time intervals determined by the BEVENT L signal. The BEVNT L signal is obtained from the power supply via module pin BR1 at 16 2/3 ms or 20 ms intervals, depending on the line frequency source (60 Hz or 50 Hz, respectively).

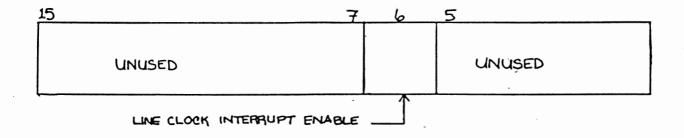

Line Clock Status Register

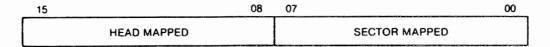

The contents of the line clock status register consist of a single read/write bit. The program communicates with the line clock via a status register at address 777 546. Program recognition of this register, along with the recognition of the boot/diagnostic registers and second wire-wrap (J11) jumper, when installed, forces the line clock interrupt enable bit to the set condition. The line clock status register bit assignment is shown below.

FIGURE 3-2 - Line Clock Status Register (LKS) 777-546

BIT: 15:7 FUNCTION: Unused

BIT: 6 (Read/Write) NAME: LINE CLOCK Interrupt Enable FUNCTION: When Set, this bit allows the BEVENT line to initiate program interrupt requests. When clear, line clock interrupts are disabled. LCIE is cleared by Power-up and BINIT. LCIE is held set when the LTC ENJ L jumper is installed.

BIT: 5:0 FUNCTION: Unused

Bootstrap/Diagnostic ROM

The bootstrap and diagnostic logic features three hardware registers and two ROM sockets for 2K, 4K, or 8K read-only memory. This 16-bit read-only memory

PAGE 3-6

contains diagnostic programs, plus a selection of bootstrap programs. These programs are user-selectable by setting eight switches on a 16-pin Dual In-Line Pack (DIP) switch pack. Programming the bootstrap and diagnostic logic consists of setting the switches for the programs desired. The bootstrap/diagnostic switch configurations and console operator responses are described in the Configuration section of this chapter. The diagnostic programs test the processor, memory, the console terminal, and the device to be bootstrapped.

The user may replace the standard ROMs with 2716-type ROMs containing programs of his/her choice, but the 11/23+ will have the functionality described above only if the standard bootstrap/diagnostic ROMs are installed in the ROM sockets.

Table 3-1 lists the error messages associated with the 11/23+ ROMs.

| ADDRESS<br>OF ERROR | DISPLAY<br>(OCTAL) | CAUSE OF ERROR                                                                                                             |

|---------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------|

| 173036              | 01                 | CP1ERR, RO contains address of error.                                                                                      |

| 0××173040           | 05                 | SLU switch selection incorrect. Error in switches.                                                                         |

| 173046              | 05                 | SLU error, CSR address for selected device<br>in error. Check CSR for selected device<br>in floating CSR address area.     |

| 173200              | 12                 | ROM Loader error. Check sum on data block.                                                                                 |

| 173232              | 02                 | Memory error 2. Write address into itself.                                                                                 |

| 173236              | 01                 | CP3ERR, RO points to cause of error.                                                                                       |

| 173240              | 01                 | CP4ERR, RO points to address of error.                                                                                     |

| 173262              | 02                 | Memory error 3. Byte addressing error.                                                                                     |

| 173302              | 02                 | Memory error in pre-memory data test.<br>R2 = Failing Data<br>R3 = Expected Data<br>R5 = Failing Address (0-776)           |

| 173316              | 02                 | Memory error. Bit 15 set in one of the<br>parity CSR's (172100-172136). Failing<br>memory should have the parity light on, |

#### TABLE 3-1 - LIST OF ERROR HALTS

| 173364                                              | 12                    | ROM Loader error. Checksum on address<br>block.                                                                                                                                                                                    |

|-----------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 173376                                              | 12                    | ROM Loader error. Jump address is odd.                                                                                                                                                                                             |

| 173526                                              | 05                    | RL01/RL02 device error.                                                                                                                                                                                                            |

| 173652                                              | 05                    | RK05 device error.                                                                                                                                                                                                                 |

| 173654                                              | 01                    | Switch mode halt. Match was not made with switches.                                                                                                                                                                                |

| 173660                                              | 02                    | Memory error in O-2044 KW 22-bit memory<br>test. Common error halt for six different<br>tests.<br>If R3-0, then error in tests 1-5.<br>R4 determines failing test.<br>R4 = Expected data<br>R5 = Failing data                      |

| CONTENTS<br>OF R4                                   | TESI                  | TEST DESCRIPTION                                                                                                                                                                                                                   |

| 20000-27776<br>177777<br>000000<br>072527<br>125125 | 1<br>2<br>3<br>4<br>5 | Address Test, bit 11 to O<br>Data Test<br>Data Test<br>Odd Parity Pattern Test<br>Byte Addressing Test                                                                                                                             |

|                                                     |                       | tests 1-5 (R3 = 0), determine 22-bit failing<br>ress as follows:                                                                                                                                                                   |

|                                                     |                       | R1 Bits 11-0 = Failing address bits 11-0.<br>R2 Bits 15-6 = Failing address bits 21-12.<br>Errors in address uniqueness test.<br>Test checks address bits 21-6, Test 6.<br>If R3 is not equal to 0, then error is in<br>this test. |

|                                                     |                       | R4 = Expected data<br>R5 = Failing data<br>R2 = 22-bit failing physical address bits<br>21-6.<br>Failing address bits 5-0 are always 0.                                                                                            |

locations 000-776. R2 = Failins data

•

Memory error in pre-memory address test for

R5 = Failing address and expected data

173664 02

- -

| 173670 | 01    | Error in CPU Test 9. JSR R3 failed.                                                  |

|--------|-------|--------------------------------------------------------------------------------------|

| 173700 | 01    | Error CPU Test 9. JSR PC failed.                                                     |

| 173704 | 05    | RX01/RX02 device error.                                                              |

| 173714 | 04    | A "NO" typed in console terminal test.                                               |

| 173736 | 02    | Memory error 1, data test failed.<br>Test O-30 Kw with MMU off if present.           |

|        |       | R1 = Failing address<br>R4 = Expected data (either 0 or 177777)<br>R5 = Failing data |

| 173740 | 01    | Error CPU Test 9. "RTS" return failed.                                               |

| 173742 | 03/04 | Console terminal test. No done flag.                                                 |

| 173760 | 05    | TU58 error halt.                                                                     |

Bootstrap and Diagnostic Registers

The bootstrap and diagnostic logic contains three hardware registers that are software-addressable. One of the registers is dual-purpose register which functions as the configuration register when read, and the display register when written. These registers are assigned separate, individual addresses that cannot be changed or modified. The particular designations and addresses of these registers are listed in Table 3-2, below. The registers and associated logic are described in the following paragraphs.

#### TABLE 3-2 - BOOTSTRAP AND DIAGNOSTIC REGISTER ASSIGNMENTS

|                           | READ/ | BIT  |         |

|---------------------------|-------|------|---------|

| REGISTER                  | WRITE | SIZE | ADDRESS |

| Page Control              | ω     | 12   | 777520  |

| Read/Write<br>Maintenance | R/W   | 16   | 777522  |

| Configuration*            | R     | 8    | 777524  |

| Display*                  | W     | 4    | 777524  |

|                           |       |      |         |

\* Dual-Purpose Register

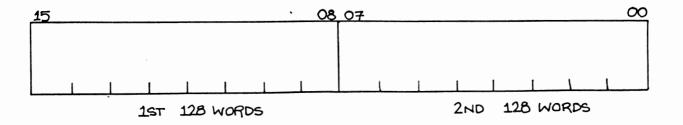

Page Control Register (PCR) 777520

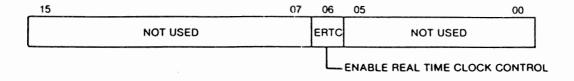

The PCR is a write-only register which is both word-addressable and byte-addressable. This register is cleared by Power-up, and when the 'Restart' switch on the CPU mounting box is activated. The PCR, in conjunction with the ROM address multiplexer, permit all 2048 locations in the 2K bootstrap/ diagnostic ROM to be accessed by 256 of the Extended Q-Bus addresses reserved for peripheral device addressing. The 256 addresses cover a byte address range of 773000-773777. Figure 3-3 illustrates the page control register.

FIGURE 3-3 - PAGE CONTROL REGISTER

The contents of the PCR are used to select any one of the 16 pages of ROM. Each page of ROM consists of 128 word locations. Table 3-3, below, describes the relationship between the PCR contents to the PCR page for pages 0-17. If the PCR is loaded with data 000400, the PCR low byte contains data 000, while the high byte contains data 001. The PCR bytes can be loaded separately. To select ROM locations 1600-1777, for example, one need only load the PCR high byte with page 7. In this example, the high byte contains 007, while the low byte is disregarded.

TABLE 3-3 - PCR CONTENTS/PAGE RELATIONSHIP, PAGES 0-17

| PCR PAGES<br>(OCTAL) | PCR CONTENTS | PCR HIGH BYTE<br>(BITS 13:08) | PCR LOW BYTE<br>(BITS 05:00) |

|----------------------|--------------|-------------------------------|------------------------------|

| 0/1                  | 000400       | 001                           | 000                          |

| 2/3                  | 001402       | 003                           | 002                          |

| 4/5                  | 002404       | 005                           | 004                          |

| 6/7                  | 003406       | 007                           | 006                          |

| 10/11                | 004410       | 011                           | 010                          |

| 12/13                | 005412       | 013                           | 012                          |

| 14/15                | 006414       | 015                           | 014                          |

| 16/17                | 007416       | 017                           | 016                          |

Read/Write Maintenance Register 777522

The read/write maintenance register (RWR) is a 16-bit read/write register which is both word- and byte-addressable. It is used by the ROM diagnostics to test various read/write functions before accessing main memory. The register is cleared by Power-up and system reset.

Configuration Resister 777524

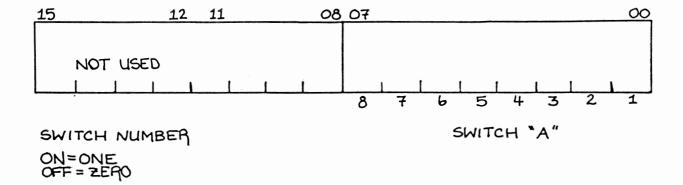

This 8-bit read-only register is used to select diagnostic programs for maintenance and/or bootstrap programs for system configuration. The boot/ diagnostic program selection procedure is described in the Configuration section of this chapter. The interpretation of the switch configuration is determined by the ROM bootstrap and diagnostic programs. The switch register is depicted

PAGE 3-12

below in Figure 3-4.

FIGURE 3-4 - SWITCH REGISTER 777524

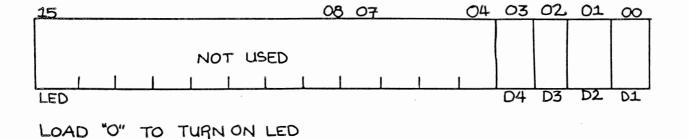

Display Register 777524

This 4-bit write-only register allows the program to control a four LED diagnostic display. Clearing one of the four display register bits lights the corresponding LED. The display register is cleared by Power-up (which turns all red LEDs on) and when the system is rebooted.

The diagnostic LED display is normally used when there is no printout on the terminal after a failure. It indicates the type of error when a failure occurs in a diagnostic test or bootstrap program. The display will indicate the type of errors described in Table 3-4, below. Figure 3-5 depicts the display register.

.

FIGURE 3-5 - DISPLAY REGISTER 777524

Standard ROMs must be installed in ROM sockets E126 (low byte) and E127 (hish byte) respectively to obtain the described errors.

TABLE 3-4 - DIAGNOSTIC LED ERROR DISPLAY\*

|                    | MSD   |       | LSD   |       |                                         |

|--------------------|-------|-------|-------|-------|-----------------------------------------|

| DISPLAY<br>(OCTAL) | BIT 3 | BIT 2 | BIT 1 | BIT O | TYPE OF ERROR                           |

| 01                 | OFF   | OFF   | OFF   | ŨN    | CPU error                               |

| 02                 | OFF   | OFF   | ON    | OFF   | Memory                                  |

| 03                 | OFF   | OFF   | ŨN    | ΩN    | Console Terminal test<br>display error  |

| 04                 | OFF   | ΩN    | OFF   | OFF   | Console Terminal test<br>kerboard error |

| 05                 | OFF   | 0N    | OFF   | ÛN    | Load device status<br>error             |

| 06                 | OFF   | ÛN    | ÛN    | OFF   | Bootstrap code<br>incorrect (NOP In-    |

.

|    |     |     |     |     | struction not in<br>location 000000)                                                                                      |

|----|-----|-----|-----|-----|---------------------------------------------------------------------------------------------------------------------------|

| 07 | OFF | ŌN  | ÓN  | ÛN  | SLU error, no response<br>from host                                                                                       |

| 10 | ON  | OFF | OFF | ÛFF | SLU received done<br>flas set                                                                                             |

| 11 | ON  | OFF | OFF | ΩN  | SLU message received<br>in DDCMP format                                                                                   |

| 12 | ŨN  | OFF | ŪN  | OFF | ROM bootstrap error                                                                                                       |

| 13 | ŨN  | OFF | ΩN  | ΟN  | Attempted access to<br>memory Loc O-6<br>failed. This failure<br>will normally occur<br>when the memory does<br>not reply |

| 17 | ON  | ΩN  | ÛN  | ΩN  | Halt switch on or<br>unable to run                                                                                        |

\* The light pattern indicates the corresponding test is in progress or failed. Some tests retry (DECnet), and others will halt the CPU (CPU, memory non-DECnet boots).

#### Serial Line Units

The two full-duplex asynchronous serial line units (console serial line unit and the second serial line unit) provide the 11/23+ (KDF11-B) with an EIA interface which is RS-232-C and RS-423 compatible. The serial line baud rates are determined by a clock signal from an internal baud rate generator or an external clock signal via connector J1 and J2. Jumpers are provided to select either the internal clock or the external clock. If the internal clock is jumper-selected, the serial line baud rates are switch-selectable from 50 to 19.2 baud. The console serial line and the second serial line may operate at different baud rates. However, a split baud rate is not possible. Each serial line must transmit and receive data at the same baud rate. If desired, 20 ma active or passive current loop operation at 110 baud may be obtained with DLV11-KA EIA to 20 ma converter option. The DLV11-KA contains a 110 baud rate clock signal which is supplied to pin 1 or the console serial line J1 and the second serial line J2 connectors.

The console serial line unit may be configured to halt in response to a break signal received from the console terminal. Both serial lines interrupt the

processor at bus interrupt priority request level 4 (BR4).

The character format for each of the serial line units selected by wire-wrap jumpers and may consist of 7 or 8 data bits, 1 or 2 stop bits, parity or no-parity, and even and odd parity.

The console serial line unit is connected to the console terminal via connector J1. The second serial line unit is connected to the line printer, the TU58 cassette tape, or an additional terminal via connector J2.

Serial Line Unit Registers

The program communicates with and transfers data to and from the external peripheral devices via four associated with each serial line. Two of the registers (RCSR and TCSR) contain control/status information for receiver and transmitter operation. The other two registers (RBUF and TBUF) contain data received from, and data to be transmitted to the peripheral device. The addresses assigned to the console and second serial line registers are listed in Table 3-5.

TABLE 3-5 - SERIAL LINE REGISTER VECTORS

| CONSOLE SERI<br>REGISTER | AL LINE<br>ADDRESS* | SECOND SERIA<br>REGISTER | L LINE<br>ADDRESS |           |

|--------------------------|---------------------|--------------------------|-------------------|-----------|

| RCSR1                    | 777560              | RCSR2                    | 776500**          | 776540*** |

| RUF1                     | 777562              | RBUF2                    | 776502            | 776542    |

| TCSR1                    | 777564              | TCSR2                    | 776504            | 776544    |

| TBUF1                    | 777566              | TBUF2                    | 776506            | 776546    |

\* DL1 DISJ L (J14) must be unprounded.

\*\* DL2 DISJ L (J13) and DL2 ADRJ L (J12) must be unprounded.

\*\*\* DL2 DISJ L (J13) must be unprounded and DL2 ADRJ L (J12) must be prounded.

PAGE 3-16

Register Bit Assignments

The console and second serial line registers have the same bit assignments with the exception of bit O of the TCSR. Bit O is used as a transmit break bit (TX BRK) in the second serial line register (TCSR2), and it is unused in the console serial line register (TCSR 1).

The bit formats for the registers are shown in the Figures below, as are the register bit assignments.

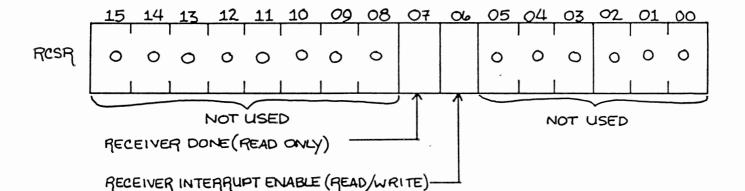

FIGURE 3-6 - RECEIVER STATUS REGISTER (RCSR 1 AND RCSR 2)

BIT: 15:8 FUNCTION: Unused. Read as zeros.

BIT: 7 (read-only) NAME: Receiver Done (RX DONE) FUNCTION: Set when an entire character has been received and is ready to be read from the RBUF register. This bit is automatically cleared when RBUF is read. It is also cleared by Power-up and Bus INIT.

BIT: 6 (Read/Write) NAME: Receiver Interrupt Enable (RX IE) FUNCTION: Cleared by Power-up and Bus INIT. If both RCVR DONE and RCVR INT ENB are set, a program interrupt is requested.

BIT: 5:0

FUNCTION: Unused. Read as zeros.

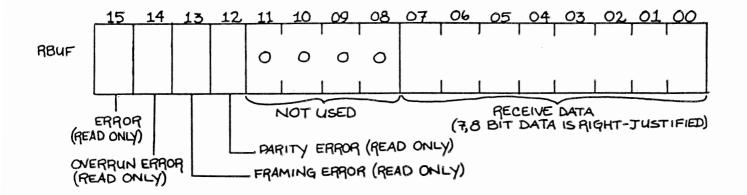

FIGURE 3-7 - RECEIVER BUFFER REGISTER (RBUF 1 AND RBUF 2)

BIT: 15 (read-only) NAME: Error (ERR) FUNCTION: Set if any RBUF bit 14:12 is set. ERR is clear if all RBUF bits 14:12 are clear. This bit cannot generate a program interrupt.

BIT: 14 (read-only) NAME: Overrun Error (OVR ERR) FUNCTION: Set if a previously received character was not read before being overwritten by the present character.

BIT: 13 (read-only) NAME: Framing Error (FRM ERR) FUNCTION: Set if the present character had no valid stop bit. Also used to detect a break condition.

BIT: 12 (read-only) NAME: Parity Error (PAR ERR) FUNCTION: Set if received parity does not asree with expected parity. Always 0 if no parity is selected.

NOTE: Error conditions remain present until the next character is received at which point, the error bits are updated. The error bits are cleared by Power-up and Bus INIT. BIT: 11:8 FUNCTION: Unused. Read as zeros.

BIT: 7:0 (read-only) NAME: Received Data Bits. FUNCTION: These bits contained the last received character. If less than eight bits are selected, the character will be right-justified with the most significant bit(s) reading zero.

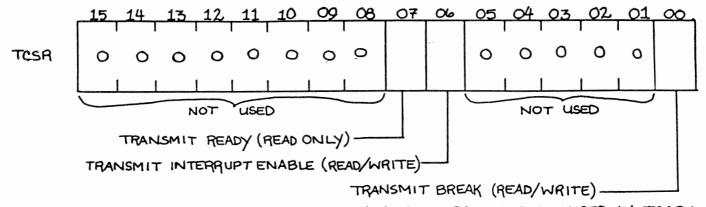

FIGURE 3-8 - TRANSMITTER/CONTROL STATUS REGISTER (TCSR 1 AND TCSR 2)

TRANSMIT BREAK BIT O IS USED ONLY IN TCSR2. IT IS NOT USED IN TCSR1.

BIT: 15:8 FUNCTION: Unused. Read as zeros.

BIT: 7 (read-only) NAME: Transmitter Ready (TX RDY). FUNCTION: Cleared when TBUF is loaded and sets when TBUF can receive another character. XMT RDY is set by Power-up and Bus INIT.

BIT: 6 (read/write) NAME: Transmitter Interrupt Enable (TX IE). FUNCTION: Cleared by Power-up and Bus INIT. If both XMT RDY and XMT INT ENB are set, a program interrupt is requested.

BIT: 5:1 FUNCTION: Unused. Read as zeros. • •

BIT: O (read/write) NAME: Break (TX BRK). FUNCTION: When set, transmits a continuous space. This bit is cleared by Power-up and System INIT. This bit is used only in TCSR2. It is unused in TCSR1.

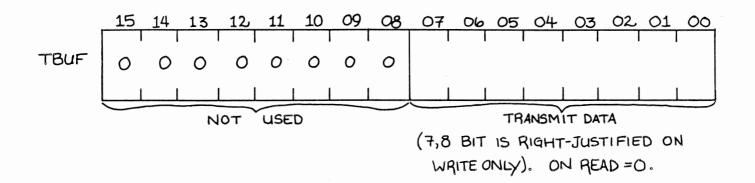

FIGURE 3-9 - TRANSMITTER BUFFER REGISTER (TBUF 1 AND TBUF 2)

BIT: 15:8 FUNCTION: Unused. Read as zeros.

BIT: 7:0 (write-only) FUNCTION: TBUF bits 7:0 are write-only bits used to load the transmitted character. If less than eight bits are selected, the character must be right-justified.

CONFIGURATION

Jumper and Switch Configuration

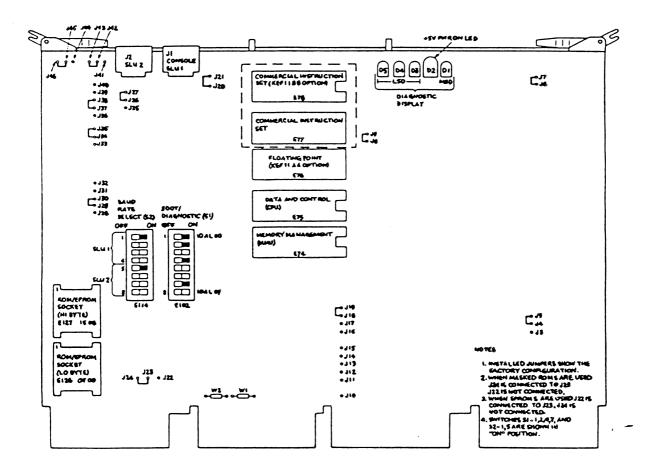

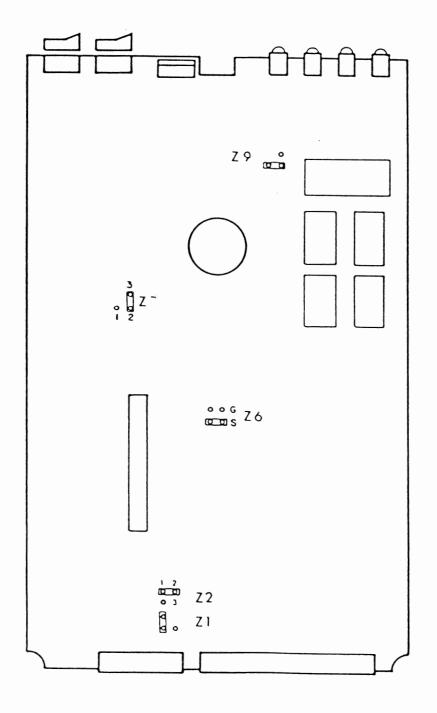

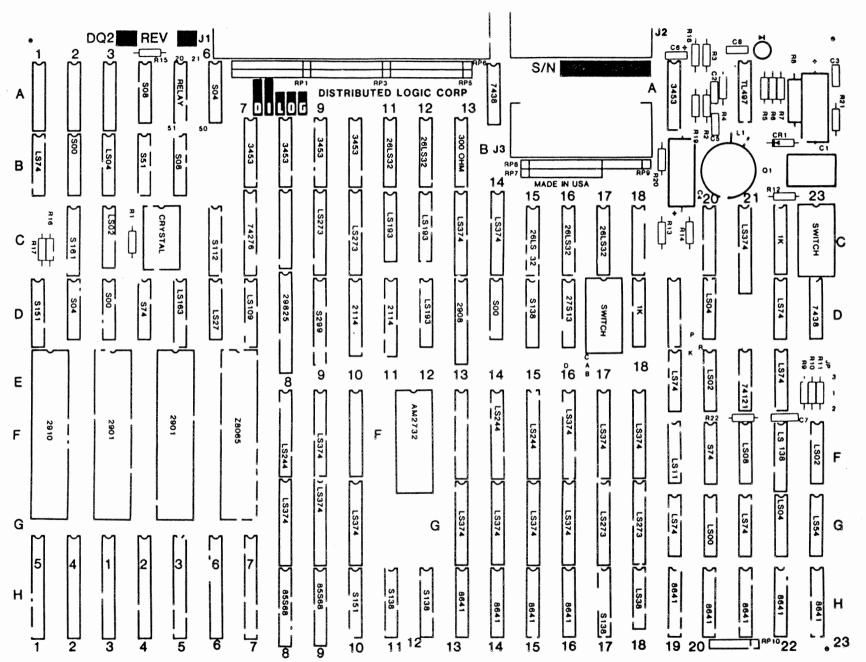

The 11/23+ contains two Dual In-Line Pack (DIP) switch units (E102 and E114) and several jumpers which allow the user to select the module features desired. The location of the switch units and jumpers is shown in Figure 3-10. The Boot/ Diagnostic switch unit (E102) consists of eight switches that let the user select boot and diagnostic programs. The second switch unit (E114) selects the baud rate for the Console SLU and the second SLU. The module contains both wire-wrap jumper stakes and soldered-in jumpers. The jumpers are divided into the following functional groups:

- 1. Test Jumpers

- 2. CPU Option Jumpers

- 3. Device Selection Jumpers

- 4. Boot and Diagnostic ROM Jumpers

- 5. SLU Character Format Jumpers

- 6. Internal/External SLU Clock Jumpers

- 7. Q-Bus Backplane Jumpers

FIGURE 3-10 - JUMPER, SWITCH AND DIAGNOSTIC DISPLAY LOCATIONS

Five jumpers are provided for manufacturing testing purposes. These jumpers must be configured as follows in Table 3-6 for normal operation.

TABLE 3-6 - MANUFACTURING TEST JUMPERS

| JUMPER |     |           |

|--------|-----|-----------|

| FROM   | то  | STATUS    |

|        |     |           |

| .16    | J7  | Installed |

| J8     | J9  | Installed |

| J20    | J21 | Installed |

| J35    | J34 | Installed |

| J33    | J34 | Removed   |

| J27    | J26 | Installed |

| J25    | J26 | Removed   |

CPU Option Jumpers

Four wire-wrap stakes provide user-selectable features associated with the operation of the CPU. The ground stake can be connected to any combination of the other three stakes to select the available features. Two power-up mode stakes select one of three power-up modes. The halt/trap stake selects the halt/trap options. Power-Up Mode Selection

The three power-up modes are available for user selection. Selection is made by installing or removing wire-wrap jumpers between jumper stakes (J17, J19) and the ground stake (J18) in various combinations. The jumper configuration for the modes are described in the Table 3-7 below.

TABLE 3-7 - POWER-UP MODE JUMPER CONFIGURATION

| MODE | NAME            | JUMPER J19 | J18 TO J17 |

|------|-----------------|------------|------------|

| 0    | PC@24, PS@26    | R*         | R          |

| 1    | Console ODT     | R          | I          |

| 2    | Bootstrap       | I          | R          |

| 3    | Not Implemented | I          | I          |

\* R = jumper removed; I = jumper installed

Power-Up Mode O (PC@24, PS@26)

This mode causes the microcode to fetch the contents of memory locations 24 and 26 and loads their contents into the PC and PS, respectively. The microcode then examines BHALT L. If BHALT L is asserted, the processor enters console ODT mode. If BHALT L is not asserted, the processor begins program execution by fetching an instruction from the location pointed to by the PC. This mode is useful when power-fail/auto restart capability is desired.

Power-Up Mode 1 (Console ODT)

This mode causes the processor to enter console ODT mode immediately after power-up regardless of the state of any service signals. This mode is useful in a program development or hardware debug environment, giving the user immediate control over the system after power-up.

Power-Up Mode 2 - Start at 773000

This mode causes the processor to internally generate a bootstrap starting address of 773000 in 16-bit mode with MMU off. This address is loaded into the PC. The processor sets the PS to 340 (PS<07:05> = 7) to inhibit interrupts before the processor is ready for them. If BHALT L is asserted, the processor enters console ODT mode. If not, the processor begins execution by fetching an instruction from the location pointed to by the PC. This mode is useful for turnkey applications where the system automatically begins operation without operator intervention.

Halt/Trap Option - J16

If the processor is in kernal mode and decodes a HALT instruction, BPOK H is tested. If BPOK H is negated, the processor will continue to test for BPOK H. The processor will perform a normal power-up sequence if BPOK H becomes asserted sometime later. If BPOK H is asserted after the HALT instructon decode, the halt/trap jumper (J16) is tested. If the jumper is removed, the processor enters console ODT mode. If the jumper is connected to J18 (ground), a trap location 10 will occur.

NOTE: In user mode a HALT instruction execution will always result in a trap to location 10 .

This feature is intended for situations, such as unattended operation, where recovery from erroneous HALT instructions is desirable. Table 3-8 describes the halt/trap jumper functions for Kernal and User processor modes.

TABLE 3-8 - HALT/TRAP JUMPER CONFIGURATION

| JUMPER<br>J18 to J16 | PROCESSOR<br>MODE | FUNCTION                                                                                                         |

|----------------------|-------------------|------------------------------------------------------------------------------------------------------------------|

| R                    | Kernal            | Processor enters Console ODT microcode<br>when it executes a HALT instruction.                                   |

| I                    | Kernal            | Processor traps to location 10 when it executes a HALT instruction.                                              |

| x                    | User              | Halt instruction decode results in a trap<br>to location 10 regardless of the status<br>of the Halt/Trap jumper. |

• • ·

#### On-Board Device Selection Jumpers

Six wire-wrap stakes on the 11/23+ module are used to select which on-board peripheral devices are enabled or disabled. The pround stake can be connected to any combination of the other five stakes to obtain the desired configuration. The jumper functions are described in Table 3-9, below.

TABLE 3-9 - ON-BOARD DEVICE SELECTION JUMPERS

STAKE NUMBER FUNCTION

- J10 This wire-wrap stake provides a ground source for the other five wire-wrap stakes in this group.

- J11 When grounded, this signal sets the line clock interrupt enable flip-flop and allows the Q-Bus BEVNT signal to request program interrupts.

- 9J15 When grounded, this signal disables the boot/ diagnostic registers, the boot/diagnostic ROMs, and the line clock register.

- J12 When J12 is ungrounded, the second SLU device and vector addresses are as follows:

| DEVICE | ADDRESSES | INTERRUPT   | VECTORS |

|--------|-----------|-------------|---------|

| RCSR   | 776500    | Receiver    | 300     |

| RBUF   | 776502    | Transmitter | 304     |

| XCSR   | 776504    |             |         |

| XBUF   | 776506    |             |         |

When J12 is grounded, the device and vector addresses are as follows:

| DEVICE | ADDRESSES | INTERRUPT   | VECTORS |

|--------|-----------|-------------|---------|

| RCSR   | 776540    | Receiver    | 340     |

| RBUF   | 776542    | Transmitter | 344     |

| XCSR   | 776544    |             |         |

| XBUF   | 776546    |             |         |

|        |           |             |         |

J13 When grounded, this signal disables the second serial line registers. When ungrounded, the device and vector addresses for the second SLU are determined by the status of the J12 jumper.

U14 When grounded, this signal disables the console serial line registers. When ungrounded, the device and vector addresses for the console SLU are the following:

| DEVICE | ADDRESSES | INTERRUPT   | VECTOR |

|--------|-----------|-------------|--------|

| RCSR   | 777560    | Receiver    | 060    |

| RBUF   | 777562    | Transmitter | 064    |

| XCSR   | 777564    |             |        |

| XBUF   | 777566    |             |        |

SLU CONNECTOR PIN FUNCTIONS

| FIN  | J1 = CONSOLE<br>SIGNAL | J2 = SECOND SLU<br>FUNCTION *                    |

|------|------------------------|--------------------------------------------------|

| 1    | EXT CLK                | Input for an external SLU clock.*                |

| 2    | Ground                 |                                                  |

| З    | XMIT+                  | Transmitter output.                              |

| 4    | Ground                 |                                                  |

| 5    | Ground                 |                                                  |

| 6    | NC                     | Key; pin not provided.                           |

| 7    | RCV-                   | Receiver input (most negative).                  |

| 8    | RCV+                   | Receiver input (most positive).                  |

| 9    | Ground                 |                                                  |

| 10   | +12V                   | Power for the DLV11-KA option.** Fused at 1A.    |

| * If | the DLV11-KA opt       | ion is installed between the console SLU and the |

\* If the DEVII-KA OPTION is installed between the Console set and the console terminal, jumper J42-J43 must be removed and jumper J42-J41 installed. \*\* This pin must be unterminated if the DEV11-KA option is not

installed.

Console SLU Switch and Jumper Configurations

Four switches of a 16-pin DIP switch pack (E114) and four jumpers provide user-selectable features associated with the operation of the console serial line unit. A jumper is available to disable the console SLU.

Console SLU Baud Rates

Switches 1 through 4 of the S2 switch pack (E114) select 1 of 16 possible SLU baud rates if the internal baud rate generator is used as the clock source. If the module is configured to operate the SLU with an external clock, the positions of these switches are meaningless. The SLU transmits and receives at the selected baud rate. Split baud operation is not provided. The switch configurations to select any one of the available baud rates are listed in Table 3-10 below:

TABLE 3-10 - CONSOLE SLU BAUD RATE SELECTION

| SWITCH POSITION |      |      |      |           |  |  |

|-----------------|------|------|------|-----------|--|--|

| S2-4            | S2-3 | S2-2 | S2-1 | BAUD RATE |  |  |

| ON              | ON   | ON   | ON   | 50        |  |  |

| ON              | ON   | ON   | OFF  | 75        |  |  |

| ON              | ON   | OFF  | ON   | 110       |  |  |

| ON              | ON   | OFF  | OFF  | 134.5     |  |  |

| ON              | OFF  | ON   | ON   | 150       |  |  |

| ON              | OFF  | ON   | OFF  | 300       |  |  |

| ON              | OFF  | OFF  | ON   | 600       |  |  |

| ON              | OFF  | OFF  | OFF  | 1200      |  |  |

| OFF             | ON   | ON   | ON   | 1800      |  |  |

| OFF             | ON   | ON   | OFF  | 2000      |  |  |

| OFF             | ON   | OFF  | ON   | 2400      |  |  |

| OFF             | ON   | OFF  | OFF  | 3600      |  |  |

| OFF             | OFF  | ON   | ON   | 4800      |  |  |

| OFF             | OFF  | ON   | OFF  | 7200      |  |  |

| OFF             | OFF  | OFF  | ON   | 9600      |  |  |

| OFF             | OFF  | OFF  | OFF  | 19,200    |  |  |

As stated previously, the UART can be configured to operate at a baud rate that is generated externally. The baud rate is inputted to the module from the external device through connector J1, pin 1. The jumper options are shown below.

| JUMPER | RATE |                                                                                            | SELECTED BAUD |          |  |

|--------|------|--------------------------------------------------------------------------------------------|---------------|----------|--|

| FROM   | то   | FUNCTION                                                                                   | INTERNAL      | EXTERNAL |  |

| J43    | J42  | Connects internal baud rate<br>generator to the console SLU<br>UART (Normal configuration) | I             | R        |  |

| 41.    | J42  | Connects external clock to the                                                             | R             | I        |  |

console SLU UART

Console SLU Character Formats

Five wire-wrap stakes select options to establish the console SLU character format. The ground stake can be connected to any combination of the other four stakes to configure the character format options.

The following table, Table 3-11, describes how to configure the character format.

TABLE 3-11 - CONSOLE SLU CHARACTER JUMPER CONFIGURATION

| JUMPER<br>FROM | TO J38**  | CHARACTER FORMAT OPTION                             |

|----------------|-----------|-----------------------------------------------------|

| J39            | IN<br>OUT | 7-bit characters<br>8-bit characters                |

| J37            | OUT<br>IN | Two stop bits<br>One stop bit                       |

| J36*           | IN<br>OUT | Parity check enabled<br>Parity check disabled       |

| J40            | IN<br>OUT | Odd parity if J36 is in<br>Even parity if J36 is in |

If 8-bit characters (J39 OUT) are selected, parity check must be disabled (J36 OUT).

\*\* J38 is the ground source for these functions. "In" means that a jumper connection is to be made to J38.

Break Halt Jumpers

Two jumpers enable and disable the Break Halt feature. If this feature is enabled, the detection of a break condition by the console UART causes the processor to halt and enter the octal debussing technique (ODT) microcode. If this feature is disabled, there is no response to the break condition. Below is Table 3-12, which lists the Break Halt Jumper configurations.

PAGE 3-27

TABLE 3-12 - BREAK HALT JUMPER CONFIGURATION

| JUMPER<br>FROM | то          | FUNCTION                          | ENABLED | BREAK FEATURE<br>DISABLED |

|----------------|-------------|-----------------------------------|---------|---------------------------|

| J5             | 4ل.         | Connects ground<br>to RQ HLT H.   | R*      | I*                        |

| - J3           | <u>.</u> 14 | Connects DL1 FE H<br>to RQ HLT H. | Ι       | R                         |

\* R = removed; I = installed

Second SLU Switch and Jumper Configurations

The second SLU is configured much the same as the console SLU, except that a different set of switches and jumpers are used to select the available SLU features. Also, the Halt/Break jumper is not present. Jumpers are also available to select the second SLU, and to select the range of addresses/vectors to be used. The switch positions for the second SLU baud rates are listed in Table 3-13.

TABLE 3-13 - SECOND SLU BAUD RATE SELECTION

| SWITCH | POSITION |      |      |           |

|--------|----------|------|------|-----------|

| S2-8   | S2-7     | S2-6 | S2-5 | BAUD RATE |

|        |          |      |      |           |

| 0N     | ON       | ON   | ON   | 50        |

| ΟN     | ON       | ON   | OFF  | 75        |

| ON     | ON       | OFF  | ON   | 110       |

| ŪN     | ON       | OFF  | OFF  | 134.5     |

| ON     | OFF      | ON   | ON   | 150       |

| ON     | OFF      | ON   | OFF  | 300       |

| ΩN     | OFF      | OFF  | ON   | 600       |

| ON     | OFF      | OFF  | OFF  | 1200      |

| OFF    | ON       | ON   | ON   | 1800      |

| OFF    | ON       | ŪN   | OFF  | 2000      |

| OFF    | ON       | OFF  | ON   | 2400      |

| OFF    | ON       | OFF  | OFF  | 3600      |

| OFF    | OFF      | ON   | ON   | 4800      |

| OFF    | OFF      | ON   | OFF  | 7200      |

| OFF    | OFF      | OFF  | ON   | 9600      |

| OFF    | OFF      | OFF  | OFF  | 19,200    |

|        |          |      |      |           |

The second SLU may be configured to operate at an externally generated baud rate. The baud rate is inputted to the module from the external device through J2, pin 1. The jumper options are:

| JUMPER<br>FROM | RATE<br>TO | FUNCTION                                                                                   | SELECTED<br>INTERNAL | BAUD<br>EXTERNAL |

|----------------|------------|--------------------------------------------------------------------------------------------|----------------------|------------------|

| J46            | J45        | Connects internal baud rate<br>senerator to the second SLU<br>UART. (Normal confisuration) | I                    | R                |

| .144           | J45        | Connects external clock to th second SLU UART.                                             | e R                  | I                |

Second SLU Character Formats

Five wire-wrap stakes select options to establish the second SLU character format. The ground stake can be connected to any combination of the other four stakes to configure the character format options.

The jumper stake functions are:

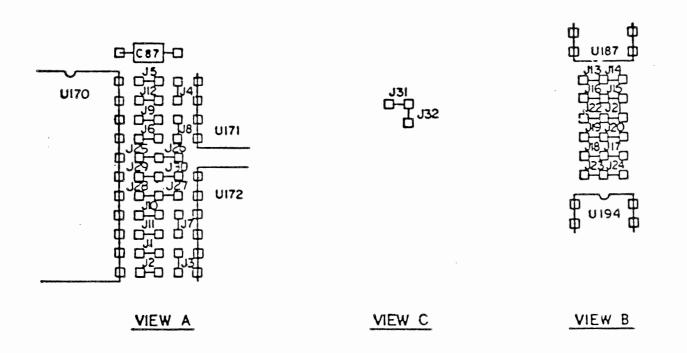

| JUMPER<br>FROM | то јзо .  | CHARACTER FORMAT OPTION                             |

|----------------|-----------|-----------------------------------------------------|

| J31            | IN<br>OUT | 7-bit characters<br>8-bit characters                |

| J29            | OUT<br>IN | Two stop bits<br>One stop it                        |

| J28*           | IN<br>OUT | Parity check enabled<br>Parity check disabled       |

| J32            | IN<br>OUT | Odd parity if J28 is in<br>Even parity if J28 is in |

\* If 8-bit characters (J31 OUT) are selected, parity check must be disabled (J28 OUT).

\*\* J30 is the ground source for these functions. "IN" means that a jumper connection is to be made to J30.

Boot/Diagnostic Switches and Jumpers

0

A 16-pin DIP switch pack (E102) and two jumpers on the 11/23+ CPU module

provide switch-selectable bootstrap and diagnostic programs for hard and floppy disks or the customer's own bootstrap program. The 11/23+ will have the functionality as described in the following sections only if 2K × 8-bit Diagnostic/Bootstrap ROMs are installed in sockets E126 and E127.

Bootstrap/Diagnostic Configuration Switches

Switches S1-1 through S1-4 are used to select a diagnostic and/or a bootstrap program. Switches S1-5 through S1-8 are used in conjunction with switches S1-3 and S1-4 to select the specific bootstrap program desired.

| S1 SWITCH | CONFIGURATION | FUNCTION                                                                                                                                           |

|-----------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1         | 0N            | When on, execute CPU diagnostic<br>upon power-up or restart                                                                                        |

| 2         | ON            | When on, execute memory diagnostic<br>upon power-up or restart                                                                                     |

| 3         | OFF           | When on, select DECnet boot (S1-4<br>through S1-7 are arguments*)                                                                                  |

| 4         | ΩN            | Select console test and dialogue<br>(S1-3 OFF)<br>When off, select turnkey boot dis-<br>patched by S1-5 through S1-8 con-<br>figuration (S1-3 OFF) |

\* DECnet boot arguments are:

| BOOT DEVICE**                               | SWITCH<br>S1-4 | POSITIONS<br>S1-5    | S1-6 | S1-7               |

|---------------------------------------------|----------------|----------------------|------|--------------------|

| DUV11                                       | ON             | X                    | X    | X                  |

| DLV11-E                                     | OFF            | ON                   | X    | OFF                |

| DLV11-F                                     | OFF            | ON                   | Х    | CIN                |

| ** DLV11-E CSR = 77<br>DLV11-F CSR = 776500 |                | DUV11 CS<br>760010 t |      | if no devices from |

X = Don't care

All boots other than the above DECnet boots are controlled by the bit patterns in the switches S1-5 through S1-8 or, if the console test is selected, a mnemonic and unit number. The console test prompts with:

TESTING MEMORY XXXX.KW Where XXXX is the decimal multiple of 1024 words of RAM START? found in the system when sized from 0 up in 1024 word increments. The first word of each 1024 word segment is read, then written back into itself. The sizing routine only sizes consecutive memory from location 0 and up.

NOTE: "Testing memory" is only printed if the memory test is selected, Turnkey mode is not selected and memory size is greater than 32 KW with memory management present.

Allowed<sup>\*</sup> responses are a two-character mnemonic with a one disit octal unit number (default 0) or one of two special single-character mnemonics. The response must be followed by a return, the special single-character mnemonics are:

'Y' Use switch settings in S1-5 through S1-8 to determine boot device

OR 'N' HALT - Enter Microcode ODT

#### "TURNKEY" BOOTSTRAP PROGRAM SELECTION

| SWITCHES | S1-5 | S1-6 | S1-7 | S1-8 | PROGRAM                      | MNEMONIC |

|----------|------|------|------|------|------------------------------|----------|

|          | OFF  | OFF  | OFF  | ON   | RK06 Boot                    | DMn n<8  |

|          | OFF  | OFF  | ON   | ON   | RL01 or RL02 Boot            | DLn n<4  |

|          | QFF  | OFF  | ŌN   | ΟN   | TU58 (SLU at<br>776500) Boot | DDn n<2  |

|          | OFF  | ON   | OFF  | OFF  | RX01 Boot                    | DXn n<2  |

|          | OFF  | ON   | ON   | OFF  | RXO2 Boot                    | DYn n<2  |

Boot and Diagnostic ROM Jumpers

Two 24-pin sockets (E126 and E127) are provided for the installation of  $2K \times 8$  ROMs or EPROMs. When EPROMs are inserted in the two ROM sockets, +5 volts must be applied to pin 21 of each socket. For all other ROMs used in this option, ROM address bit 13 (BTRA 13 H) must be applied to pin 21. Note that

#### 11/23+ MICROCOMPUTER

-

supplied devices may be either ROM or EPROM type.

| JUMPER<br>FROM | то  | MEMORY TYPE<br>ROM | EPROM |

|----------------|-----|--------------------|-------|

| J24            | J23 | Ī.★                | R*    |

| J22            | J23 | R                  | I     |

\* I = Installed, R = Removed

Q-Bus Backplane Jumpers

Two soldered jumpers must be installed when the 11/23+ is used in a backplane in which the Q-Bus (or Extended Q-Bus) is connected to both the AB and CD rows. Ford-Higgins supplied backplanes of this type include: H9270, H9275, and the DDV11-B. The jumpers provide continuity for the interrupt acknowledge (BIAK) and direct memory access grant (BDMG) Q-Bus signals.

JUMPER FUNCTION

W1 Connects backplane pins CM2 and CN2 providing continuity for BIAK L

W2 Connects backplane pins CR2 and CS2 providing continuity for BDMG L

NOTE: If the KDF11-B is installed in a LSI-11/CD Backplane (H9273-A) and the W1 and W2 jumpers are in, pin CM1 is shorted to CN1 and pin CR1 is shorted to CS1 on slot 2. Therefore, do not install peripherals in the slot immediately following the KDF11-B if they use these lines.

-

TABLE 3-14 - FACTORY JUMPER CONFIGURATION

| JUMPER           | JUMPE | R NAME          | JUMFER | STATE | FUNCTION                                                                                                                                  |

|------------------|-------|-----------------|--------|-------|-------------------------------------------------------------------------------------------------------------------------------------------|

| ω1               | ВІАК  |                 | :      | I     | Provides backplane continuity<br>for BIAK signal. Must be<br>installed when a LSI-11/<br>LSI-11 backplane is used.                        |

| W2               | BDMG  |                 | :      | I     | Provides backplane continuity<br>for BDMG signal. Must be<br>installed when a LSI-11/<br>LSI-11 backplane is used.                        |

| JUMPER<br>FROM T | JUM   | PER NAME        | JUMPER | STATE | FUNCTION                                                                                                                                  |

| J22 U            | J23   | +5V             | I      | R     | When EPROMs are used, jumper<br>J24 to J23 is removed and<br>jumper J22 to J23 is<br>installed.                                           |

| J24 J            | J23   | BTRA 13 H       |        | I     | Connects ROM address bit 13<br>to pin 21 of both ROM<br>sockets (E126 to E127)                                                            |

| J3 .             | _14   | DL1 FE H        | I      | R     | Enables BREAK HALT feature.<br>The detection of a break<br>condition by the console SLU<br>causes the processor to halt<br>and enter ODT. |

| J5 J             | _14   | DL1 FE H        | 1      | R     | No halt on break.                                                                                                                         |

| J6 .             | _17°  | Master<br>Clock |        | I     | Enables internal master<br>clock; do not remove.                                                                                          |

| J8 .             | 19    | PHASE           |        | I     | Connects PHASE signal to F11<br>chip clock drivers; do not<br>remove.                                                                     |

| J11 J            | 10    | LTC ENBJ        | L      | R     | Allows BEVENT signal to<br>request interrupts only if<br>bit 6 in the Line Clock<br>Register (777546) is set.                             |

| J12 .            | J10   | DL2 ADJR        | L      | R     | Selects the following device<br>and vector addresses for the                                                                              |

11/23+ MICROCOMPUTER

PAGE 3-34

|     |     |                              |                                      | second SLU.                                                                                                         |

|-----|-----|------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------|

|     |     | DEVICE                       | ADDRESSES                            | VECTOR ADDRESSES                                                                                                    |

|     |     | RCSR<br>RBUF<br>XCSR<br>XBUF | 776500<br>776502<br>776504<br>776506 | Receiver 300<br>Transmitter 304                                                                                     |

| J13 | J10 | DL2 DISJ L                   | R                                    | Enables the DL2 ADRJ L<br>jumper to determine the<br>device and vector addresses<br>for the second SLU.             |

| J14 | J10 | DL1 DISJ L                   | R                                    | Selects the following device<br>and vector addresses for the<br>console SLU.                                        |

|     |     | DEVICE                       | ADDRESSES                            | VECTOR ADDRESSES                                                                                                    |

|     |     | RCSR<br>RBUF<br>XCSR<br>XBUF | 776560<br>776562<br>776564<br>776566 | Receiver 060<br>Transmitter 064                                                                                     |

| J15 | J10 | BDK DISJ L                   | R                                    | Enables boot/diagnostic<br>registers, boot/diagnostic<br>ROMs and the line clk<br>register.                         |

| J16 | J18 | TRAP OPJ L                   | R                                    | Enter console ODT if the<br>processor is executing a<br>HALT instruction and the<br>processor is in Kernal<br>mode. |

| J17 | J18 | PUP CDOJ L                   | R                                    | Power-up code Bootstrap<br>bit O Power-up                                                                           |

| J19 | J18 | PUP CDIJ L                   | I                                    | Power-up code - Mode 2<br>bit 1                                                                                     |

| J20 | J21 | ХТ∟ Н                        | I                                    | Connects baud rate<br>oscillator to the baud<br>rate senerator. Removed<br>for manufacturing test<br>only.          |

| J25 | J26 | RCV IN                       | R                                    | Console Loop-back test dis-                                                                                         |

abled.

| J27  | J26  | XMIT OUT     | I  | Connects console SLU output<br>to the console SLU connector. |

|------|------|--------------|----|--------------------------------------------------------------|

| J28  | J30  | DL2 PARJ L   | R  | Disable second SLU character<br>Parity check.                |

| J29  | J30  | DL2 ST1J L   | I  | Second SLU character contains<br>one stop-bit.               |

| J31  | J30  | BL2 CH7J L   | R  | Second SLU character contains<br>8 bits.                     |

| J32  | JSO  | DL2 ODDJ L   | R  | Second SLU parity check dis-<br>abled by DL2 ODDJ L.         |

| J33  | J34  | DCOKC2B H    | R  | Installed only during manu-<br>facturing testing.            |

| J35  | J34  | LINITF (1) H | I  | BINIT L clears console SLU.                                  |

| J36  | J38  | DLI PARJ L   | R  | Disables console SLU char-<br>acter parity check.            |

| J37  | J38  | DLI STIJ L   | Ι. | Console SLU character con-<br>tains one stop bit.            |

| J39  | J38  | DLI CH7J L   | R  | Console SLU character con-<br>tains 8 bits.                  |

| J40  | J38  | DLI ODDJ L   | R  | Console parity check disabled<br>by DLI PARJ L.              |

| .141 | J42  | EXT CLK 1 H  | R  | Disconnects EXT CLK 1 input<br>from the console SLU.         |

| J43  | J42  | INT CLK 1 H  | I  | Connects baud rate clock to the console SLU.                 |

| .144 | .145 | EXT CLK2 H   | R  | Disconnects EXT CLK2 input<br>from the second SLU.           |

| J46  | J45  | INT CLK2 H   | I  | Connects baud rate clock to the second SLU.                  |

# 11/23+ MICROCOMPUTER

# TABLE 3-15 - BOOTSTRAP/DIAGNOSTIC FACTORY SWITCH CONFIGURATION

|                     |                    | · · · · · · · · · · · · · · · · · · ·                    |

|---------------------|--------------------|----------------------------------------------------------|

| SWITCH S1<br>NUMBER | (E102)<br>POSITION | FUNCTION                                                 |

| 1                   | ÖN                 | Execute CPU diagnostic upon power-up or<br>restart       |

| 2                   | 0N                 | Execute Memory Diagnostic upon power-up (<br>or restart) |

| 3                   | OFF                | DECnet boot disabled                                     |

| 4                   | ON                 | Console test and dialogue Enabled                        |

| 5                   | OFF                |                                                          |

| 6                   | OFF                |                                                          |

| 7                   | ON                 | RL01/RL02 Bootstrap Program selected                     |

| 8                   | OFF                |                                                          |

|                     |                    |                                                          |

NOTE: With the switch configuration shown, the KDF11-B upon Power-Up or restart, will execute the CPU diagnostic, the Memory Diagnostic and then enter the Console test. If the operator wishes to terminate the Memory diagnostic and immediately enter the Console test, the Control/C keys must be depressed on the console terminal. If the memory test is terminated before completion, some memory locations may have wrong parity written into them.

| TABLE 3-16          | - SLU BAUD RATE    | FACTORY SWITCH CONFIGURATION                    |

|---------------------|--------------------|-------------------------------------------------|

| SWITCH S2<br>NUMBER | (E114)<br>POSITION | FUNCTION                                        |

| 1                   | ON                 |                                                 |

| 2                   | OFF                | Console SLU set for 9600 baud per Table<br>3-10 |

| 3                   | OFF                |                                                 |

| 4                   | OFF                |                                                 |

| 5                   | ON                 |                                                 |

| 6                   | OFF                |                                                 |

| 7                   | ŨFF                | Second SLU set for 9600 baud per Table<br>3-13  |

| 8                   | OFF                |                                                 |

e

.

#### CHAPTER 4

# DC40 POWER DRIVE

# INTRODUCTION

The DC40 is the first of a family of high performance 8-inch disk drives that incorporate applicable elements of Winchester/Whitney technology. Unformatted storage capacity of the DC40 is 53.2 megabytes, with 26.6 megabytes in an ANSI-standard removable cartridge and 26.6 megabytes on a fixed medium.

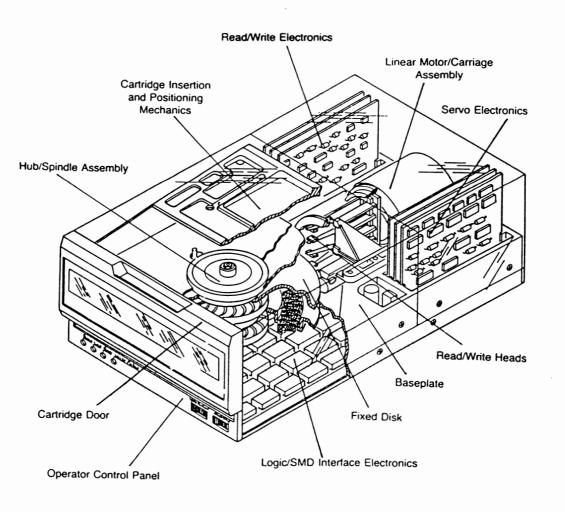

FIGURE 4-1 - DC40 BASIC COMPONENTS

# BASIC COMPONENTS

Basic components in the drive are shown in Figure 4-1. They consist of:

- -

- \* Base Plate

- \* Spindle with integral spindle drive motor and fixed disk

- \* Cartridge insertion and positioning mechanism

- \* Linear servo motor and cartridge assembly with read/write heads

- \* Read/Write electronics

.

- \* Servo Drive electronics

- \* Logic/SMD interface electronics

- \* Air cooling and filtration components

- \* Operator control switches and indicators

#### PERFORMANCE CHARACTERISTICS

The performance characteristics of the DC40 Disk Drive are shown in Table 4-1.

TABLE 4-1 - PERFORMANCE CHARACTERISTICS

|            | CAPA        | CITY      |

|------------|-------------|-----------|

|            | Unformatted | Formatted |

| Cantridge  | 26.6 Mbytes | 21 Mbytes |

| Fi≍ed Disk | 26.6 Mbytes | 21 Mbytes |

| Total      | 53.2 Mbytes | 42 Mbytes |

|  | 1 | С | Ū | ۱ħ | 1 | F | Ι | G | U | R | Α | Т | Ι | Ū١ | 1 |  |

|--|---|---|---|----|---|---|---|---|---|---|---|---|---|----|---|--|

|--|---|---|---|----|---|---|---|---|---|---|---|---|---|----|---|--|

| Number of Disks    | 1 Fixed, 1 Removable (Cartridge) |

|--------------------|----------------------------------|

| Data Surfaces      | 2 Fixed, 2 Removable             |

| Data Heads         | 4 (1 per surface)                |

| Servo              | Embedded                         |

| Tracks per Surface | <u>6.44</u>                      |

| Track Density      | 555 Tracks per Inch              |

| Track Capacity     | Unformatted: 20,672 Bytes        |

|                    | Formatted: 16,384 Bytes          |

,

|                       | PERFORMANCE                              |

|-----------------------|------------------------------------------|

| Actuator              | Linear Voice-Coil Motor                  |

| herearer -            | Lined Voice coll noto:                   |

| Access Time (Seek and | Latency)                                 |

|                       | Track to Track: 10 msec.                 |

|                       | Averase: 35 msec.                        |

|                       | Maximum: 55 msec.                        |

| Average Latency       | 8.45 msec.                               |

| Rotation Speed        | 3545 RPM                                 |

| Data Transfer Rate    | 1.229 Mbytes/sec.                        |

| Start Time            | 45 seconds                               |

| Stop Time             | 15 seconds                               |

| Stop Time (Power off) | 120 seconds                              |

|                       | READ/WRITE                               |

| Interface             | SMD                                      |

| Recording Method      | Whitney, 2-of-7 run length limit<br>code |

|                       |                                          |

Recording Density 10,889 bits/inch Flux Density 7259 flux-reversals/inch

# PHYSICAL DIMENSIONS

| Drive     | Height<br>Width<br>Depth | 4.62 in<br>8.55 in<br>14.00 in<br>24.255 | (117.4mm)<br>(217.1)<br>(355.6mm) |

|-----------|--------------------------|------------------------------------------|-----------------------------------|

| Cartridge | Weight                   | 26 lbs                                   | (11.8kg)                          |

|           | Height                   | 1.0 in                                   | (25mm)                            |

|           | Width                    | 8.2 in                                   | (208mm)                           |

|           | Depth                    | 8.3 in                                   | (211mm)                           |

|           | Weight                   | 1.5 lbs                                  | (0.7kg)                           |

•

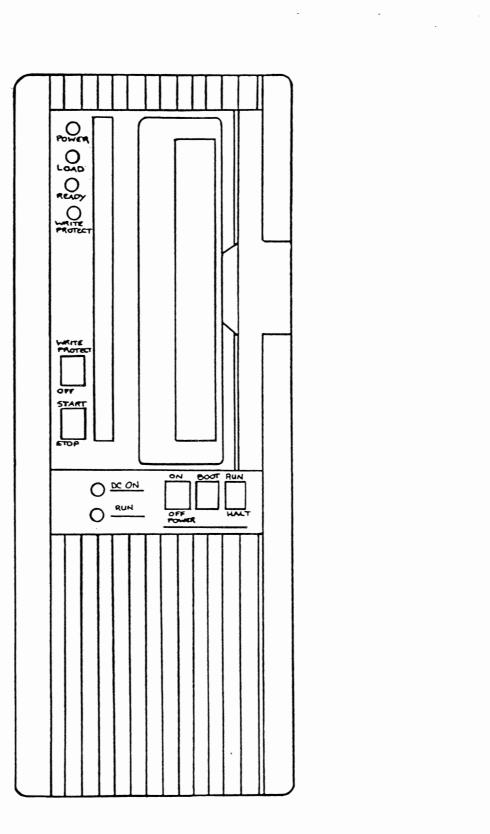

FIGURE 4-2 - OPERATOR CONTROL PANEL

.

DC40 POWER DRIVE

OPERATION

Operator Controls and Indicators

The locations of the operator controls and indicators are shown in Figure 4-2. All operator controls and indicators are on the front panel. A full operational description of these controls and indicators are given in Table 4-2.

TABLE 4-2 - CONTROLS AND INDICATORS

CONTROL OR O INDICATOR D

OPERATIONAL DESCRIPTION

START/STOP To initiate a spin-up and load heads sequencing of Rocker Switch the drive, assuming the following conditions have been met.

- A. All proper DC power has been provided

- B. The cartridge is loaded

- C. The cartridge door is closed and locked

- D. The head carriage is home, in its unloaded position

- E. The local mode option is selected (if the remote option is selected, the hold control line should be at a low logic level)

Pressing the START switch energizes the spin motor and brings the disks up to normal speed, while a purge period is under way. After the purge period the heads are loaded onto the disks and a seek to cylinder zero is performed.

During the start sequence a resident set of diagnostics will have been executed.

Drive Ready is achieved in 45 seconds and is indicated when the Ready indicator is lit.

Pressing the STOP switch during the spin-up sequencing, or when the drive is Ready initiates head retract to the home position and spindle braking. This requires approximately 15 seconds for the complete spin-down sequence. When the LOAD indicator is lit, the cartridge may be removed. An automatic safety latch secures

PAGE 4-5

the cartridge access door closed any time the LOAD indicator is not lit.

The START/STOP switch will also clear a primary fault and initiate a reset procedure by cycling the switch from its current position and then back again. See "ERROR CONDITIONS AND ACTIONS."

WRITE PROTECT Allows the operator to place the drive's Rocker Switch fixed media in read-only mode for file protection purposes. Pressing this switch will turn on or off the Write Protect indicator (towards indicators: on; away from indicators: off). When the indicator is lit, writing on the fixed disk is inhibited, and any command to write in the protected file will cause an error. To update fixed volume data the Write Protect indicator must be turned off, allowing both reading and writing.

> The Write Protect switch will also clear a secondary type of device fault and initiate a recovery procedure by cycling the switch from its current position and then back again. See "ERROR COND-ITIONS AND ACTIONS."

Write Protect status for the removable cartridge is governed by a removable write enable tab on the back of the cartridge. When the tab is removed, writing in the removable volume is inhibited. Any command to write in the protected files will cause an error condition.

POWER LED Indicator

Indicates that DC power is on.

LOAD LED Indicator

READY LED Indicator

WRITE PROTECT LED Indicator indicates that DC Power is on.

Indicates that drive is available for disk cartridge insertion or removal.

Indicates that drive is ready to receive commands for data transfer to/from host.

Indicates that fixed media has been write protected. Note: When any of the indicators are flashing on and off, an error condition code is being indicated to the operator. Refer to section on error conditions and actions.

**Operating Procedures**

The following procedures are for normal day to day use and should only be performed after installation and initial checkout has been performed.

#### Power UP

Apply power to disk system power supplies or with the optional DC power supply place the ON/OFF switch to ON. Both the POWER and LOAD indicators should now be

#### Start/Spin-Up

- Install disk cartridge as per the "CARTRIDGE INSTALLATION" procedure.

- Place START/STOP switch to start. The LOAD indicator will extinguish as the cartridge door is locked and the spin motor comes up to speed.

- Within 50 seconds the READY indicator should illuminate. If after 50 seconds the READY indicator is not lit, an error condition may exist; see the procedure on error conditions and actions.

### Write Protect

- Remove write tab from disk cartridge as shown in Figure 4-3.

- 2. Perform Start/Spin-Up procedure.

- Place drive in Write Protect mode by depressing the WRITE PROTECT switch. The WRITE PROTECT indicator should now be lit.

#### Stop/Spin-Down

1. Depress the START/STOP switch to STOP. The READY indicator will

.

extinguish as the spin motor spins down. After 10 seconds the spin motor should have stopped and the LOAD indicator illuminated.

Remove the disk cartridge, if desired, as per the "Normal Cartridge Removal" procedure. Remember the cartridge door does not unlock until the LOAD indicator is lit.

Power Down

Remove power to the disk system power supplies or with optional DC power supply place the ON/OFF switch to OFF. All indicators should now be off. With no power present it is impossible to open the cartridge normally. See the "Emergency Cartridge Removal" procedure.

### Cartridge Handling and Storage

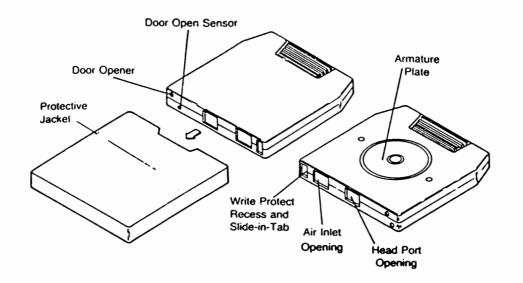

When handling or storing the removable disk cartridge, shown in Figure 4-3, the following practices should be observed.

- Never manually try to open the door to the air inlet and head port openings.

- Store the disk cartridge in its protective jacket when not inserted in the drive.

- Avoid stacking the disk cartridges on one another. Cartridges can be stored on edge or flat.

- When the cartridge is removed from its protective jacket, store the jacket in such a way as to prevent dust from collecting inside.

- 5. Disk cartridges should be stored in a cool, dry place and kept free of dust accumulations. Preferably stored in the same computer room or office as the drive or in an equally clean and temperate environment.

- 6. Cartridges should be kept away from magnetic sources. Do not place cartridges on top of drive enclosure or near CRT displays.

- Keep cartridges out of direct sunlight and away from sources of heat.

### FIGURE 4-3 - REMOVABLE DISK CARTRIDGE

Cartridge Stabilization

The removable disk cartridge must be allowed to stabilize to the same temperature as the drive at least one hour prior to installation and use. In the event a cartridge is brought in from a temperature environment significantly colder than the operating temperature, below 60 degrees F (16 C), the possibility of condensation in the cartridge exists. If condensation occurs, disk cartridges should not be used for at least 24 hours after all condensation disappears from the exterior surfaces.

Error Condition Codes

When any of the LED indicators are flashing on and off, an error condition or fault has occurred. The indicators will be flashing repetitively a three digit hexadecimal code in the form FXX, where the hexadecimal digit F indicates the start of the string and XX are the actual two digit hexadecimal error code. Table 4-3 contains all error codes and a description of each.

Operator Actions

There are two types of error conditions: primary device faults and secondary device faults. The following are a list of the required actions.

1. To clear a secondary device fault and initiate a recovery, cycle

the WRITE PROTECT switch from its current position for one complete cycle of the flashing lights, and then back again. These faults can also be cleared and recovered by issuing a fault clear command from the Controller.

- 2. To clear a primary device fault and initiate a recovery, cycle the START/STOP switch from its current position and back again.

- 3. If neither procedure seems successful or the problem persists, contact your service representative.

A list of all error codes and required operator actions are contained in Table 4-3.

TABLE 4-3 - ERROR CONDITION CODES AND OPERATOR ACTIONS

.

| ERROR<br>CODE | ERROR<br>DESCRIPTIONS                              | FAULT TYPE<br>P/S | OPERATOR<br>ACTIONS |

|---------------|----------------------------------------------------|-------------------|---------------------|

|               |                                                    |                   |                     |

| 11            | HARDWARE - Basic<br>No carriage return from termin | al P              | 2,3                 |

| 12            | Beadman timer too short                            | ai r<br>P         | 2,3                 |

| 12            | Deadman timer too long                             | Г                 | 2, C                |

| 14            | Write current unsafe                               | P                 | 2,3                 |

| 15            | Power unsafe test failed                           | P                 | 2,3                 |

| 16            | Not Used                                           |                   | 270                 |

| 17            | Not Used                                           |                   |                     |

| 18            | Not Used                                           |                   |                     |

| 19            | Not Used                                           |                   |                     |

| 1A            | Not Used                                           |                   |                     |

| 1B            | Not Used                                           |                   |                     |

| 1 C           | Download checksum error                            | P                 | 2,3                 |

| 1 D           | Not Used                                           |                   |                     |

| 1E            | Not Used                                           |                   |                     |

|               | HARDWARE - Control                                 |                   |                     |