Customer Order Number 424410284-001 NSC Publication Number 424410284-001A February 1985

$\operatorname{COPS}^{\operatorname{TM}}$

# The COPS Programming Manual

1985 National Semiconductor Corporation 2900 Semiconductor Drive P.O. Box 58090 Santa Clara, California 95052-8090

# CONTENTS

| Chapter 1 | INT | RODUCTION TO COPS MICROCONTROLLERS 1-1                                                                                            |

|-----------|-----|-----------------------------------------------------------------------------------------------------------------------------------|

|           | 1.1 | SCOPE AND PURPOSE OF THIS MANUAL                                                                                                  |

|           | 1.2 | THE COPS MICROCONTROLLER FAMILY       1-2         1.2.1 General Description       1-2         1.2.1 General Description       1-2 |

|           |     | 1.2.2 COPS ROMless Microcontrollers 1-2                                                                                           |

|           |     | 1.2.3 COPS Single-Chip Microcontrollers 1-2                                                                                       |

|           |     | 1.2.4 Conclusion                                                                                                                  |

| Chapter 2 |     | CHITECTURE OF COPS MICROCONTROLLERS 2-1                                                                                           |

|           | 2.1 | INTRODUCTION                                                                                                                      |

|           | 2.2 |                                                                                                                                   |

|           |     | 2.2.1 Program Memory – ROM                                                                                                        |

|           |     | 2.2.2 Data Memory – RAM                                                                                                           |

|           |     | 2.2.3 Subroutine Stack                                                                                                            |

|           | 2.3 | THE ARITHMETIC LOGIC UNIT                                                                                                         |

|           | 2.4 | INPUT/OUTPUT                                                                                                                      |

|           |     | 2.4.1 Inputs                                                                                                                      |

|           |     | 2.4.2 Bidirectional Tri-State I/O                                                                                                 |

|           |     | 2.4.3 Bidirectional I/O                                                                                                           |

|           |     | 2.4.4 Outputs                                                                                                                     |

|           |     | 2.4.5 The SIO Register                                                                                                            |

|           |     | 2.4.6 $Microbus^{TM}$                                                                                                             |

|           | 25  | THE ENABLE REGISTER                                                                                                               |

|           | 2)  | 2.5.1 E N <sub>0</sub> through E N <sub>3</sub> 2-12                                                                              |

|           |     | 2.5.1 E $N_0$ through E $N_3$                                                                                                     |

|           |     |                                                                                                                                   |

|           | 2.6 | INTERNAL TIMER                                                                                                                    |

|           |     | 2.6.1 Access to the Timer                                                                                                         |

|           |     | 2.6.2 External Event Counter                                                                                                      |

|           | 2.7 | OSCILLATOR AND BASIC TIMING                                                                                                       |

|           |     | 2.7.1 Clock Generator and Divider                                                                                                 |

|           |     | 2.7.2 The Instruction Cycle                                                                                                       |

|           | 2.8 |                                                                                                                                   |

| Chapter 3 | THE | E COPS INSTRUCTION SET                                                                                                            |

|           | 3.1 | BASIC CHARACTERISTICS                                                                                                             |

|           | 3.2 | DETAILED INSTRUCTION DESCRIPTION                                                                                                  |

|           | 0.2 | 3.2.1 Arithmetic/Logic Instructions                                                                                               |

|           |     | 3.2.2 Transfer of Control Instructions                                                                                            |

|           |     | 3.2.3 Memory Reference Instructions                                                                                               |

|           |     | 3.2.4 Register Reference Instructions                                                                                             |

|           |     | 3.2.5 Test Instructions                                                                                                           |

|           |     | 3.2.6 Input/Output Instructions                                                                                                   |

|           |     |                                                                                                                                   |

|           | 3.3 | NOTES ON ADDRESSING MODES                                                                                                         |

| Chapter 4 | PRC  | OGRAMMING COPS MICROCONTROLLERS    4-1                                                      |

|-----------|------|---------------------------------------------------------------------------------------------|

|           | 4.1  | INTRODUCTION                                                                                |

|           | 4.2  | BOUNDARY CONDITIONS 4-1                                                                     |

|           |      | 4.2.1 Page Boundaries                                                                       |

|           |      | 4.2.2 Block Boundaries                                                                      |

|           |      | 4.2.3 Chapter Boundaries                                                                    |

|           | 4.3  | SKIP CONDITIONS                                                                             |

|           |      | 4.3.1 Effect of Skips on Timing Loops                                                       |

|           |      | 4.3.2 Instructions That Generate a Skip                                                     |

|           | 4.4  | CARRY                                                                                       |

|           | 45   | INPUT/OUTPUT                                                                                |

|           | 7.5  | 4.5.1 Unidirectional Ports                                                                  |

|           |      | 4.5.2 Bidirectional Ports                                                                   |

|           |      | 4.5.3 The Serial I/O Port - MICROWIRE                                                       |

|           |      |                                                                                             |

|           | 4.6  | INTERRUPT                                                                                   |

|           |      | 4.6.1 Conditions for Interrupt Recognition                                                  |

|           |      | 4.6.2 Effects of Interrupt Acknowledge                                                      |

|           |      | 4.6.3 Interrupt Handling                                                                    |

|           |      | 4.6.4 Interrupt Disable                                                                     |

|           |      | 4.6.5 Interrupt in the COP440/COP2440 Series 4-11                                           |

|           | 4.7  | PROGRAM EFFICIENCY                                                                          |

|           | 4.8  | RULES AND TECHNIQUES                                                                        |

|           |      | 4.8.1 Absolute Requirements                                                                 |

|           |      | 4.8.2 General Guidelines                                                                    |

|           | 4.9  | STRUCTURED PROGRAMMING TECHNIQUES 4-16                                                      |

| Chapter 5 | ST A | ANDARD PROGRAMS                                                                             |

| Chapter 5 |      |                                                                                             |

|           |      | INTRODUCTION                                                                                |

|           | 5.2  | MATH PACK                                                                                   |

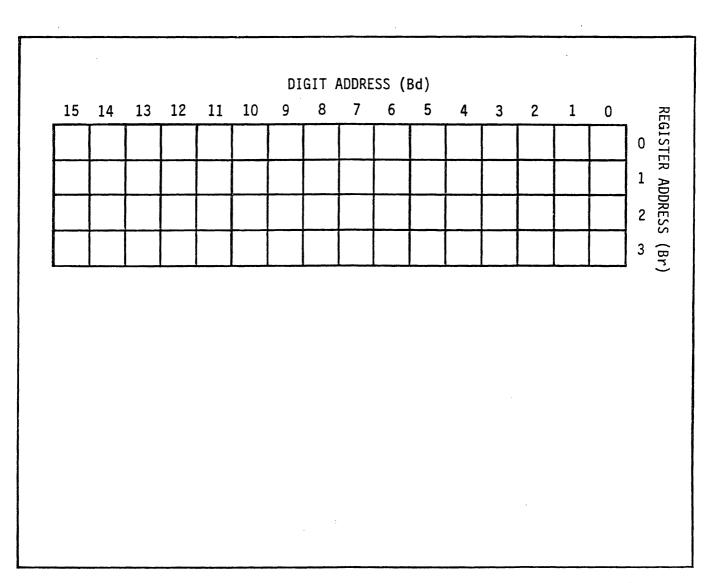

|           |      | 5.2.1 Basic Increment Routines                                                              |

|           |      | 5.2.2 Basic Decrement Routines                                                              |

|           |      | 5.2.3 Integer Addition                                                                      |

|           |      | 5.2.4 A Doubling Routine                                                                    |

|           |      | 5.2.5 Integer Subtract                                                                      |

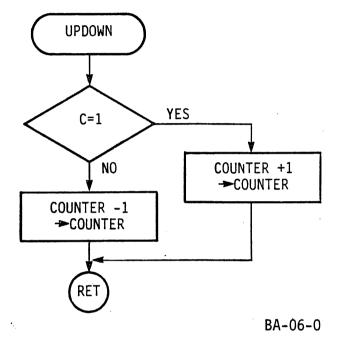

|           |      | 5.2.6 Up-Down Counters                                                                      |

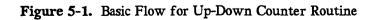

|           |      | 5.2.7 Binary Multiply                                                                       |

|           |      | 5.2.8 Basic Arithmetic Package                                                              |

|           |      | 5.2.9       Square Root       5-40         5.2.10       Binary to BCD Conversion       5-53 |

|           |      | 5.2.10 Binary to BCD Conversion                                                             |

|           |      | 5.2.11 BCD to Binary Conversion                                                             |

|           | 5.3  | TIMEKEEPING ROUTINES                                                                        |

|           | 2.0  | 5.3.1 Basic Clock Routines - External Input                                                 |

|           |      | 5.3.2 Clock Routines Based on Internal Timer                                                |

|           | E 4  |                                                                                             |

|           | э.4  | DATA MANIPULATION AND STRING OPERATIONS5-905.4.1Register Transfers5-90                      |

|           |      | 5.4.1 Register Transfers                                                                    |

|            |     | 5.4.2       | Shift  |        |       |       |      |    |     |      |    |     |    |     |    |   |   |   |   |   | 5-93  |

|------------|-----|-------------|--------|--------|-------|-------|------|----|-----|------|----|-----|----|-----|----|---|---|---|---|---|-------|

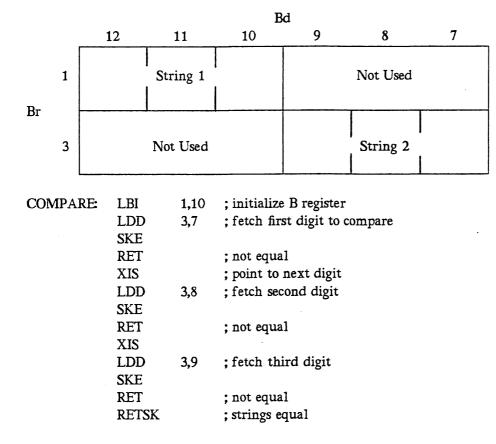

|            |     | 5.4.3       | Data/  | String | g Co  | mpar  | e    | •  | •   | •    | •  | •   | •  | •   | ٠  | • | • | • | • | • |       |

|            |     | 5.4.4       | String | g Sear | ch    |       | •    | •  | •   | •    |    | •   | •  | •   | •  | • | • | • | • | • | 5-97  |

|            |     | 5.4.5       | RAM    | Clean  | r Roi | utine | S.   | •  | •   | •    | •  | •   | •  | •   | •  | • | • | • | • | • | 5-98  |

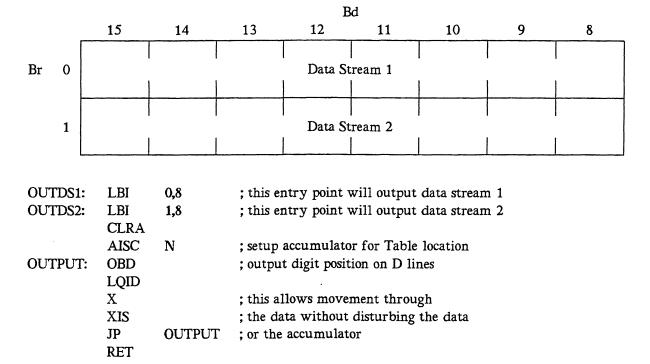

|            | 5.5 | INPUI       | C/OUT  | PUT    | •     |       | •    |    | •   | •    | •  | •   | •  |     | •  |   | • |   | • | • | 5-99  |

|            |     | 5.5.1       | Table  | Look   | . Up  | •     | •    | •  |     | •    | •  | •   | •  |     | •  | • | • | • | • | • | 5-99  |

|            |     | 5.5.2       | Micro  | bus L  | /0    |       | •    |    | •   |      | •  | •   | •  |     |    | • |   | • | • |   | 5-100 |

|            |     | 5.5.3       | Serial | I/O -  | · MI  | CRO   | WIR  | Ε  | •   | •    | •  | •   | •  |     | •  | • |   |   | • |   | 5-102 |

|            |     | 5.5.4       | -      |        |       |       |      |    |     |      |    |     |    |     |    |   |   |   |   |   | 5-105 |

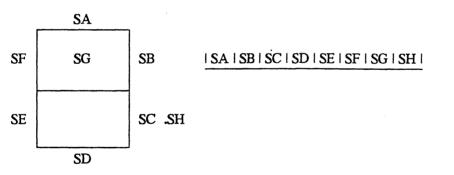

|            | 5.6 | DISPL.      | AY CO  | ONTR   | OL    |       | •    |    | •   |      |    | •   |    | •   | •  | • | • | • | • | • | 5-106 |

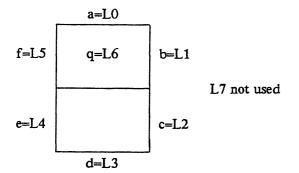

|            |     | 5.6.1       | A Fou  | ır-Dig | git N | lulti | olex | ed | Dis | spla | iy |     | •  |     | •  | • |   |   |   | • | 5-106 |

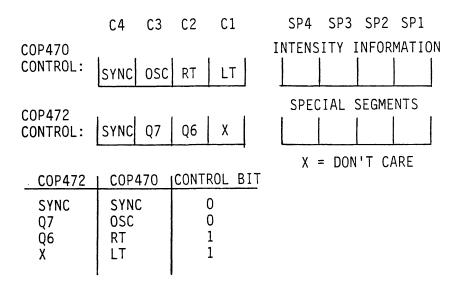

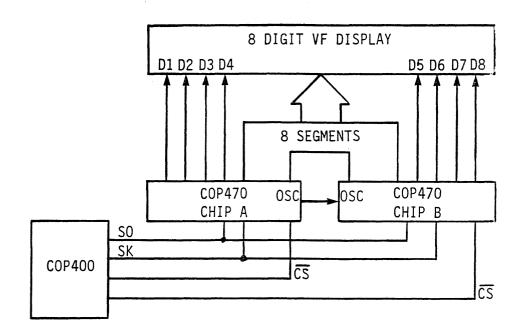

|            |     | 5.6.2       | Perip  |        |       |       |      |    |     |      |    |     |    |     |    |   |   |   |   |   | 5-111 |

|            | 5.7 | KEYBO       | DARD   | SCAI   | N     |       | •    | •  | •   | •    | •  | •   | •  | •   | •  | • | • | ٠ | • | • | 5-122 |

| Appendix A | DAT | ΓA RAN      | ИINC   | COP41  | .0L/  | 411L  | /41  | 3L | AN  | ٧D   | CC | )P4 | 10 | C/2 | 11 | С |   |   |   |   |       |

|            |     | <b>ICES</b> | • •    | • •    | •     | • •   | •    | •  | •   | •    | •  |     |    |     |    |   | • | • | • | • | A-1   |

|            | A.1 | DATA        | RAM    | DESC   | CRIF  | TION  | V    | •  | •   | •    | •  | •   | •  | •   | •  | • | • | • | • | • | A-1   |

| Appendix B | DEV | VICES V     | VITH S | SUBR   | OUI   | TINE  | ST / | AC | ΚI  | N    | RA | Μ   | •  | •   | •  | • | • | • | • | • | B-1   |

|            | B.1 | SUBRO       | )UTIN  | E ST   | ACK   | INI   | RAN  | ИĽ | DES | CF   | IP | ГІС | )N | AN  | D  |   |   |   |   |   |       |

|            |     | LOCA        |        | • •    | •     |       | •    | •  | •   | •    | •  | •   | •  | •   | •  | • | • | • | • | • | B-1   |

# FIGURES

.

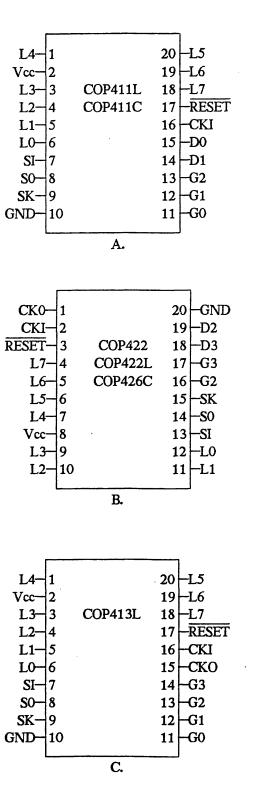

| Figure 1-1. | Pinouts for 20-Pin COPS Microcontrollers                       | -5        |

|-------------|----------------------------------------------------------------|-----------|

| Figure 1-2. | Pinout for 24-Pin COPS Microcontrollers                        | -6        |

| Figure 1-3. | Pinout for 28-Pin COPS Microcontrollers                        | -6        |

| Figure 1-4. | Pinout for 40-Pin COPS Single-Chip Microcontrollers            | <b>-7</b> |

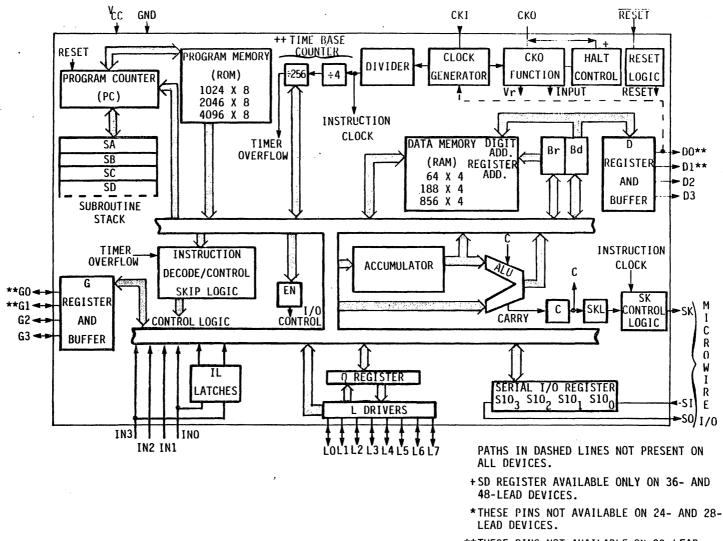

| Figure 2-1. | Basic Block Diagram for COPS Microcontrollers                  | 2-2       |

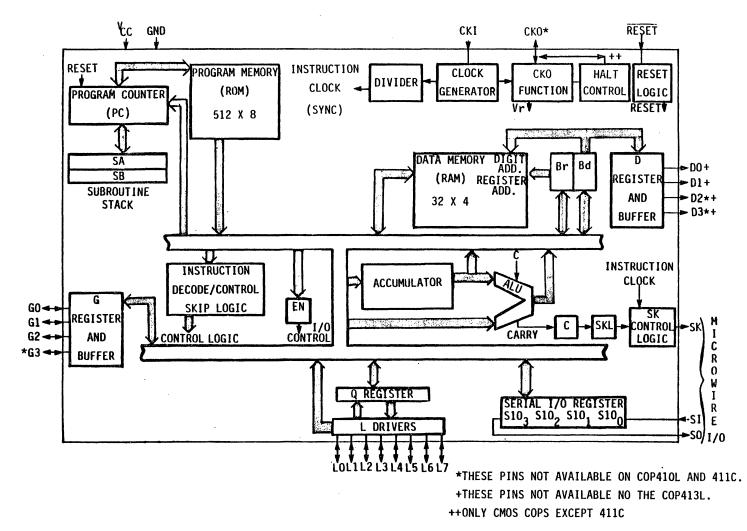

| Figure 2-2. | COP410L/411L/413L and COP410C/411C Block Diagram 2             | 2-3       |

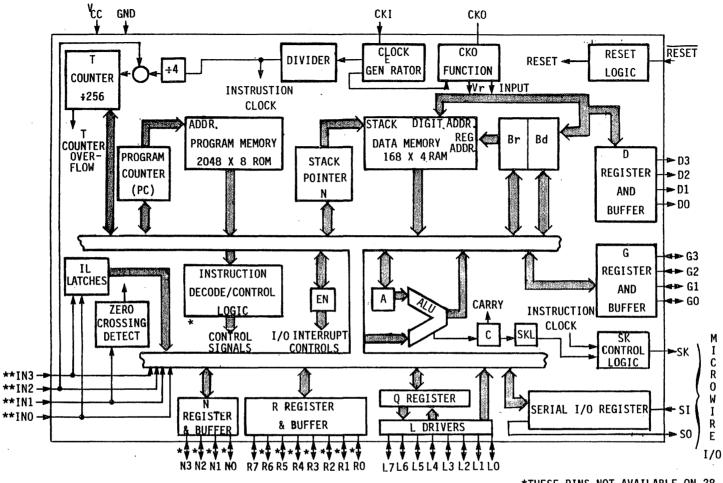

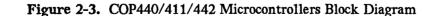

| Figure 2-3. | COP440/411/442 Microcontrollers Block Diagram                  | 2-4       |

| Figure 2-4. | COP2440/2411/2442 Dual CPU Microcontrollers - Block<br>Diagram | 2-5       |

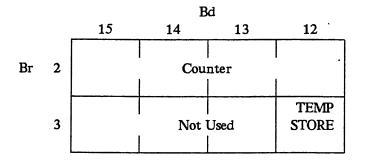

| Figure 4-1. | COP420 RAM Map                                                 | 15        |

| Figure 5-1. | Basic Flow for Up-Down Counter Routine                         | 10        |

| Figure 5-2. | Binary Multiply                                                | 14        |

| Figure 5-3. | BCD Arithmetic Package (Sheet 1 of 9)                          | 16        |

| Figure 5-3. | BCD Arithmetic Package (Sheet 2 of 9)                          | 17        |

| Figure 5-3. | BCD Arithmetic Package (Sheet 3 of 9)                          | 18        |

| Figure 5-3. | BCD Arithmetic Package (Sheet 4 of 9)                          | 19        |

|   | Figure 5-3.   | BCD Arithmetic Package (Sheet 5 of 9)                  | • | • | • | • | • | 5-20 |

|---|---------------|--------------------------------------------------------|---|---|---|---|---|------|

|   | Figure 5-3.   | BCD Arithmetic Package (Sheet 6 of 9)                  | • | • | • | • | • | 5-21 |

|   | Figure 5-3.   | BCD Arithmetic Package (Sheet 7 of 9)                  | • | • | • | • | • | 5-22 |

|   | Figure 5-3.   | BCD Arithmetic Package (Sheet 8 of 9)                  | • | • | • | • | • | 5-23 |

|   | Figure 5-3.   | BCD Arithmetic Package (Sheet 9 of 9)                  | • | • | • | • | • | 5-24 |

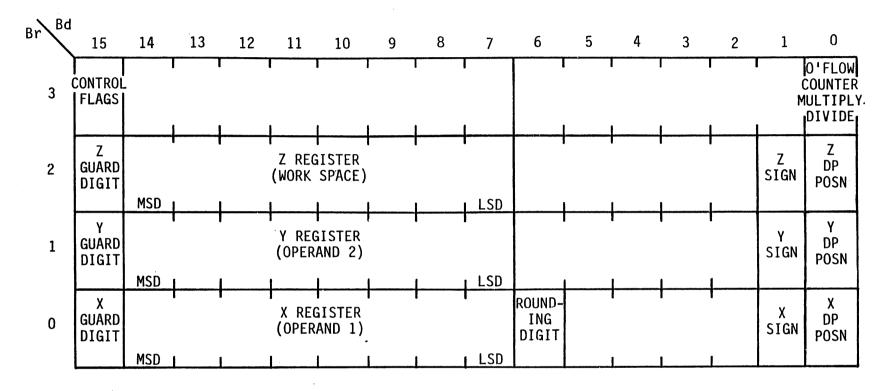

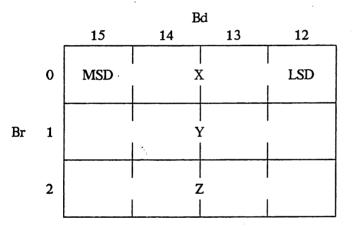

|   | Figure 5-4.   | RAM Map - Basic Arithmetic Routines                    | • | • | • | • | • | 5-25 |

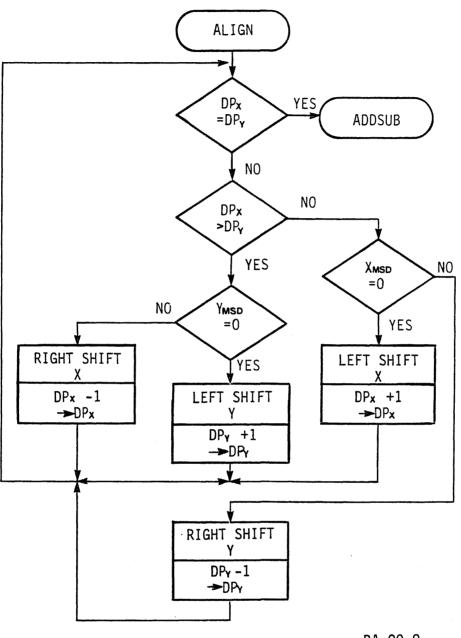

|   | Figure 5-5.   | Align Routine for Add/Subtract                         | • | • | • | • | • | 5-26 |

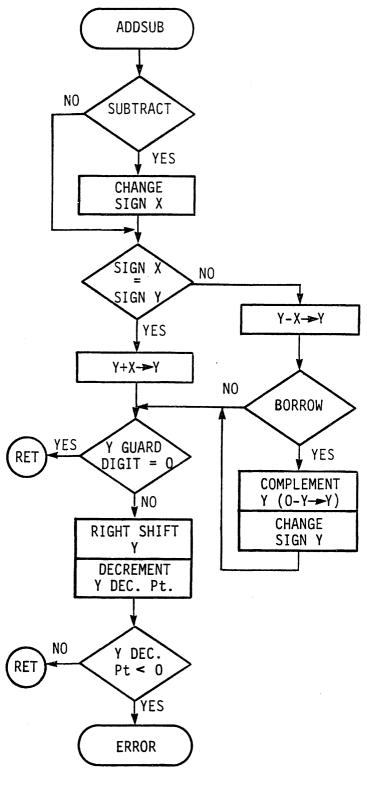

|   | Figure 5-6.   | Fully Algebraic Add/Subtract                           | • | • | • | • | • | 5-27 |

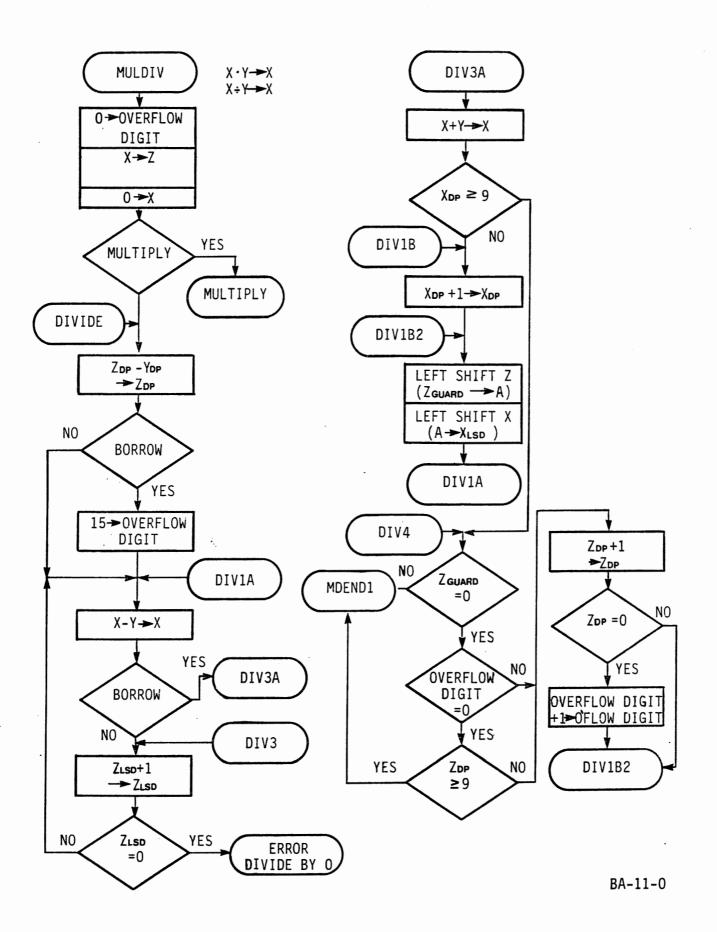

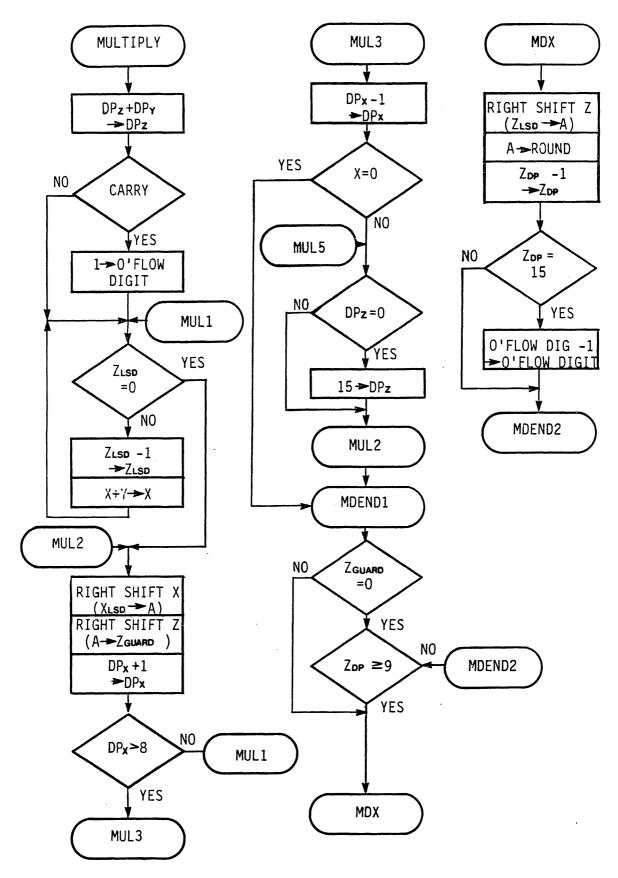

|   | Figure 5-7.   | Multiply/Divide (Sheet 1 of 3)                         | • | • | • | • | • | 5-28 |

|   | Figure 5-7.   | Multiply/Divide (Sheet 2 of 3)                         | • | • | • | • | • | 5-29 |

|   | Figure 5-7.   | Multiply/Divide (Sheet 3 of 3)                         | • | • | • | • | • | 5-30 |

|   | Figure 5-8.   | Binary (Hexadecimal) Arithmetic Package (Sheet 1 of 9) | • | • | • | • | • | 5-31 |

|   | Figure 5-8.   | Binary (Hexadecimal) Arithmetic Package (Sheet 2 of 9) | • | • | • | • | • | 5-32 |

|   | Figure 5-8.   | Binary (Hexadecimal) Arithmetic Package (Sheet 3 of 9) | • | • | • | • | • | 5-33 |

|   | Figure 5-8.   | Binary (Hexadecimal) Arithmetic Package (Sheet 4 of 9) | • | • | • | • | • | 5-34 |

|   | Figure 5-8.   | Binary (Hexadecimal) Arithmetic Package (Sheet 5 of 9) | • | • | • | • | • | 5-35 |

|   | Figure 5-8.   | Binary (Hexadecimal) Arithmetic Package (Sheet 6 of 9) | • | • | • | • | • | 5-36 |

|   | Figure 5-8.   | Binary (Hexadecimal) Arithmetic Package (Sheet 7 of 9) | • | • | • | • | • | 5-37 |

|   | Figure 5-8.   | Binary (Hexadecimal) Arithmetic Package (Sheet 8 of 9) | • | • | • | • | • | 5-38 |

|   | Figure 5-8.   | Binary (Hexadecimal) Arithmetic Package (Sheet 9 of 9) | • | • | • | • | • | 5-39 |

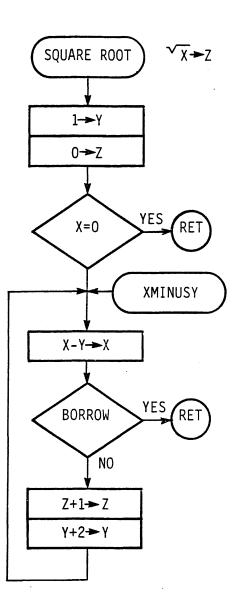

|   | Figure 5-9.   | Integer Square Root                                    | • | • | • | • | • | 5-41 |

|   | Figure 5-10.  | Square Root - General Flow Chart                       | • | • | • | • | • | 5-44 |

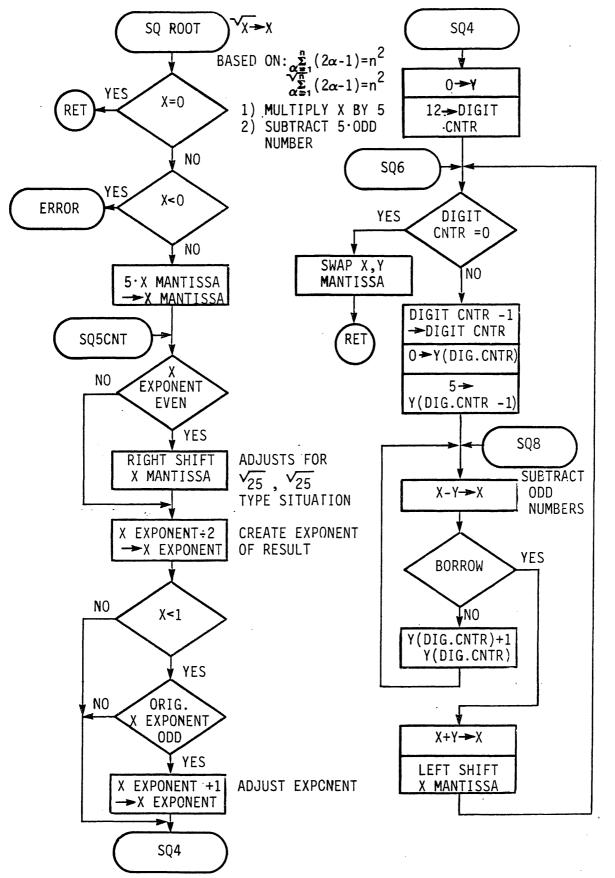

|   | Figure 5-10a. | Square Root - Detailed Flow Chart (Sheet 1 of 2)       | • | • | • | • | • | 5-45 |

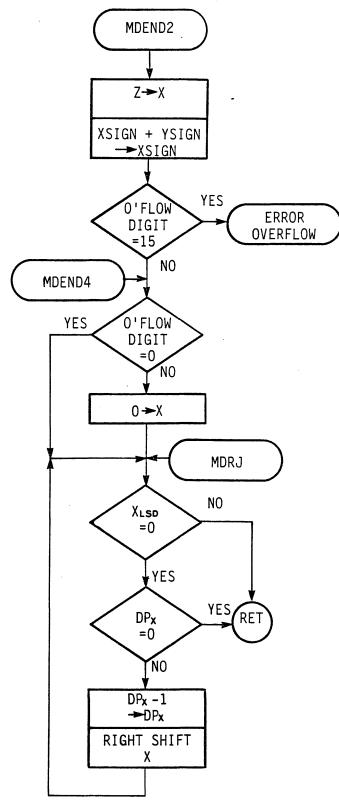

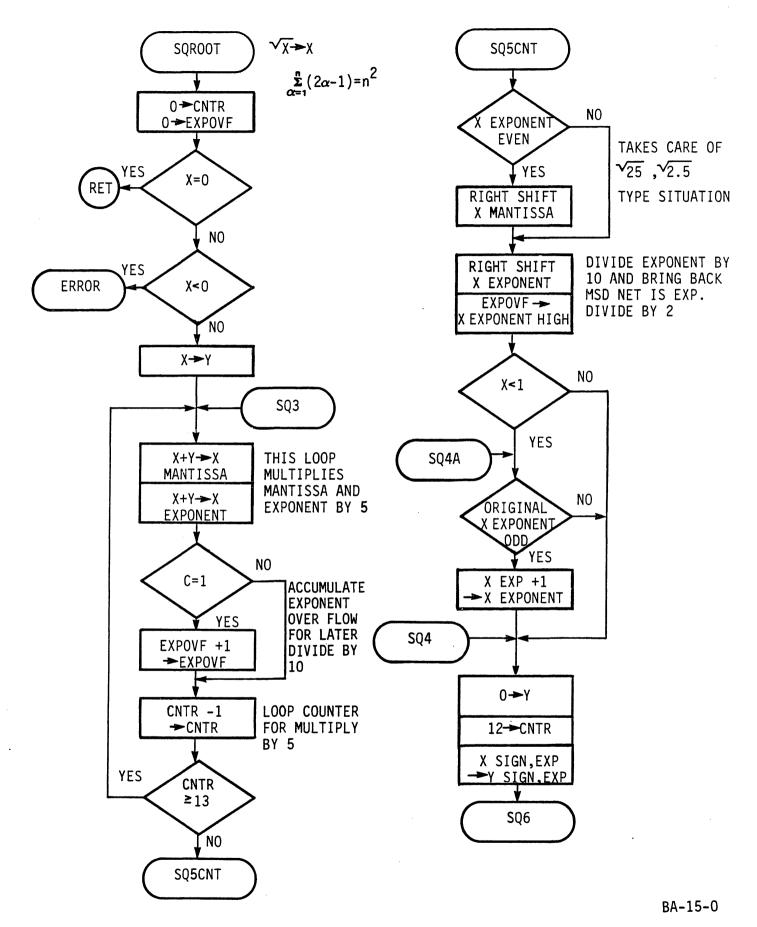

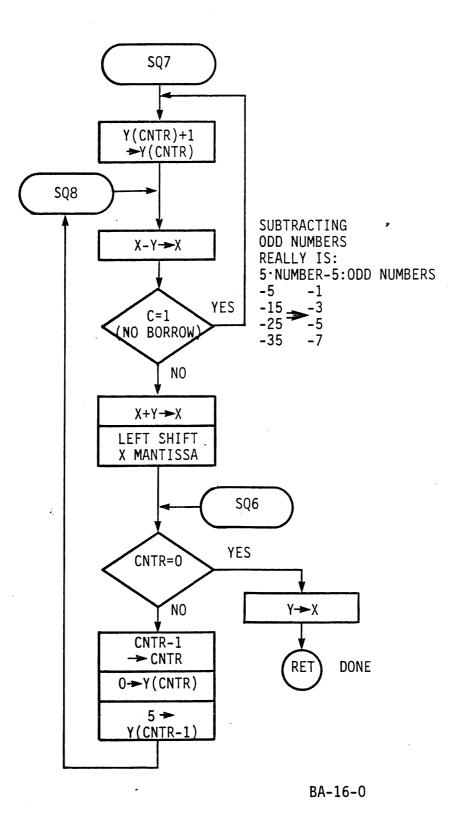

|   | Figure 5-10a. | Square Root - Detailed Flow Chart (Sheet 2 of 2)       | • | • | • | • | • | 5-46 |

|   | Figure 5-11.  | Square Root Routine (Sheet 1 of 6)                     | • | • | • | • | • | 5-47 |

|   | Figure 5-11.  | Square Root Routine (Sheet 2 of 6)                     | • | • | • | • | • | 5-48 |

|   | Figure 5-11.  | Square Root Routine (Sheet 3 of 6)                     | • | • | • | • | • | 5-49 |

|   | Figure 5-11.  | Square Root Routine (Sheet 4 of 6)                     | • | • | • | • | • | 5-50 |

|   | Figure 5-11.  | Square Root Routine (Sheet 5 of 6)                     | • | • | • | • | • | 5-51 |

| • | Figure 5-11.  | Square Root Routine (Sheet 6 of 6)                     | • | • | • | • | • | 5-52 |

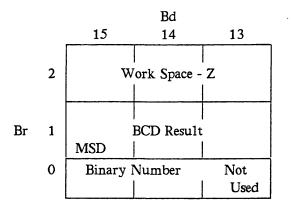

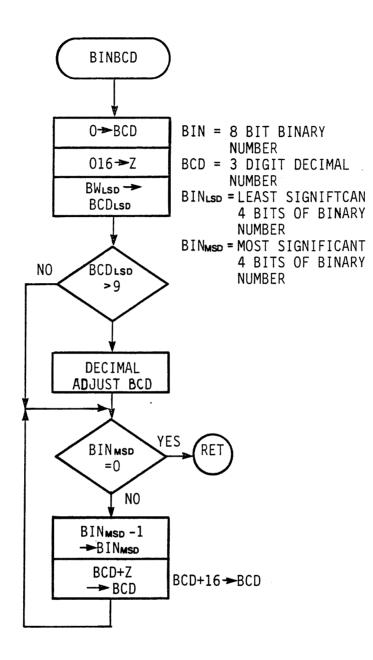

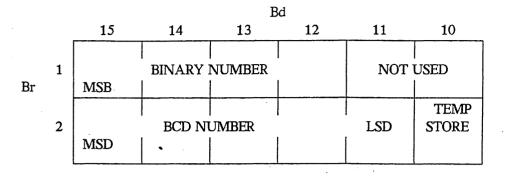

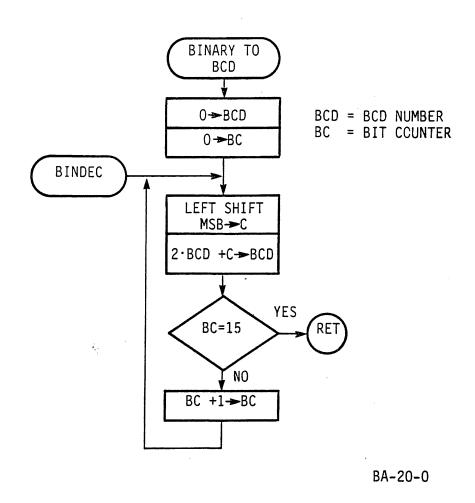

|   | Figure 5-12.  | Eight-Bit Binary to BCD Conversion                     | • | • | • | • | • | 5-54 |

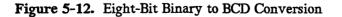

|   | Figure 5-13.  | Binary to BCD Conversion – Basic Doubling Algorithm    | • | • | • | • | • | 5-61 |

|   | Figure 5-14.  | RAM Map for Doubling Algorithm Straight-Forward        |   |   |   |   |   |      |

|   |               | Implementation                                         | • | • | • | • | • | 5-62 |

|   | Figure 5-15.  | Flow Chart for Variation 1                             | • | • | • | • | • | 5-64 |

| Figure 5-16. | RAM Map for Variation 1 on the Doubling Algorithm 5-65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5-17. | RAM Map for Binary to BCD Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

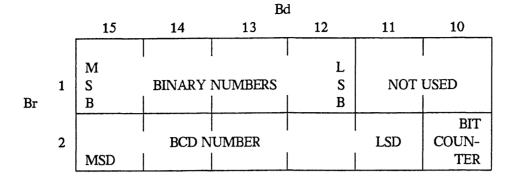

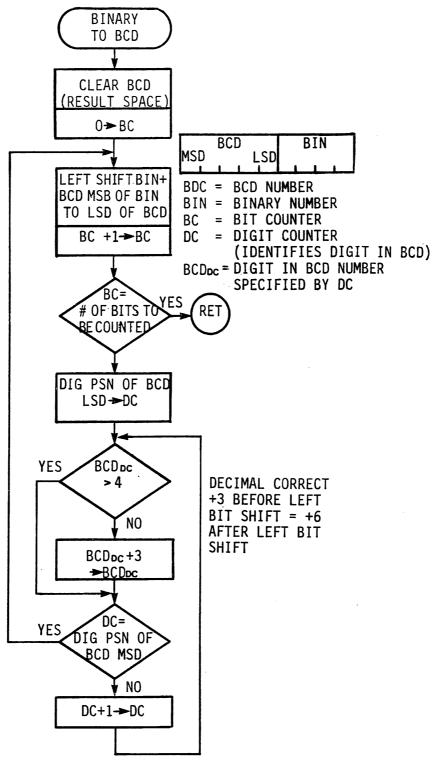

| Figure 5-18. | Binary to BCD Conversion – Shifting Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

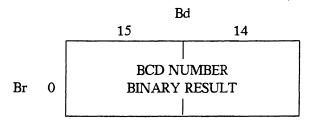

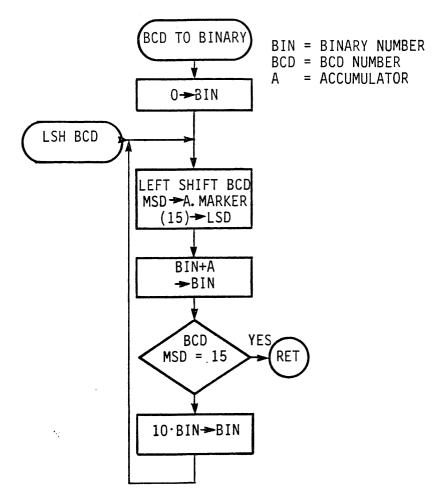

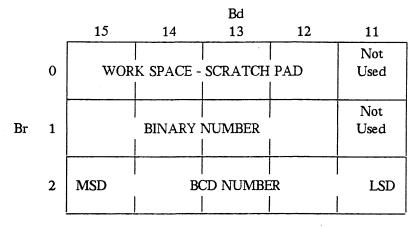

| Figure 5-19. | Two-Digit BCD to Binary Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

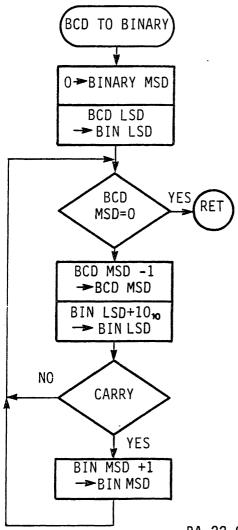

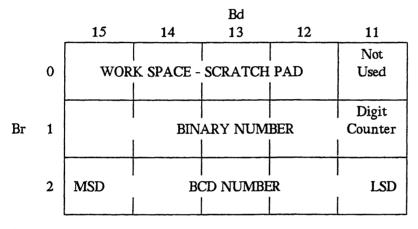

| Figure 5-20. | BCD to Binary Conversion - Multiply by 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

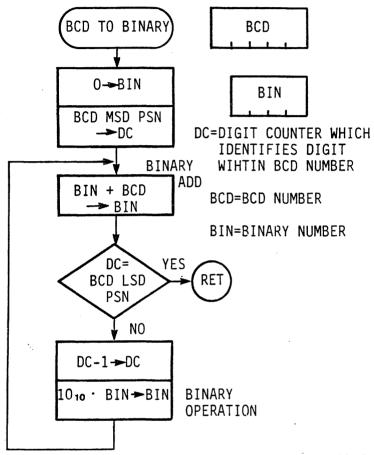

| Figure 5-21. | BCD to Binary Conversion – Multiply by 10 – the Shifting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              | Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

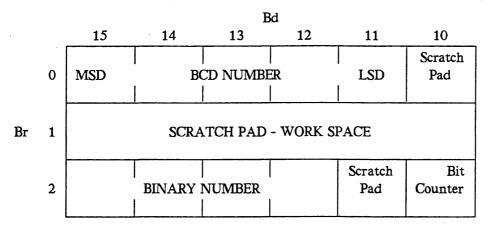

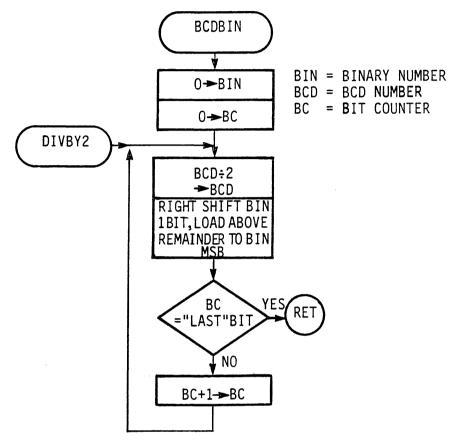

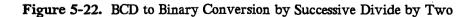

| Figure 5-22. | BCD to Binary Conversion by Successive Divide by Two 5-77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

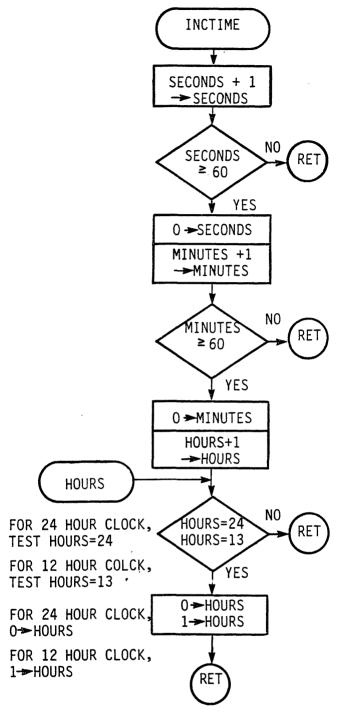

| Figure 5-23. | Basic Block Flow Chart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

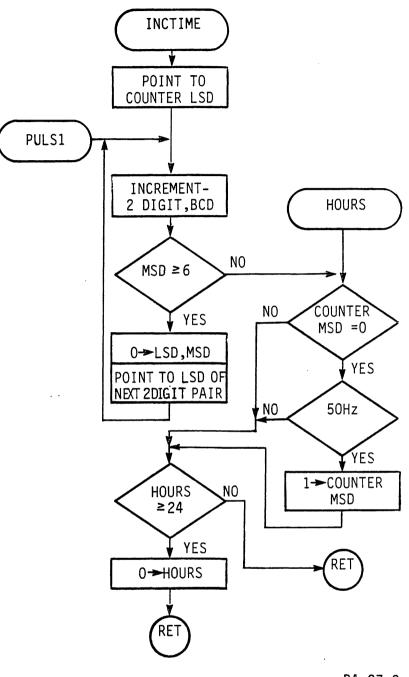

| Figure 5-24. | Clock Based on 50- or 60-Hz Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

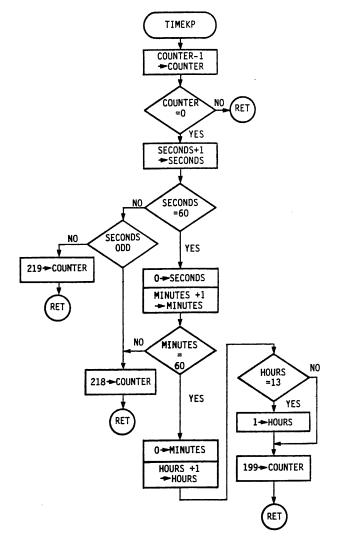

| Figure 5-25. | Flow Chart for Internal Time Base Clock (Oscillator Frequency =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0            | 3.579545 MHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

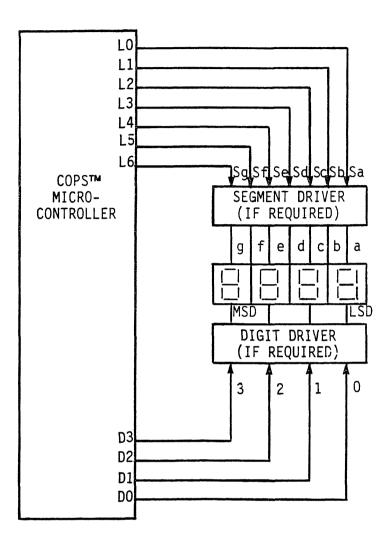

| Figure 5-26. | Interconnect for Sample and Multiplexed Display Code 5-107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

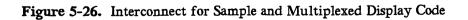

| Figure 5-27. | Multiplexed Display Flow Chart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

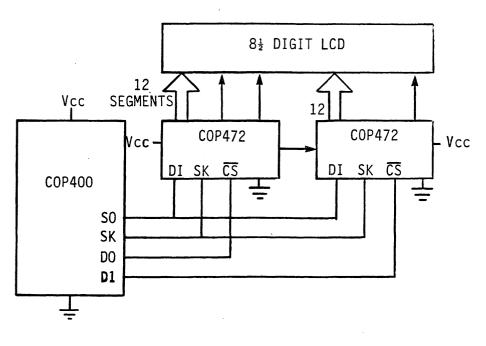

| Figure 5-28. | Dual COP470/472 Systems         5-116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

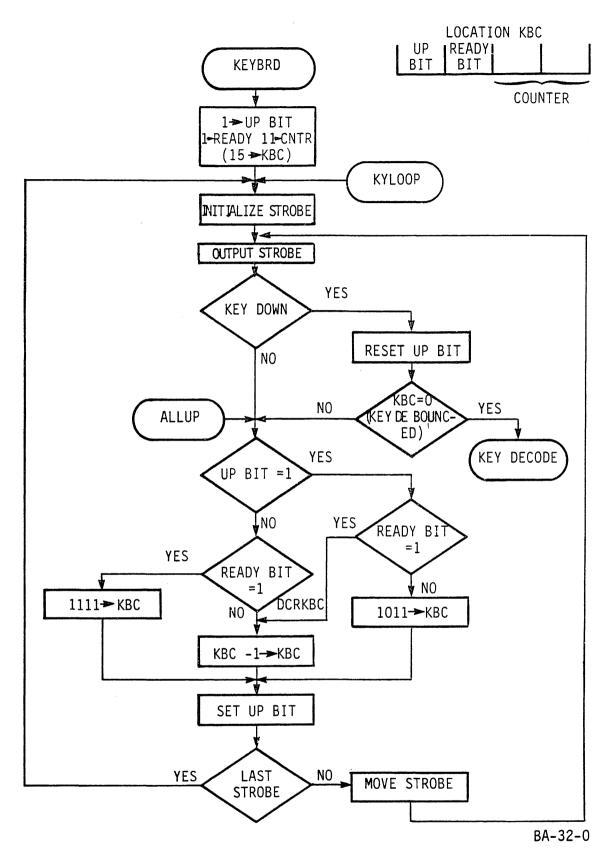

| Figure 5-29. | Keyboard Scan Flow Chart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

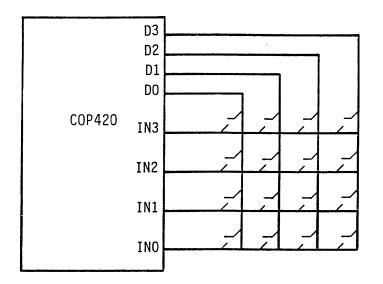

| Figure 5-30. | Interconnect for Key Scan Routine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

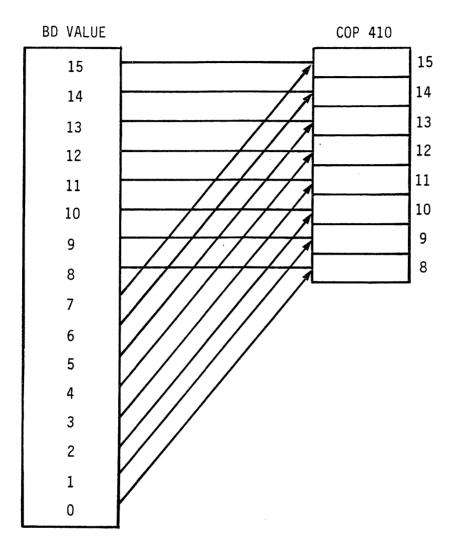

| Figure A-1.  | RAM Mapping         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . <th< td=""></th<> |

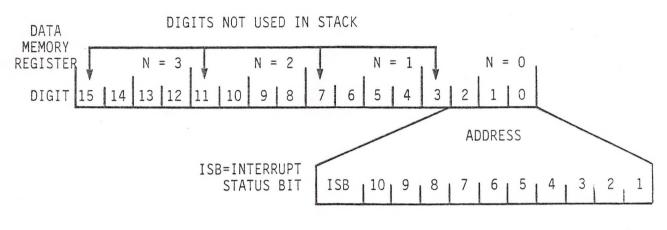

| Figure B-1.  | Stack Structure in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

# TABLES

| TABLE 1-1. | COPS ROMLESS MICROCONTROLLERS - GENERAL SOFTWARE         OVERVIEW     | l-3         |

|------------|-----------------------------------------------------------------------|-------------|

| TABLE 1-2. | COPS MICROCONTROLLERS - GENERAL SOFTWARE         OVERVIEW         1   | l <b>-4</b> |

| TABLE 2-1. | ADDRESS-PAGE-BLOCK-CHAPTER MAPPING                                    | 2-6         |

| TABLE 2-2. | EFFECTS OF EN <sub>3</sub> , EN <sub>0</sub> , ON SIO, SI, SO, AND SK | 14          |

| TABLE 2-3. | INTERRUPT SOURCE SELECTION                                            | 14          |

| TABLE 4-1. | EFFECTS OF BLOCK BOUNDARIES ON JID                                    |             |

|            | DESTINATION                                                           | 1-4         |

| TABLE 5-1. | CONTROL BITS                                                          | 12          |

| TABLE 5-2. | CONTROL CODES                                                         | 13          |

| TABLE 5-3. | MM54XX SERIES DEVICES                                                 | 18          |

# Chapter 1

# INTRODUCTION TO COPS MICROCONTROLLERS

#### 1.1 SCOPE AND PURPOSE OF THIS MANUAL

How is an efficient COPS program written? The answer to this question begins with dividing the broad category of microcomputer into two areas: microcontrollers and microprocessors. This distinction is made because these are really two different types or classes of devices. Microcontrollers generally have a dual-bus architecture rather than the memory-mapped von Neumann architecture common in most microprocessors. For control applications, microcontrollers are generally more memory efficient than microprocessors. The microcontroller instruction set is quite different in nature than the microprocessors are, generally, multi-chip devices. Microcontrollers dominate the microcomputer marketplace in terms of volume. To be sure, the division between microcontroller and microprocessor is sometimes blurred but the distinction is real nonetheless.

COPS devices are microcontrollers. It is the intent of this manual to provide the user/programmer of COPS microcontrollers the requisite information to write an efficient COPS program — to take full advantage of the characteristics of the devices. To achieve that end, this manual is written from the programmer's perspective. The various characteristics of COPS microcontrollers are described in the context of the effect of those characteristics on the programming of the devices. The COPS architecture is discussed; the instruction set is described in detail; general techniques of COPS programming are explained; and standard programs are provided. The standard programs are commonly used as vehicles to illustrate various programming techniques. The user or reader would be well advised to carefully read the explanations associated with routines showing multiple implementations. The intent of providing multiple implementations is not to show how many different ways a routine can be written but rather to show techniques, "tricks", tradeoffs, considerations, etc. Therefore, a great deal of useful information is included in those explanations.

This manual does not attempt to explain the detailed physical or electrical characteristics of COPS microcontrollers. To the extent any such information is provided here, it is to explain some software effect or characteristic. Therefore, the physical details may be simplified to clarify the software explanation.

#### **1.2 THE COPS MICROCONTROLLER FAMILY**

#### 1.2.1 General Description

COPS devices are general purpose, single-chip microcontrollers. These microcontrollers are complete microcomputers containing all system timing, internal logic, ROM, RAM, and I/O necessary to implement dedicated control functions in a wide variety of applications. The COP400 family presently consists of a large number of devices enabling the user to select the device best suited to his application. The software is upward compatible – programs written on one device may be transferred to the next larger device (in terms of memory capacity) with little or no change. The package pin configurations have also been selected so that movement up or down (using memory size as the variable parameter) within the family can be accomplished easily. All COPS microcontrollers, regardless of memory size or number of pins, have the same basic architectural structure. In addition to the large number and wide range of devices, all COPS microcontrollers have a number of I/O options, specified at the same time as the program, which allow the user to tailor, within limits, the I/O characteristics of the microcontroller to the system. Thus, the user can optimize the microcontroller for the system, thereby achieving maximum capability and minimum cost.

This manual deals with the basic functionality of COPS microcontrollers. It does not address electrical differences among the various devices. Thus, this manual does not distinguish between the COP400 and the COP300 series. These two series differ only in electrical characteristics and not in function. This manual further does not distinguish the high-speed devices from the low-power devices or from the CMOS devices except to the extent that some of the devices may have features that affect programming.

### 1.2.2 COPS ROMless Microcontrollers

Several COPS microcontrollers are designed to use external program memory. Basically, these devices have been created by removing the ROM from their single-chip counterparts. These devices are primarily intended to be used in program development and debug, device emulation, and low-volume production. Table 1-1 provides a list of COP400 ROMless devices currently available or in design. The devices are designed so that each COPS microcontroller has at least one ROMless device that can be used for accurate emulation. Since these devices are functionally equivalent to the single-chip microcontrollers, this manual does not generally distinguish the ROMless device from its single-chip counterpart.

#### 1.2.3 COPS Single-Chip Microcontrollers

Table 1-2 provides a list of COPS single-chip microcontrollers currently available or in design. It is readily apparent that the list is quite extensive. Many of the variations are simply different packagings of the same device, *e.g.*, the COP441 is the COP440 in a 28-lead package; the COP442 is the COP440 in a 24-lead package; the COP440 is a 40-pin device. Another important characteristic is the commonality of the pinouts of the single-chip devices: all 40-pin devices have the same pinout; all 24-pin devices have the same pinout; the COP411L and COP411C have the same pinout; the COP422 and COP422L have the same pinout. See Figures 1-1 through 1-4.

| СОР                                                                                                                                                                                                                                                                                                                                                                   | 401L         | 402  | <b>40</b> 2M | 404C | 404L  | 404     | 2404        | 409     |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|--------------|------|-------|---------|-------------|---------|--|--|--|

| External ROM x 8                                                                                                                                                                                                                                                                                                                                                      | Up to<br>512 | Up 1 | to 1024      |      | Up    | to 2048 | o 2048      |         |  |  |  |

| RAM x 4                                                                                                                                                                                                                                                                                                                                                               | 32           |      | 64           | 1    | 28    |         | 160         | 512     |  |  |  |

| Inputs                                                                                                                                                                                                                                                                                                                                                                | 0            |      | 4            |      | 4     |         | 4           | 4       |  |  |  |

| Bidirectional TRI-<br>STATE <sup>®</sup> I/O                                                                                                                                                                                                                                                                                                                          | 8            |      | 8            |      | 8     |         | 8           |         |  |  |  |

| Bidirectional I/O                                                                                                                                                                                                                                                                                                                                                     | 4            |      | 4            |      | 4     |         | 8           | 4       |  |  |  |

| Outputs                                                                                                                                                                                                                                                                                                                                                               | 4            |      | 4            |      | 4     |         | 4           | 4       |  |  |  |

| Serial I/O and<br>External Event<br>Counter                                                                                                                                                                                                                                                                                                                           | Yes          |      | Yes          | Y    | es    |         | Yes         |         |  |  |  |

| Internal Time<br>Base Counter                                                                                                                                                                                                                                                                                                                                         | No           |      | Yes          | Y    | es    |         | Yes         |         |  |  |  |

| Time Base<br>Counter<br>Programmable                                                                                                                                                                                                                                                                                                                                  | No           |      | No           | Yes  | No    |         | Yes         |         |  |  |  |

| Interrupt                                                                                                                                                                                                                                                                                                                                                             | No           | Yes  | No           | Y    | es    | Yes     | - 4 sources | Yes     |  |  |  |

| Stack Levels                                                                                                                                                                                                                                                                                                                                                          | 2            |      | 3            |      | 3     | 4       | 4 per CPU   | 8       |  |  |  |

| Microbus <sup>™</sup> Option                                                                                                                                                                                                                                                                                                                                          | No           | No   | Yes          | Yes  | No    |         | Yes         | No      |  |  |  |

| Instruction Cycle<br>(µs) min - max                                                                                                                                                                                                                                                                                                                                   | 15-40        | 4    | -10          | 4-DC | 15-40 |         | 4-10        | 4-25    |  |  |  |

| Package Size (pins)                                                                                                                                                                                                                                                                                                                                                   | 40           |      | 40           | 48   | 40    |         | 48          | 40      |  |  |  |

| Availability                                                                                                                                                                                                                                                                                                                                                          | Now          | N    | low          | Now  | Now   |         | Now         | Future* |  |  |  |

| * These devices are NOT available as of this writing. The information on these devices is preliminary and subject to change. Advance information has been provided for completeness and as an aid to the user. Announcements will be made by National Semiconductor at the appropriate times regarding the availability and ultimate characteristics of these devices |              |      |              |      |       |         |             |         |  |  |  |

**TABLE 1-1.** COPS ROMLESS MICROCONTROLLERS - GENERAL SOFTWARE OVERVIEW

· . ....

# TABLE 1-2. COPS MICROCONTROLLERS - GENERAL SOFTWARE OVERVIEW

| COP:                                        | T             | 1    |       |      |       | ľ    | ]     |      |      |       | T                  | 1        | 1     |                   |       | T    |       |      |      |             | T                   |        | 1           |                     |     | <b></b> |

|---------------------------------------------|---------------|------|-------|------|-------|------|-------|------|------|-------|--------------------|----------|-------|-------------------|-------|------|-------|------|------|-------------|---------------------|--------|-------------|---------------------|-----|---------|

| COP:                                        | 410L          | 410C | 411L  | 411C | 413I. | 420  | 420L  | 424C | 421  | 421L  | 425C               | 422      | 422L  | 426C              | 444L  | 444C | 445L  | 445C | 440  | 441         | 442                 | 2440   | 2441        | 2442                | 484 | 485     |

| ROM X 8                                     |               |      | 512   |      |       |      |       |      | 1024 |       |                    |          |       | 2048              |       |      |       |      |      |             |                     | 4096   |             |                     |     |         |

| RAM × 4                                     |               |      | 32    |      |       |      |       |      |      | 64    |                    |          |       |                   |       | 1    | 28    |      |      |             | 1                   | 60     |             |                     | 2!  | 56      |

| INPUTS                                      |               |      | 0     |      |       |      | 4     |      |      |       | . <sup>*</sup> . ( | )        |       |                   |       | 4    |       | 0    |      | 4           | 0                   |        | 4           | 0                   | 4   | 0       |

| BIDIRECTIONAL<br>TRI-STATE I/O              |               |      | 8     |      |       |      |       |      |      | 8     |                    |          |       |                   |       |      | 8     |      | 16   |             | 8                   | 16     |             | 8                   |     | 8       |

| BIDIRECTIONAL<br>I/O                        |               | 1    | :     | 3    | 4     |      | 4     |      |      | 4     |                    |          | 2     |                   |       |      | 4     |      | 8    |             | 4                   | 8      |             | 4                   |     | 4       |

| OUTPUTS                                     |               | 4    |       | 2    |       |      | 4     |      |      | 4     |                    |          | 2     |                   |       |      | 4     |      |      | <b></b>     |                     | 4      |             |                     |     | 4       |

| SERIAL I/O AND<br>External event<br>Counter |               |      | YES   |      |       |      |       |      |      | YES   |                    | <b>.</b> | •     |                   |       |      | YES   |      |      |             |                     | YES    |             |                     | Y   | (ES     |

| INTERNAL TIME<br>BASE COUNTER               |               |      | NO    |      |       |      | •     |      |      | YES   |                    |          |       |                   |       |      | YES   |      |      |             |                     | YES    |             |                     | Y   | /ES     |

| TIME BASE<br>COUNTER<br>PROGRAMMABLE        |               |      | NO    |      |       | N    | 0     | YES  | Ņ    | 0     | YES                | NO       | Y     | ES                | NO    | YES  | NO    | YES  |      |             |                     | YE     | S           |                     |     |         |

| INTERRUPT                                   |               |      | NO    |      |       |      | YES   | ·    |      |       | NC                 | )        |       |                   | Y     | ES   | ٢     | 10   | 4 SO | ES<br>URCES | YES<br>2<br>Sources | 1 4 50 | ES<br>URCES | YES<br>2<br>Sources | YES | NO      |

| STACK LEVELS                                |               |      | 2     |      | •     |      |       |      |      | 3     |                    |          |       |                   |       |      | 3     |      |      | 4           |                     | 4      | PER C       | PU                  |     | 4       |

| MICROBUS<br>OPTION                          |               |      | NO    |      |       | YES  | NO    | YES  |      |       | N                  | )        |       |                   | NO    | YES  | , I   | 10   | Y    | ES          | NO                  | Y      | ES          | NO                  | 1   | NO      |

| INSTRUCTION<br>CYCLE (MS)<br>MIN-MAX        | <b>16-4</b> 0 | 4-DC | 16-40 | 4-DC | 16-40 | 4-10 | 16-40 | 4-DC | 4-10 | 16-40 | 4-DC               | 4-10     | 16-40 | 4#SEC<br>TO<br>DC | 16-40 | 4-DC | 16-40 | 4-DC |      |             |                     | 4-10   |             |                     | 4   | -25     |

| PACKAGE SRE<br>(PINS)                       | 2             | 4    |       | 20   |       |      | 28    |      |      | 24    |                    |          | 20    |                   | 2     | 28   |       | 24   | 40   | 28          | 24                  | 40     | 28          | 24                  | 28  | 24      |

| AVAILABILITY                                |               |      | NOW   |      |       |      | NOW   |      |      | NOW   |                    |          | NOW   |                   | N     | OW   | N     | OW   |      |             | N                   | OW     |             |                     | FUT | URE*    |

\* THESE DEVICES ARE NOT AVAILABLE AS OF THIS WRITING. THE INFORMATION ON THESE DEVICES IS PRELIMINARY AND SUBJECT TO CHANGE. ADVANCE INFORMATION HAS BEEN PROVIDED FOR COMPLETENESS AND AS AN AID TO THE USER. ANNOUNCEMENTS WILL BE MADE BY NATIONAL SEMICONDUCTOR AT THE APPROPRIATE TIME REGARDING THE AVAILABILITY AND ULTIMATE CHARACTERISTICS OF THESE DEVICES.

BA-37-C

Figure 1-1. Pinouts for 20-Pin COPS Microcontrollers

| GND-   | 1  | COP410L | 24 | -D0          |

|--------|----|---------|----|--------------|

| СКО    | 2  | COP410C | 23 | -D1          |

| CKI-   | 3  | COP421  | 22 | -D2          |

| RESET- | 4  | COP421L | 21 | D3           |

| L7     | 5  | COP425C | 20 | -G3          |

| L6-    | 6  | COP445L | 19 | G2           |

| L5     | 7  | COP445C | 18 | -G1          |

| L4-    | 8  | COP485  | 17 | -G0          |

| Vcc-   | 9  | COP442  | 16 | -SK          |

| L3-    | 10 | COP2442 | 15 | - <b>S</b> 0 |

| L2-    | 11 |         | 14 | -SI          |

| L1-    | 12 |         | 13 | -L0          |

|        |    |         |    |              |

Figure 1-2. Pinout for 24-Pin COPS Microcontrollers

| GND-1   |         | 28 – D0  |

|---------|---------|----------|

| СКО-2   | •       | 27 – D1  |

| CKI-3   |         | 26 – D2  |

| RESET-4 | COP420  | 25 – D3  |

| L7-5    | COP420L | 24 – G3  |

| L6-6    | COP424C | 23 - G2  |

| L5-7    | COP444L | 22 – G1  |

| L4-8    | COP444C | 21 - G0  |

| IN1-9   | COP484  | 20 – IN3 |

| IN2-10  | COP441  | 19 – INO |

| Vcc-11  | COP2441 | 18 – SK  |

| L3-12   |         | 17-S0    |

| L2-13   |         | 16 – LI  |

| L1-14   |         | 15 – L0  |

| L       |         |          |

Figure 1-3. Pinout for 28-Pin COPS Microcontrollers

| L1-  | 1  |         | 40 | -Vcc  |

|------|----|---------|----|-------|

| L0-  | 2  |         | 39 | -L2   |

| SI-  | 3  |         | 38 | -L3   |

| S0-  | 4  |         | 37 | -IN2  |

| SK—  | 5  |         | 36 | -IN1  |

| IN0- | 6  |         | 35 | -L4   |

| IN3- | 7  |         | 34 | -L5   |

| G0   | 8  |         | 33 | -L6   |

| G1   | 9  |         | 32 | -L7   |

| G2-  | 10 | COP440  | 31 | -RO   |

| G3-  | 11 | COP2440 | 30 | -R1   |

| H0-  | 12 |         | 29 | -R2   |

| H1—  | 13 |         | 28 | -R3   |

| H2—  | 14 |         | 27 | -R4   |

| H3-  | 15 |         | 26 | -R5   |

| D3-  | 16 |         | 25 | -R6   |

| D2-  | 17 |         | 24 |       |

| D1-  | 18 |         | 23 | RESET |

| D0   | 19 |         | 22 | -СКІ  |

| GND- | 20 |         | 21 | -СК0  |

|      |    |         |    | 1     |

Figure 1-4. Pinout for 40-Pin COPS Single-Chip Microcontrollers

### 1.2.4 Conclusion

COPS microcontrollers comprise a broad, general purpose, powerful, and flexible family of devices. The hardware and software compatibility of the devices allow the user to move easily within the family as the need arises or the application dictates. Many ROMless devices are available to aid in emulation and development. The applications of COPS devices are unlimited. COPS microcontrollers have been used in automotive (trip computer, seat position controller, electronic instrument cluster, ignition systems, diagnostic systems), appliance (ovens, microwave ovens, vacuum cleaners, sewing machines, washers, driers, food processors), home electronic (electronically tuned radios, cassette recorders, video cassette recorders, stereo systems), security system, timekeeping, energy management, industrial/commercial (utility meters, keyboard encoders, cash registers, dictation equipment, coin changers, vending machines, jukeboxes), telephone (repertory dialers, simple phone dialers, call timers), exercise equipment (exercise bicycle, jogging machine), miscellaneous home (garage door openers, lawn sprinklers, Christmas ornaments, cable television), toy, game, and many other applications.

# Chapter 2

# ARCHITECTURE OF COPS MICROCONTROLLERS

#### 2.1 INTRODUCTION

This section deals with the architecture of COPS microcontrollers. Figure 2-1 is the generic block diagram for COPS microcontrollers. The diagram is accurate as is for the COP420/421/422, COP420L/421L/422L, COP424C/425C/426C, COP444L/445L, COP444C/445C, and COP484/485 devices. The addition or deletion of certain elements creates the other microcontrollers in the COPS family. Figure 2-2, the block diagram of the COP410L/411L/413L and COP410C/411C, Figure 2-3, the block diagram of the COP440/441/442, and Figure 2-4, the block diagram of the COP440/2441/2442, illustrate this fact. It is clear, even from a cursory examination, that all COPS microcontrollers possess the fundamental architecture that is indicated in Figure 2-1. Therefore, Figure 2-1 is the focal point for the discussion of the COPS architecture. The additions or deletions that lead to the other block diagrams are discussed where appropriate.

#### 2.2 COPS MEMORY STRUCTURE

#### 2.2.1 Program Memory – ROM

The program memory in COPS microcontrollers is a read-only memory (ROM) organized as a number of eight-bit words. COPS microcontrollers with ROM capacities of 512, 1024, and 2048 words are presently available. Devices with ROM capacity of 3072 and 4096 words are currently in design. The ROM words are addressed sequentially by a binary program counter (in ROMless devices, the program counter is brought out to pins to address external memory). The program counter starts at zero and, if there are no jumps or subroutines or table lookups, will increment to the maximum value possible for the device and rolls over to zero and begins again.

Internally, COPS microcontrollers have a semi-transparent page, block, and chapter structure to the ROM. A page is composed of 64 contiguous ROM words. The lower six bits of the program counter are zeroes at the first address of a page and ones at the last address of a page. A block, which is significant only in the table lookup and indirect jump operations, is composed of four contiguous pages (256 contiguous ROM words). The lower eight bits of the program counter are zeroes at the first address of a block and ones at the last address of a block. The first address of a block is also the first address of a page and the last address of a block is also the last address of a page. The chapter division is relevant only in COPS devices with more than 2048 ROM words or ROMless devices capable of addressing more than 2048 ROM words. The lower 11 bits of the program are zeroes at the first address of a chapter and ones at the last address of a chapter. The first address of a chapter is also the first address of a block and the last address of a chapter is also the last address of a block. Table 2-1 lists the hexadecimal address and the corresponding page/chapter/block divisions.

\*\*THESE PINS NOT AVAILABLE ON 20-LEAD DEVICES.

+ONLY CMOS COPS EXCEPT 411C.

++NOT AVAILABLE ON 1K DEVICES.

BA-01-0

Figure 2-1. Basic Block Diagram for COPS Microcontrollers

BA-02-0

### Figure 2-2. COP410L/411L/413L and COP410C/411C Block Diagram

\*THESE PINS NOT AVAILABLE ON 28-OR 24- LEAD DEVICES.

\*\*THESE PINS NOT AVAILABLE ON 24-LEAD DEVICES.

BA-03-0

# TABLE 2-1. ADDRESS-PAGE-BLOCK-CHAPTER MAPPING

| HEX ADDRESS | PAGE | BLOCK | CHAPTER                               |

|-------------|------|-------|---------------------------------------|

| 000-03F     | 0    |       |                                       |

| 040-07F     | 1    | 0     |                                       |

| 080-0BF     | 2    |       |                                       |

| 0C0-0FF     | 3    |       |                                       |

| 100-13F     | 4    |       |                                       |

| 140-17F     | 5    | 1     |                                       |

| 180-1BF     | 6    |       |                                       |

| 1C0-1FF     | 7    |       |                                       |

| 200-23F     | 8    |       |                                       |

| 240-27F     | 9    | 2     |                                       |

| 280-2BF     | 10   |       |                                       |

| 2C0-2FF     | 11   |       |                                       |

| 300-33F     | 12   |       |                                       |

| 340-37F     | 13   | 3     | 0                                     |

| 380-3BF     | 14   |       |                                       |

| 3C0-3FF     | 15   |       |                                       |

| 400-43F     | 16   |       |                                       |

| :           | :    | 4     |                                       |

| 4C0-4FF     | 19   |       |                                       |

| 500-53F     | 20   |       |                                       |

| :           | :    | 5     |                                       |

| 5C0-5FF     | 23   |       |                                       |

| 600-63F     | 24   |       |                                       |

| :           | :    | 6     |                                       |

| 6C0-6FF     | 27   |       |                                       |

| 700-73F     | 28   |       |                                       |

| :           | :    | 7     |                                       |

| 7C0-7FF     | 31   |       |                                       |

|             | ł    | I I   | · · · · · · · · · · · · · · · · · · · |

| HEX ADDRESS  | PAGE    | BLOCK | CHAPTER |

|--------------|---------|-------|---------|

| 800-83F      | 32      |       |         |

| :<br>8C0-8FF | :<br>35 | 8     |         |

| 900-93F      | 36      | _     |         |

| :<br>9C0-9FF | :<br>39 | 9     |         |

| A00-ACF      | 40      |       |         |

| :<br>AC0-AFF | :<br>43 | 10    |         |

| B00-B3F      | 44      |       |         |

| :<br>BCO-BFF | :<br>47 | 11    |         |

| C00-C3F      | 48      |       |         |

| :<br>CC0-CFF | :<br>51 | 12    | 1       |

| D00-D3F      | 52      |       |         |

| :<br>DC0-DFF | :<br>55 | 13    |         |

| E00-E3F      | 56      |       |         |

| :<br>ECO-EFF | :<br>59 | 14    |         |

| F00-F3F      | 60      |       |         |

| :<br>FC0-FFF | :<br>63 | 15    |         |

| 1000-103F    | 64      |       |         |

| •            | :       |       |         |

TABLE 2-1. (Cont)

This internal structure is semi-transparent. Only some jumps, some subroutine calls, and table lookups are affected by this structure. As indicated earlier, the block divisions come into play only in the table lookups and indirect jumps. The page and chapter divisions affect some direct jumps and subroutine calls. Chapter 4 explains the effects of these divisions on the pertinent instructions. Complete operational programs can be written without consideration of this internal structure. Such a program, however, will use more code, and therefore require larger ROM capacity, than a program written with this structure in mind. Chapter 4 will address this in greater detail. This page/block/chapter structure has no effect on the program counter. The binary program counter will freely increment through page, block, or chapter boundaries.

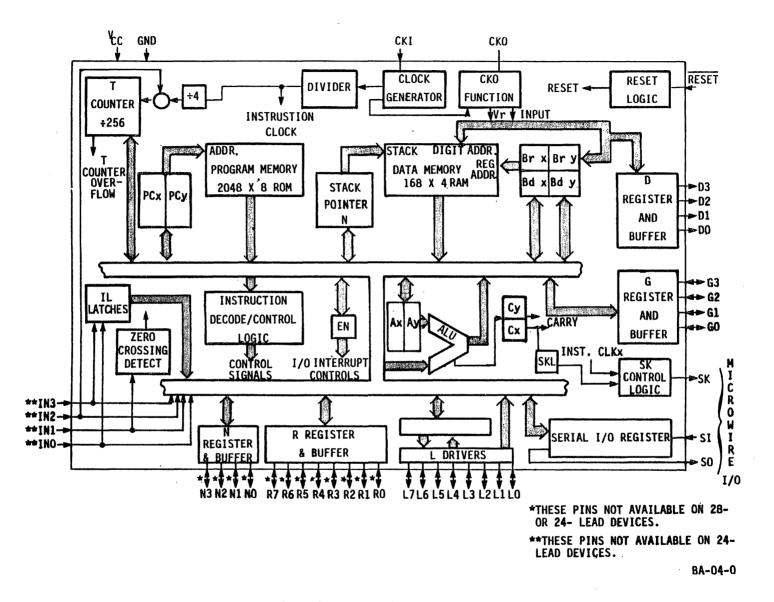

#### 2.2.2 Data Memory – RAM

The data memory (RAM) in COPS microcontrollers is organized as a matrix. Each row in the matrix is called a register; each column in the matrix is called a digit. A digit is 4 bits wide. As shall be seen, this particular structure contributes to the general efficiency of COPS microcontroller. All RAM addressing is based on this register-digit (or row-column) organization. The RAM address register identifies a specific digit in the RAM matrix. COPS devices with RAM sizes of 32 digits (4 registers by 8 digits, 128 bits), 64 digits (4 registers by 16 digits, 256 bits), 128 digits (8 registers by 16 digits), and 160 digits (10 registers by 16 digits) are presently available. A device with RAM sizes 256 digits (16 registers by 16 digits) is in design. A ROMless device with 512 digits (32 registers by 16 digits) of RAM is also in design.

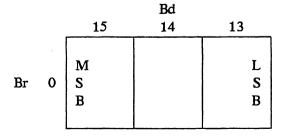

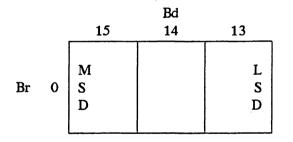

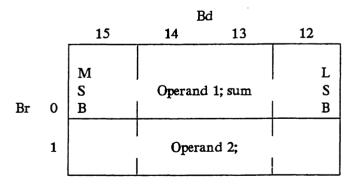

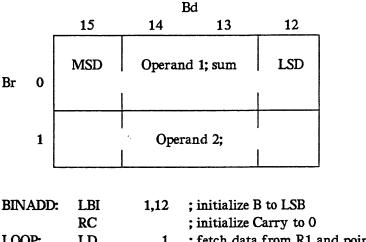

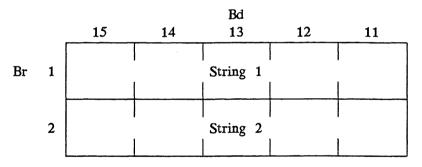

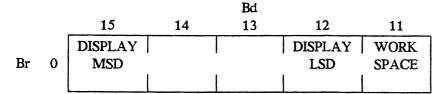

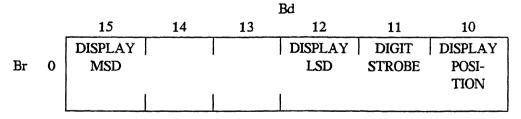

The RAM in COPS microcontrollers is not in the program memory space. The RAM is not addressed by the program counter but has its own address register, the B register. The B register can be loaded directly or through the accumulator. Since the RAM has its own address register, most COPS instructions which access RAM do not contain an address field. This tends to promote ROM code efficiency. The B register is divided into two distinct parts: Br - the row or register address and Bd - the column or digit address. Bd is 4 bits wide in allCOPS microcontrollers. Br is between 2 and 5 bits wide depending on the particular device.Bd, in addition to being the digit address, is the source for the D output register. On softwarecommand, the contents of Bd can be transferred to the D port where the information islatched.

The data memory digit addressed by the B register is normally accessed through the accumulator. The contents of the RAM digit may be directed, under software command, to one of several output ports as well as used in the normal program flow. Two instructions, LDD and XAD, carry a RAM address with them. These instructions operate (load or exchange) on the specified RAM digit without modifying the B register.

#### 2.2.3 Subroutine Stack

COPS microcontrollers have a subroutine stack of two, three, or four (eight on the COP409) save registers. On all COPS microcontrollers with two or three save registers in the subroutine stack, a physical transfer of register contents within the stack occurs on all operations affecting the stack, primarily calls and returns. On these devices, the stack is physically and logically separate from data RAM. The user does not have access to the stack and, therefore, may not read or write the stack in these devices.

On COPS devices with four or more stack levels, the stack is located in data RAM. Four stack levels use up one data register. The user has access to the stack since the data RAM contains