# PM Technical Reference Manual

Please attach this label to the spine of the binder. See the illustration below for the correct location.

# PM Technical Reference Manual

TeleVideo Part Number 127611-00 Rev. A

February 1985

)

)

#### Personal Mini Technical Reference

#### Copyright

Copyright ©1985 by TeleVideo Systems, Inc. All rights reserved. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, without the prior written permission of TeleVideo Systems, Inc., 550 East Brokaw Road, San Jose, CA 95112.

#### Disclaimer

TeleVideo Systems, Inc. reserves the right to make improvements to products without incurring any obligations to incorporate such improvements in products previously sold. Specifications and information contained in this manual are subject to change without notice.

Material describing applications of components supplied by independent vendors such as Intel, Synertek, and Western Digital have been based in large part upon handbooks, technical manuals, and similar information distributed by such vendors. For a complete description of those parts and the ways in which they may be used, reference should be made to vendors' texts, which will be more complete.

#### Personal Mini Technical Reference

TeleVideo is a registered trademark of TeleVideo Systems, Inc.

PM, PM/16, PM/16T, and PM/4T are trademarks of TeleVideo Systems, Inc.

Z80A is a registered trademark of ZILOG Corporation.

Printed February 1985.

TeleVideo Part Number: 127611-00 Rev. A

TeleVideo Systems, Inc., 550 East Brokaw Road, San Jose, CA 95112.

#### PREFACE

The Personal Mini Technical Reference Manual is intended for use by the programmer, engineer, dealer, and end user. The manual provides an overview of the hardware and a more in-depth view of the hardware programming. The systems covered include the PM/16, PM/16T, and PM/4T. The latter two systems feature an integral backup tape drive for backing up the hard disk, hence the 'T' suffix in their names.

The manual has five chapters and three appendices which are described here. Chapter 1, Unit Overview, describes the features of the Personal Mini and provides the physical, environmental, power, memory, and storage specifications. The workstation cable requirements and a general description of each major assembly are also described. At the end of the chapter is a list of references that provide additional information about the components discussed in this manual.

Chapter 2, Hardware Functions, details the operations of the following components: the CPU (16-bit), Z80A (8-bit processor), main memory, hard disk controller, and the tape backup drive.

**Chapter 3, Hardware Programming,** contains the information a programmer needs to interface with the system hardware, such as I/O addresses and command codes.

#### **Chapter 4, Interface,** details the pin-outs and signals for the internal and external connectors.

Appendix A, Jumper Configurations, describes the jumper configurations on the main CPU board and tape drive interface board.

**Appendix B, Self Diagnostics,** describes the diagnostics that are performed by the Personal Mini upon initialization.

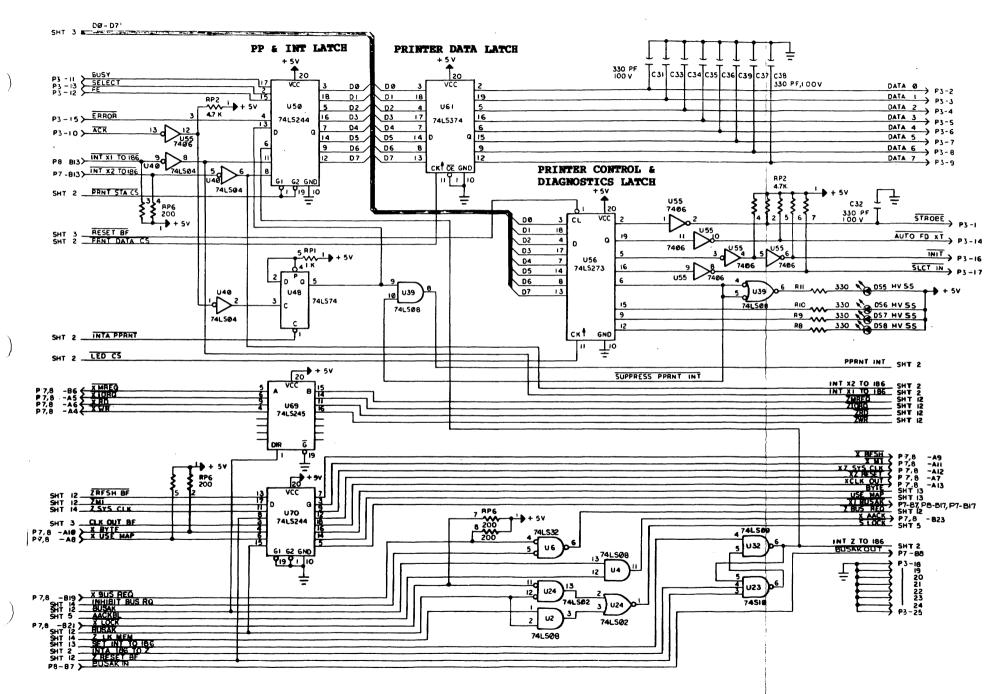

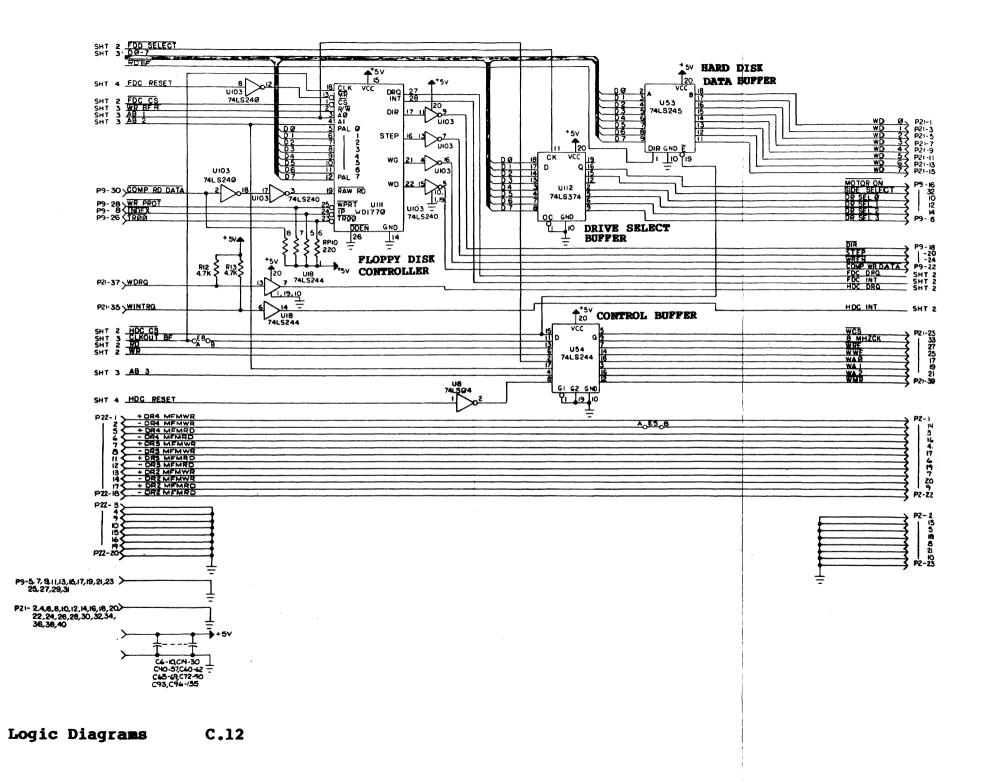

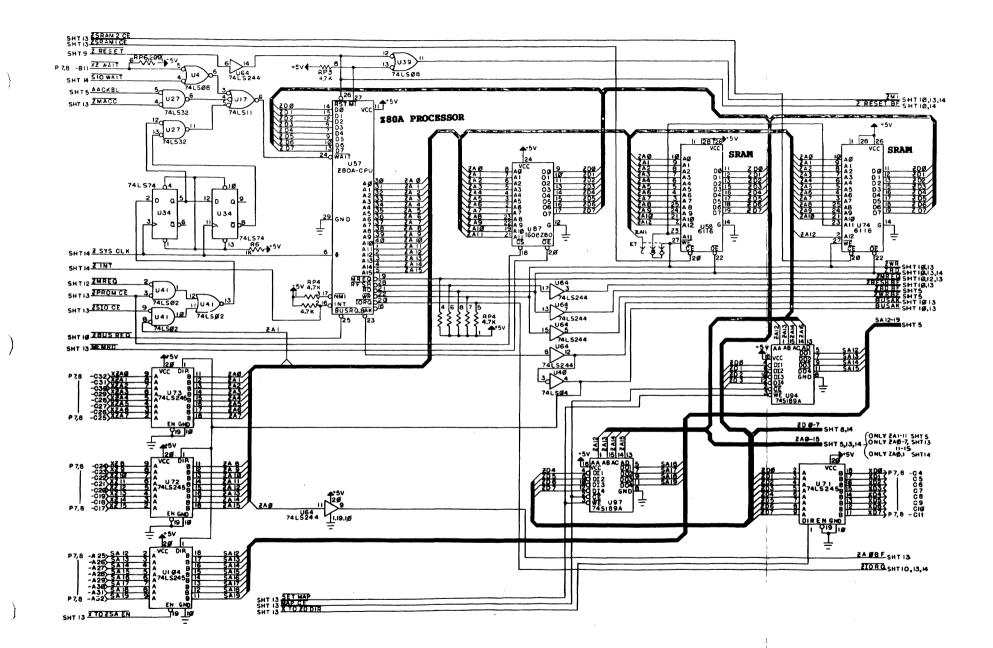

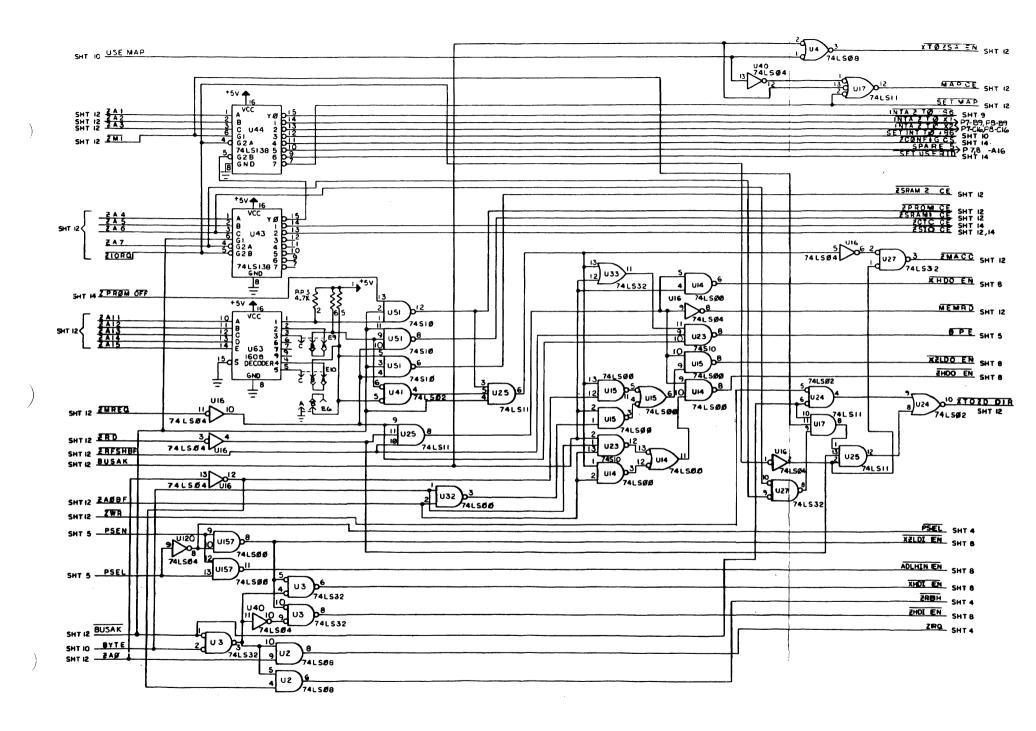

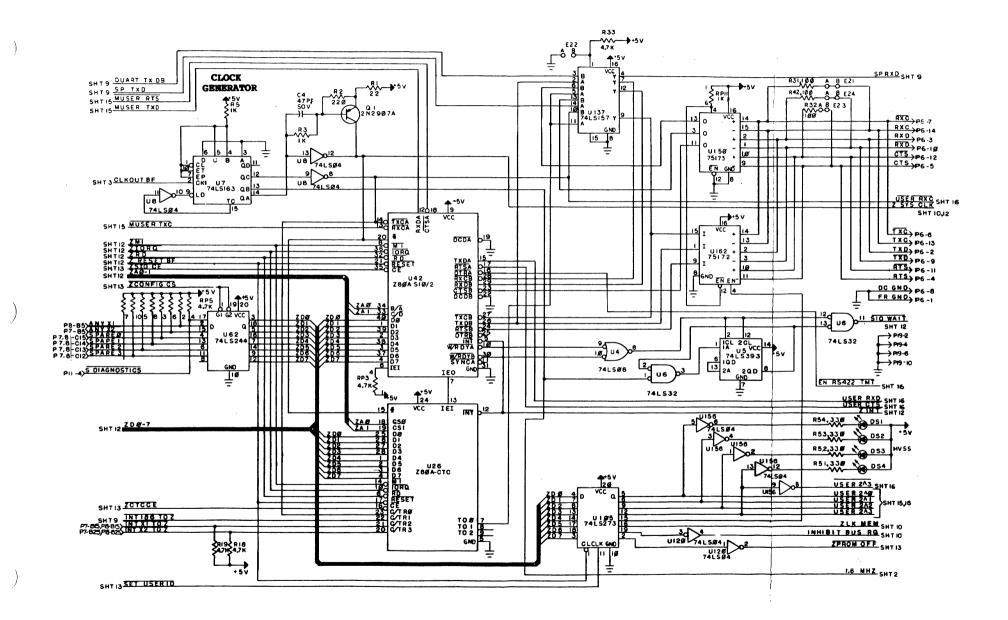

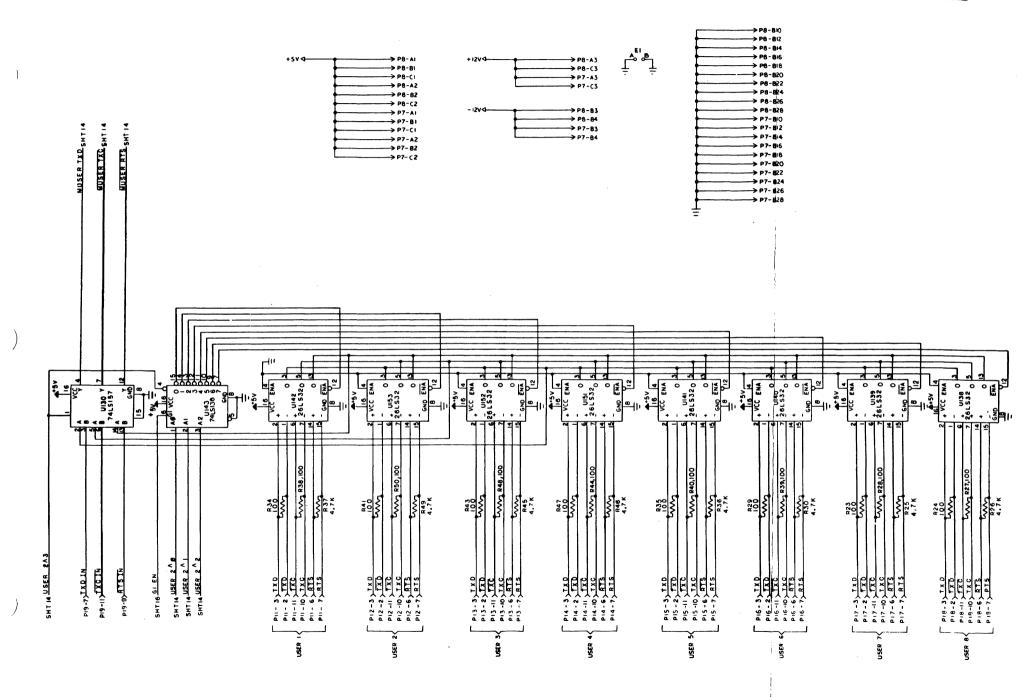

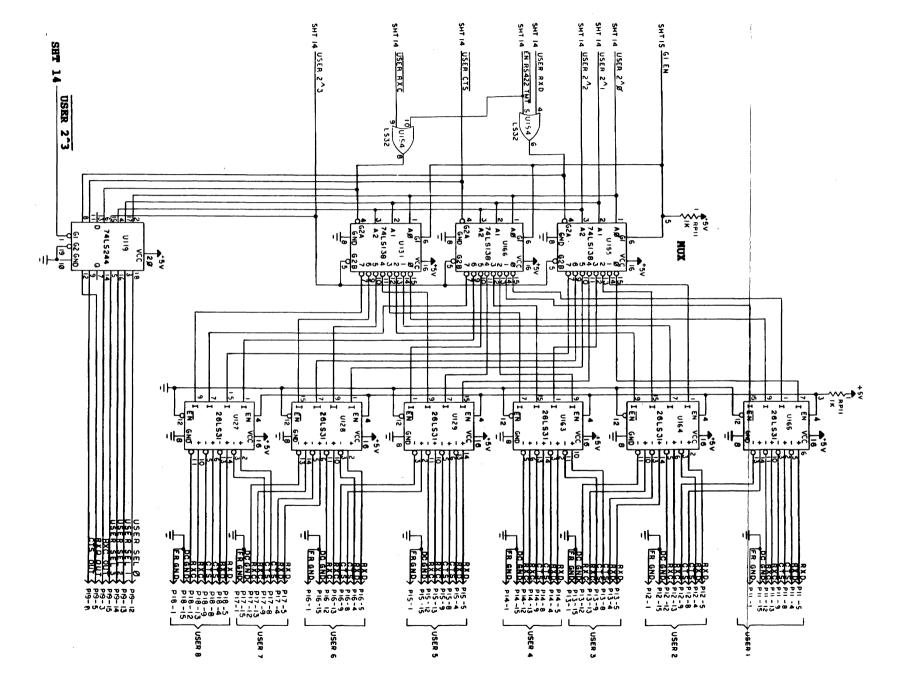

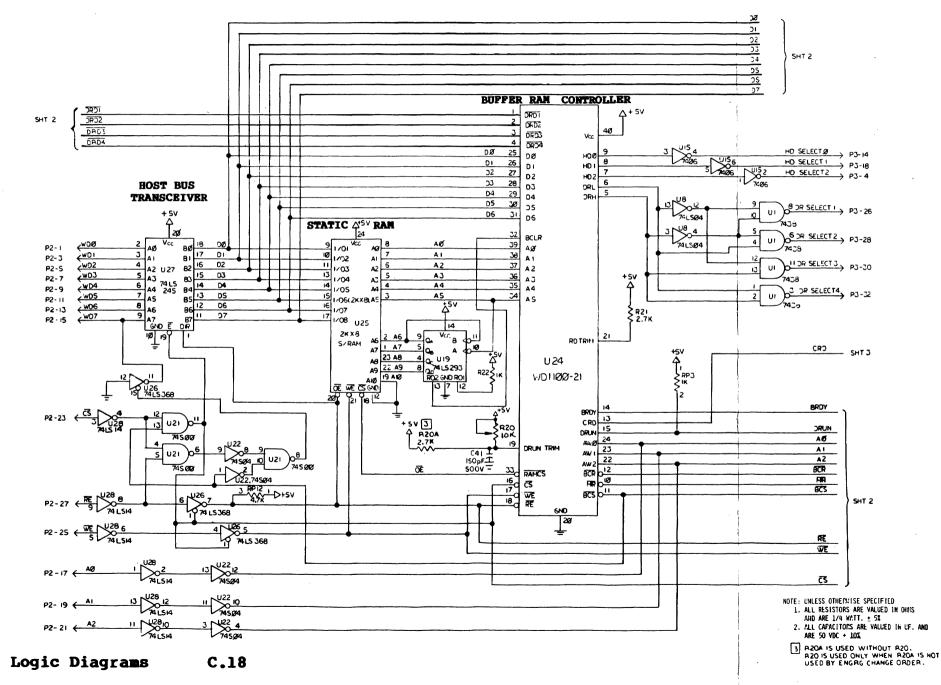

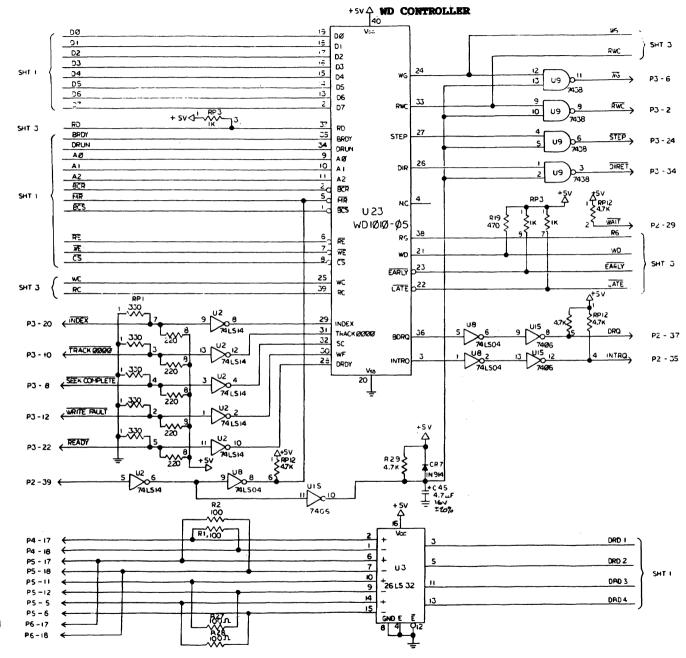

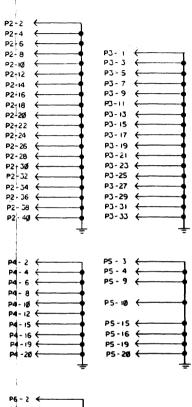

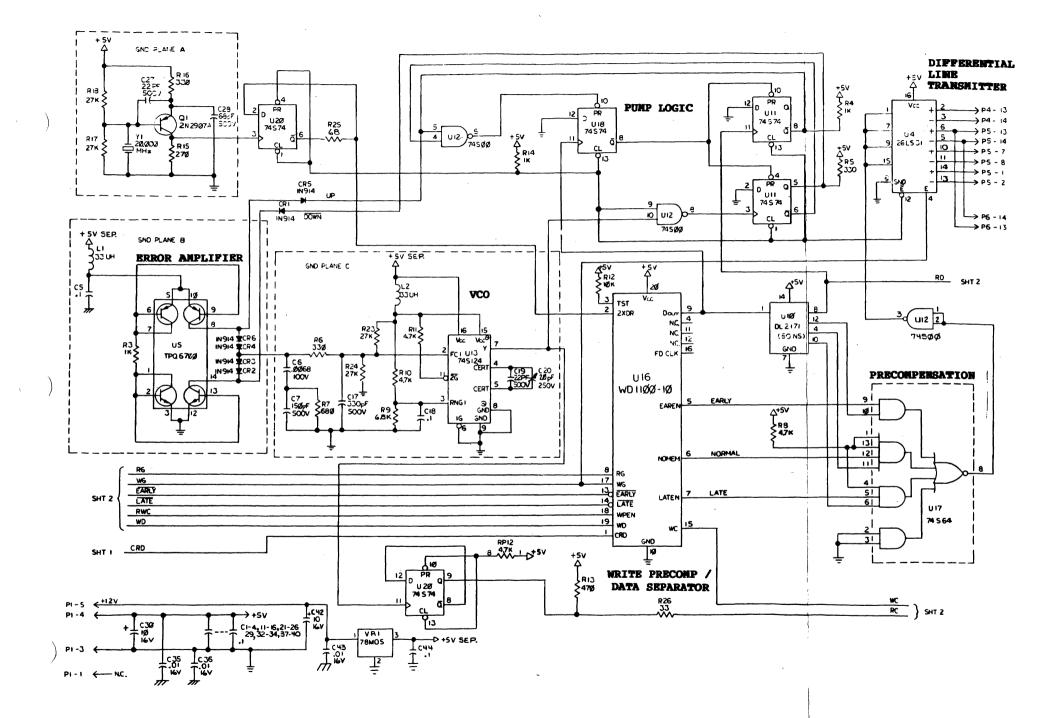

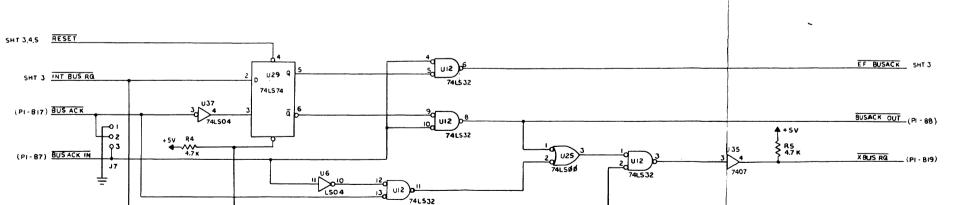

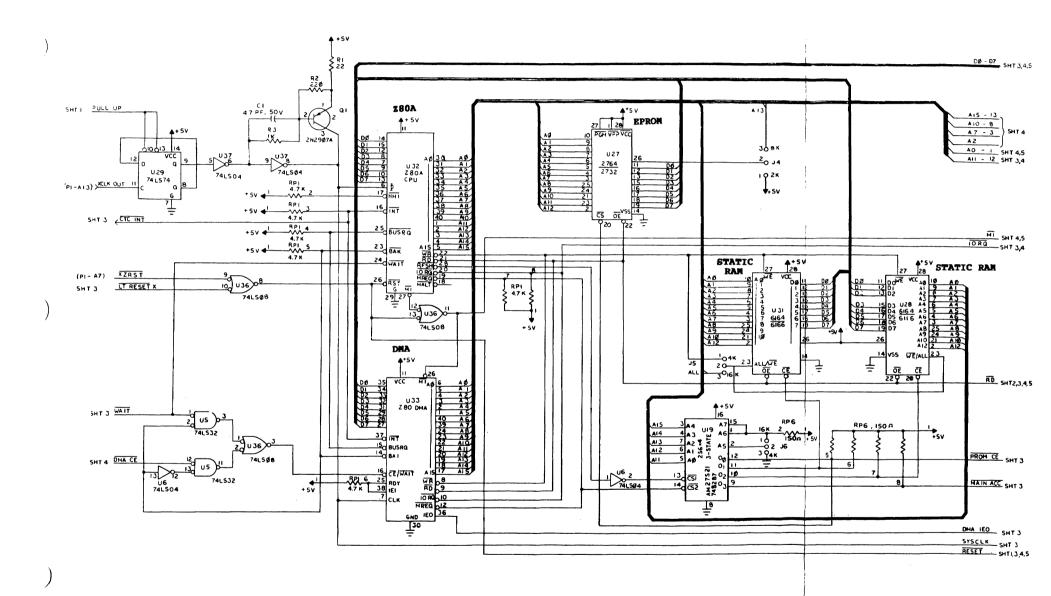

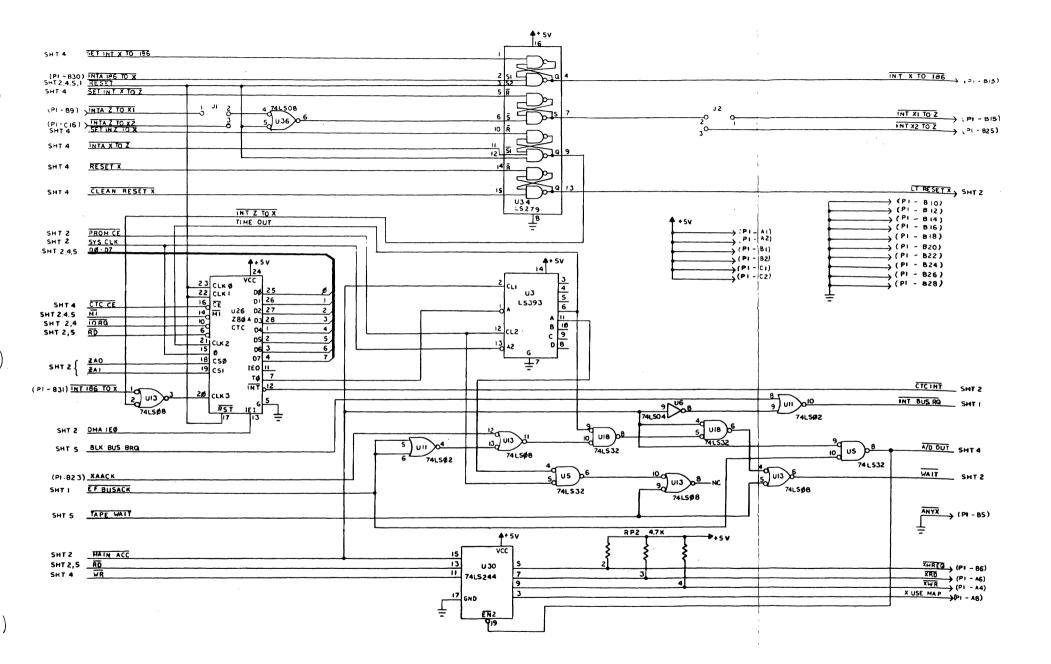

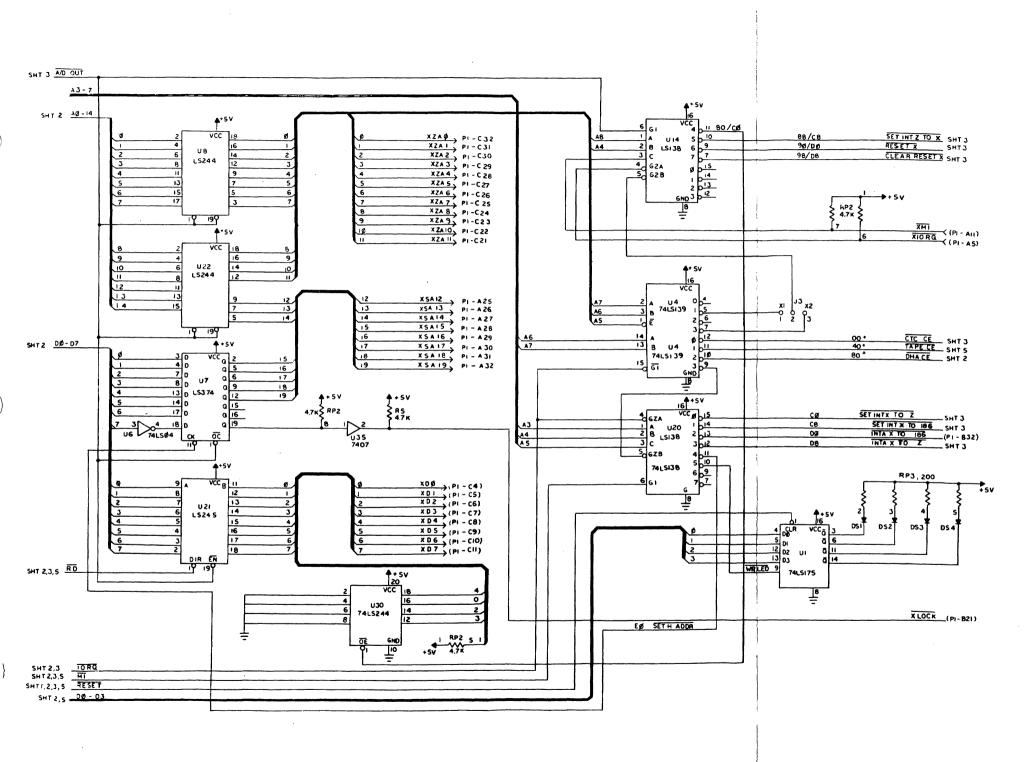

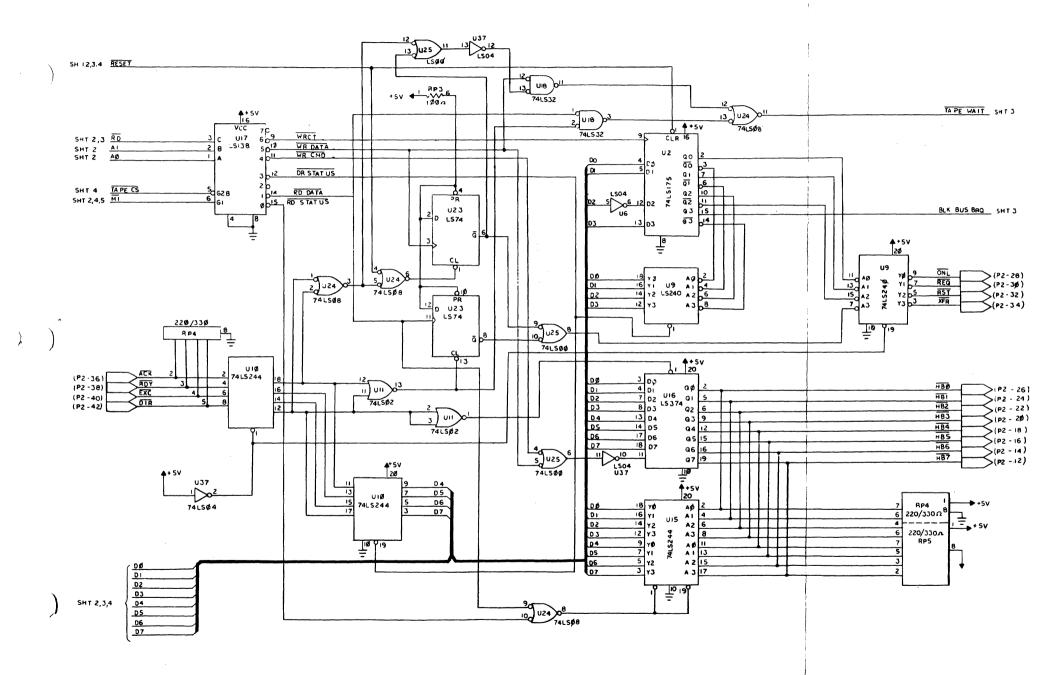

**Appendix C, Logic Diagrams,** contains the logic diagrams of the main CPU board, Winchester disk controller board, and tape drive interface board.

## TABLE OF CONTENTS

#### **1 UNIT OVERVIEW**

)

)

)

| Physical Specifications      | 1.3  |

|------------------------------|------|

| Environmental Specifications | 1.5  |

| Power Requirements           | 1.5  |

| Memory and Storage           | 1.6  |

| Workstation Cables           | 1.8  |

| Major Assemblies             | 1.8  |

| Technical References         | 1.10 |

#### **2 HARDWARE FUNCTIONS**

| 80186 CPU Functions<br>DUART | 2.1<br>2.6 |

|------------------------------|------------|

| Parallel Printer Port        | 2.6        |

| Floppy Disk Controller       | 2.9        |

| Hard Disk Interface          | 2.11       |

| System Interrupts            | 2.11       |

| Main Memory                  | 2.13       |

| Memory Mux                   | 2.13       |

| Memory Controller            | 2.13       |

| Memory Banks                 | 2.15       |

| Winchester Disk Controller   | 2.16       |

| 8-Bit Networking Functions   | 2.18       |

| Local Memory                 | 2.20       |

| Memory Mapping               | 2.20       |

| Serial I/O and User          |            |

| Stations                     | 2.20       |

| Counter-Timer Circuit        | 2.22       |

| Expansion Slots              | 2.23       |

| Tape Back-Up                 | 2.23       |

| Tape Operation               | 2.23       |

## 3 HARDWARE PROGRAMMING

| 80186 Microprocessor            | 3.1  |

|---------------------------------|------|

| 80186 Interrupts                | 3.1  |

| 80186 Read-Only Memory          | 3.3  |

| 80186 I/O Port Selection        | 3.4  |

| Z80A Microprocessor             | 3.8  |

| Z80A Interrupts                 | 3.8  |

| Z80A Read-Only Memory           | 3.9  |

| Z80A I/O Ports                  | 3.10 |

| <b>Z80A</b> Processor Section   |      |

| Reset                           | 3.12 |

| Main Memory                     | 3.13 |

| Dual Port Ram Controller        | 3.13 |

| Memory Organization             | 3.16 |

| Memory Locking                  | 3.17 |

| Z80A CPU Main Memory            |      |

| Mapping                         | 3.17 |

| Expansion Card Slots            | 3.19 |

| System Facilities for Expansion |      |

| Cards                           | 3.21 |

| Parallel Port                   | 3.21 |

| Serial and Console Ports        | 3.23 |

| Mode Register 1 - MR1A          |      |

| & MRÍB                          | 3.24 |

| Clock Select Registers          |      |

| CSRA & CSRB                     | 3.27 |

| Interrupt Status Register -     |      |

| ISR                             | 3.29 |

| Command Registers - CRA         |      |

| & CRB                           | 3.30 |

| Floppy Disk Controller          | 3.32 |

| Status Register                 | 3.34 |

| Command Register                | 3.35 |

| Track Register                  | 3.38 |

| Sector Register                 | 3.38 |

| Data Register                   | 3.38 |

| Winchester Disk Controller      |      |

| Board                           | 3.39 |

| Task File Register              |      |

| Functions                       | 3.39 |

| Error Register                  | 3.40 |

١

)

## 3 HARDWARE PROGRAMMING Continued

| Write Precomp Register     | 3.41    |

|----------------------------|---------|

| Sector Count Register      | 3.41    |

| Sector Number Register     | 3.41    |

|                            | 3.4I    |

| Cylinder Number Low        | • • • • |

| Register                   | 3.41    |

| Cylinder Number High       |         |

| Register                   | 3.41    |

| Sector/Drive/Head Register | 3.42    |

| Status Register            | 3.43    |

| Command Register           | 3.44    |

| Tape Interface Card        | 3.51    |

|                            |         |

| Tape Card Interrupts       | 3.51    |

| Local Memory Space         | 3.53    |

| Main Memory Addressing     | 3.54    |

| Configuration Facility     | 3.55    |

| CTC Counter/Timer          | 3.55    |

| DMA Transfers              | 3.57    |

|                            | -       |

| Tape Drive Interface       | 3.57    |

| Data Format                | 3.60    |

| The IOCB                   | 3.63    |

| Tape Commands              | 3.65    |

| - The second second        |         |

## **4** INTERFACE

)

· )

)

| Internal Interfaces        | 4.1  |

|----------------------------|------|

| Power Supply (Pl)          | 4.1  |

| Tape Drive Controller      |      |

| Board (P2)                 | 4.2  |

| Expansion Card Slot (P7)   | 4.3  |

| Expansion Card Slot (P8)   | 4.6  |

| Floppy Disk Drive (P9)     | 4.9  |

| Memory Expansion           |      |

| Board (P10)                | 4.10 |

| Hard Disk Controller (P21) | 4.12 |

| External Interfaces        | 4.13 |

| Hard Disk Expansion and    |      |

| Hard Disk Data (P22)       | 4.13 |

| Parallel Printer Port (P3) | 4.13 |

| Console (P4) and Serial    |      |

| Printer (P5)               | 4.14 |

## 4 INTERFACE Continued

| RS422 Network (P6)      | 4.15 |

|-------------------------|------|

| User Channels (Pl1-Pl8) | 4.15 |

| User Expansion (P19)    | 4.16 |

| Reset Button (P20)      | 4.16 |

## APPENDICES

| Jumper Configurations | A.1 |

|-----------------------|-----|

| Self Diagnostics      | B.1 |

| Logic Diagrams        | C.1 |

#### FIGURES

)

)

)

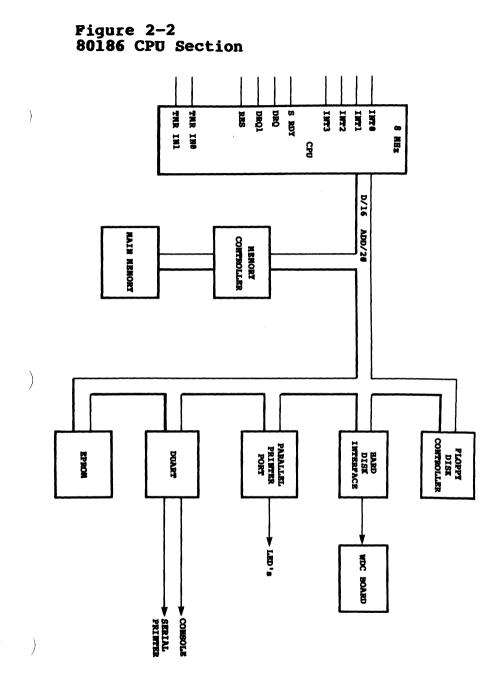

| Tape Expansion Board<br>System Functions<br>80186 CPU Section<br>DUART | 1.4<br>2.3<br>2.5<br>2.7 |

|------------------------------------------------------------------------|--------------------------|

| Parallel Printer Port                                                  | 2.8                      |

| Floppy Disk Controller                                                 | 2.10                     |

| Hard Disk Interface                                                    | 2.12                     |

| Main Memory Section                                                    | 2.14                     |

| Winchester Disk Controller                                             | 2.17                     |

| <b>Z80A 8-Bit Section</b>                                              | 2.19                     |

| Local Memory                                                           | 2.21                     |

| Tape Back-Up                                                           | 2.24                     |

| Parallel Printer and                                                   |                          |

| Status Buffer                                                          | 3.3                      |

| Configure Z80A Buffer Select                                           | 3.12                     |

| Control Signal Input Port                                              | 3.22                     |

| Output Control Port                                                    | 3.23                     |

| Floppy Disk Control Latch                                              | 3.33                     |

| Status Register                                                        | 3.34                     |

| Tape Card Local Memory                                                 |                          |

| Space Map                                                              | 3.53                     |

| High Address Register                                                  | 3.54                     |

| Write Control Latch                                                    | 3.58                     |

| Drive Status Bit Assignments                                           | 3.59                     |

| Control Byte                                                           | 3.61                     |

| IOCB Pointer                                                           | 3.63                     |

| Status Code                                                            | 3.64                     |

|                                                                        |                          |

#### TABLES

| PM Features                | 1.2  |

|----------------------------|------|

| 80186 Interrupt Priorities | 3.2  |

| PACS Register              | 3.4  |

| PCS Address Ranges         | 3.5  |

| MPCS Register              | 3.6  |

| 80186 I/O Port Addresses   | 3.7  |

| Z80A Interrupts            | 3.9  |

| Z80A I/O Port Addresses    | 3.10 |

| Set User and Misc Latch    | 3.11 |

## TABLES Continued

| Default Initialization<br>of the Memory Controller | 3.15 |

|----------------------------------------------------|------|

| Data Output Port                                   | 3.22 |

| DUART Register Addresses                           | 3.24 |

| Mode Register 1 - MRIA & MRIB                      | 3.25 |

| CSRA                                               | 3.27 |

| Interrupt Status Register                          | 3.29 |

| Command Register                                   | 3.31 |

| FDC Register Addresses                             | 3.34 |

| FDC Commands                                       | 3.35 |

| Flag Summary                                       | 3.35 |

| WD1010-05 Registers                                | 3.39 |

| Error Register                                     | 3.40 |

| Status Register                                    | 3.43 |

| Command Register Format                            | 3.45 |

| Tape Card Interrupt Addresses                      | 3.51 |

| Main Board Interrupts to the                       |      |

| Tape Card                                          | 3.52 |

| CTC Channel Assignments                            | 3.56 |

| GCR Conversion Table                               | 3.60 |

| Status Byte O                                      | 3.72 |

| Status Byte 1                                      | 3.74 |

| Power Supply (P1)                                  | 4.1  |

| Tape Drive Controller                              |      |

| Board (P2)                                         | 4.2  |

| Expansion Card Slot (P7)                           | 4.3  |

| Expansion Card Slot (P8)                           | 4.6  |

| Floppy Disk Drive (P9)                             | 4.9  |

| Memory Expansion                                   |      |

| Board (P10)                                        | 4.10 |

| Hard Disk Controller (P21)                         | 4.12 |

| Hard Disk Expansion and                            |      |

| Hard Disk Data (P22)                               | 4.13 |

| Parallel Printer Port (P3)                         | 4.13 |

| Console (P4) and Serial                            |      |

| Printer (P5)                                       | 4.14 |

| RS422 Network (P6)                                 | 4.15 |

| User Channels (P11-P18)                            | 4.15 |

| User Expansion (P19)                               | 4.16 |

|                                                    |      |

)

)

)

## TABLES Continued

4.16 Reset Button (P20) Jumper Default Configuration A.1 Tape Board Default Configuration A.6 Sequence Number and Error Message B.15 Tape Status Bits B.15 Tape Extended Status Bits B.17 Hex Complementary Status Bits B.18 Drive Hex Status Code B.19

#### 1. UNIT OVERVIEW

The Personal Mini (PM) is a high performance, network system, capable of interfacing with the IBM PC, most IBM compatible computers, and the TeleVideo TS 1605 and TPC II systems. The Personal Mini is available in three configurations:

- \* PM/16 Manages eight workstations and contains a 40 megabyte hard disk drive. The system can be expanded to sixteen workstations with the PM Expansion Unit and its eight additional ports. The Expansion Unit also provides 40 megabytes of additional hard disk storage.

- \* PM/16T Manages eight workstations. The system contains an intelligent interface tape backup drive and a 40 megabyte hard disk. It too can be expanded to sixteen workstations with the PM Expansion Unit.

- \* PM/4T Manages four workstations and contains an intelligent interface tape backup drive to backup its 20 megabyte hard disk.

The hard disk in the PM/16 and the PM Expansion Unit can be backed up onto tape with the TS 806C Tape Drive Unit. The unit is available from TeleVideo and includes the necessary software. The Personal Mini is configured as a star network, with RS-422 ports and a simple, low overhead protocol. Table 1-1 lists many of the outstanding features of the systems.

Table 1-1 PM Features

| Maximum<br>‡ of    | P <b>m/4</b> T  | PM/16           | P <b>M/16</b> T |

|--------------------|-----------------|-----------------|-----------------|

| Users              | 12              | 16              | 16              |

| СРО                | 80186 &<br>Z80A | 80186 &<br>Z80A | 80186 &<br>Z80A |

| RAM                | 256-512K        | 256-512K        | 512K            |

| Floppy<br>Drive    | 360K            | 720K            | 360K            |

| Hard Disk<br>Drive | 20M             | 44.5M           | 44.5M           |

| Tape<br>Drive      | 20M             | -               | 2 O M           |

All PM systems use the InfoShare operating system, which offers four levels of security, as well as many other advanced features for handling business, engineering, and programming needs. Also, all of the systems can be expanded to one megabyte of main memory.

This chapter lists the unit specifications, briefly describes the main assemblies, and provides a list of technical references. The specifications are divided into five sections:

```

* Physical Specifications

```

```

* Environmental Specifications

```

```

* Power Requirements

```

```

* Memory and Storage

```

```

* Workstation Cables

```

#### PHYSICAL SPECIFICATIONS

| Height:<br>Width:<br>Depth: | 7.25 in<br>17.50 in<br>16.88 in |           |

|-----------------------------|---------------------------------|-----------|

| Weight:                     |                                 |           |

| PM/16:                      |                                 |           |

| Net:                        | 36.5 lbs                        | (18.1 kg) |

| Shipping:                   | 50.0 lbs                        |           |

| PM/4T, PM/16T:              |                                 |           |

| Net:                        | 41.5 lbs                        | (18.8 kg) |

| Shipping:                   |                                 | (24.9 kg) |

#### Expansion Board Dimensions

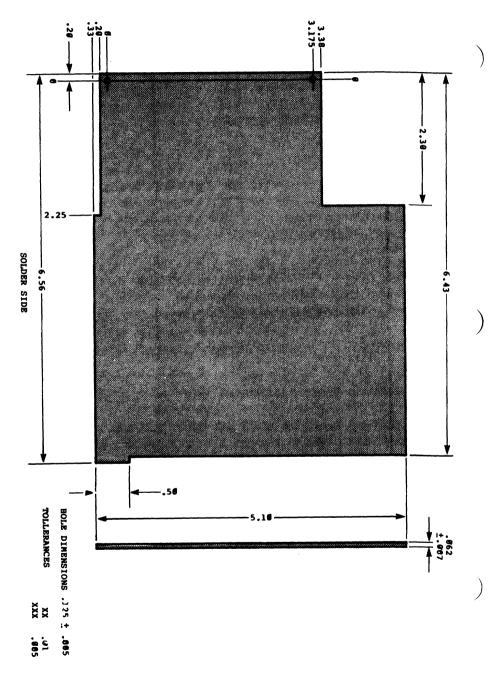

Expansion boards can be installed in the expansion board slots X1 and X2. The board dimensions are illustrated in Figure 1-1.

)

## Figure 1-1 Expansion Board Dimensions

Unit Overview

#### ENVIRONMENTAL SPECIFICATIONS

#### Temperature:

}

| Operating: | 15 to 35 degrees Celsius<br>59 to 95 degrees Fahrenheit |

|------------|---------------------------------------------------------|

| Non-       | -25 to 60 degrees Celsius                               |

| operating: | 13 to 140 degrees Fahrenheit                            |

#### Relative Humidity (non-condensing):

| Operating: | 20-80% |

|------------|--------|

| Transit:   | 5-95%  |

#### Heat Output:

| es  |

|-----|

|     |

| es  |

|     |

|     |

| ies |

|     |

#### Altitude:

| Operating: | 10,000 | ft. | (max) |

|------------|--------|-----|-------|

| Transit:   | 50,000 | ft. | (max) |

#### POWER REQUIREMENTS

#### AC Power:

Voltage: 115/230 Vac +/-10% Frequency: 50/60 Hz Regulation: 1% max

## ) Current (RMS):

| 115Vac | 1.50 ampere |

|--------|-------------|

|        | .75 ampere  |

Unit Overview 1.5

## **Power Consumption:**

| 115Vac | 2 | ampere |

|--------|---|--------|

| 230Vac | 1 | ampere |

## Start Current:

| 115Vac | 1.87 | ampere |

|--------|------|--------|

| 230Vac | 0.94 | ampere |

## DC Power:

PM/16:

| Voltage    | Current       | Regulation<br>(20%-100%) | Power<br>Consumption |

|------------|---------------|--------------------------|----------------------|

| +5         | 7 <b>.</b> 0a | 3% max                   | 35 watts             |

| +12        | 2.0a          | 5% max                   | 24 watts             |

| -12        | 0.5a          | 5% max                   | 6 watts              |

| +12V peak  | (300 ms)      | )                        | 6 ampere             |

| +5V cross  | s regulat:    | ion                      | l% max               |

| PM/4T and  | 3 PM/16T:     |                          |                      |

| Voltage    | Current       | Regulation<br>(20%-100%) | Power<br>Consumption |

| +5         | 12.0a         | 3% max                   | 60 watts             |

| +12        |               |                          |                      |

| <b>T12</b> | 8.0a          | 5% max                   | 96 watts             |

+5V Cross regulation (20%-100%) 1% max

#### MEMORY AND STORAGE

Main Memory:

| PM/4T, PM/16 | 64Kxl  | RAM | 256 | Kbytes |

|--------------|--------|-----|-----|--------|

| Expansion    | 64Kx1  | RAM | 512 | Kbytes |

| PM/16T       | 64Kx1  | RAM | 512 | Kbytes |

| Option       | 256Kx1 | RAM | 512 | Kbytes |

| Option       | 256Kxl | RAM | 1   | Mbyte  |

Unit Overview 1.6

## Z80A Static RAM:

)

' )

)

| All systems<br>Option<br>Option                                 |       | RAM<br>RAM<br>RAM | 64             | Kbytes<br>Kbytes<br>Kbytes |

|-----------------------------------------------------------------|-------|-------------------|----------------|----------------------------|

| Hard Disk:                                                      |       |                   |                |                            |

| PM/4T:<br>Formatted                                             |       |                   | 20 M           | lbytes                     |

| PM/16 and PM/16T<br>Formatted<br>Unformatted                    | :     |                   |                | 6 Mbytes<br>9 Mbytes       |

| Floppy Disk:                                                    |       |                   |                |                            |

| PM/16:<br>Formatted<br>Unformatted<br>TPI (tracks per :         | inch) |                   | 720<br>1<br>96 | Kbytes<br>Mbyte            |

| PM/4T and PM/16T<br>Formatted<br>Unformatted<br>TPI (tracks per |       |                   |                | Kbytes<br>Kbytes           |

| Mana Backun.                                                    |       |                   |                |                            |

#### Tape Backup:

| Formatted              | 20   | Mbytes |

|------------------------|------|--------|

| Unformatted            | 21   | Mbytes |

| Tape speed (nominal)   | 90   | ips    |

| Data density (nominal) | 7772 | bpi    |

#### WORKSTATION CABLES

## Maximum Distance Between Workstation and PM:

450 feet using shielded, twisted-pair cable.

6000 feet using Optic Data Systems ODS214/215 fiber optics modem and duplex fiber cables.

#### MAJOR ASSEMBLIES

#### Main CPU Board

The main CPU board contains the 16-bit CPU functions, 8-bit processor functions, main memory, and all interface signals going to the connectors and the floppy disk.

#### Winchester Disk Controller Board

The controller board controls the internal hard disk drive.

ſ

#### Hard Disk Assembly

PM/16 and PM/16T:

The hard disk is a random-access Winchester assembly with eight recording surfaces and a 44.5 megabyte storage capacity.

#### PM/4T:

The hard disk is a random-access Winchester assembly with four recording surfaces and a 20 megabyte storage capacity.

#### Unit Overview 1.8

#### **Floppy Disk Assembly**

#### PM/16:

The floppy disk drive is a 5 1/4-inch quaddensity, double-sided assembly with a 720 Kbyte capacity. This 96 TPI drive has read/write capabilities but the write function is not software supported. This drive is used to up-load the system. The drive can load programs recorded at 48 TPI in PC-DOS format.

PM/4T and PM/16T: The floppy disk drive is a 5 1/4-inch double-density, double-sided assembly with a 320 Kbyte capacity. This 48 TPI drive is a logical (read and write) drive for PC-DOS formatted diskettes.

#### Interface

The interface is made up of twenty-one interface connectors located on the main CPU board, back panel, front panel, and tape controller board.

#### Tape Backup:

The tape backup drive has an intelligent interface allowing it to directly access main memory. The intelligent tape adaptor is installed in one of the expansion slots and controls the Streaming Tape Drive through a standard QIC-02 intelligent interface board.

#### TECHNICAL REFERENCES

The following publications contain technical data related to the Personal Mini:

\* Intel Microprocessor and Peripheral Handbook (Intel) )

- \* Zilog Data Book (Zilog)

- MOS Microprocessor Data Manual (Signetics)

- \* Synertek Data Catalog (Synertek)

- \* Storage Management Products Handbook (Western Digital)

#### 2. HARDWARE FUNCTIONS

The Personal Mini contains two processors: an Intel 80186 to handle the 16-bit operations, and a Zilog Z80A to handle the 8-bit operations. Both have access to main memory.

The system architecture is designed so that the two processors remain isolated in normal operation with main memory and the interrupts as their only link.

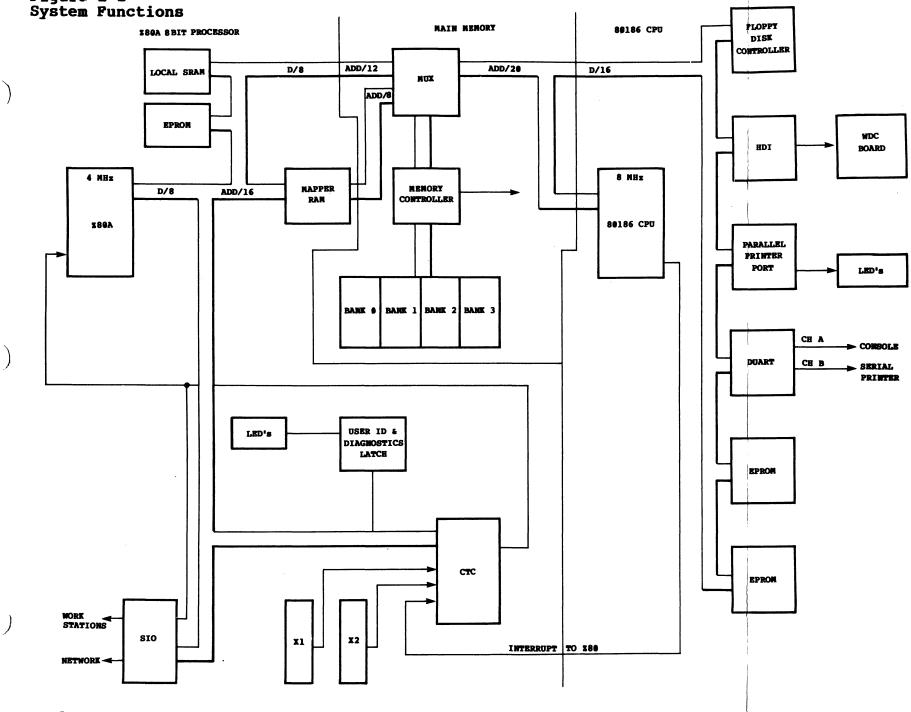

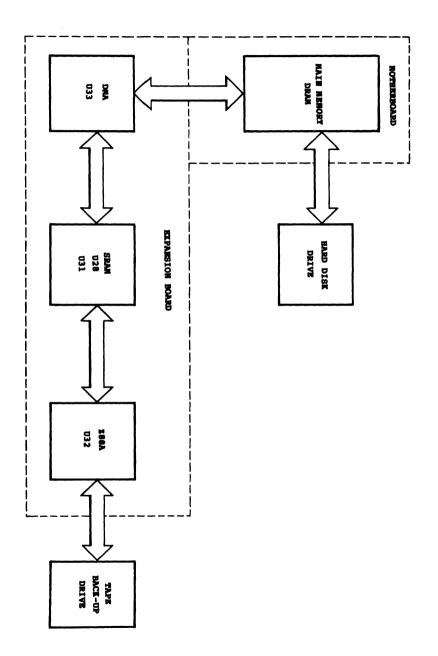

This chapter describes the functions of the unit. The functions described are the 80186 CPU, main memory, Winchester disk controller, Z80A, and tape backup. Figure 2-1 shows the functional block diagram of the unit.

#### 80186 CPU FUNCTIONS

)

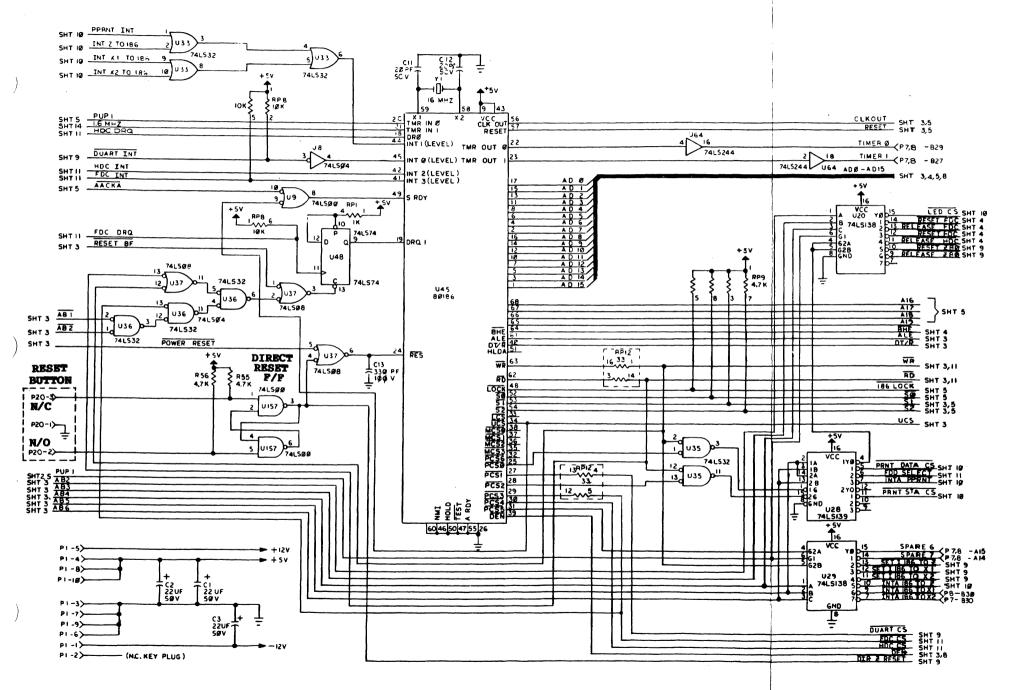

The 80186 CPU (see Figure 2-2) is a 16-bit microprocessor that controls the 16-bit interfaces, system interrupts, and EPROM. The 80186 has sixteen data lines, twenty address lines, and an 8 MHz system clock that is developed from a 16 MHz crystal. The following main board 16-bit interfaces are controlled by the 80186.

- \* DUART - console and serial printer ports

- Parallel printer port \*

- Floppy disk controller Hard disk interface \*

- \*

THIS PAGE WAS INTENTIONALLY LEFT BLANK.

Hardware Functions 2.2

# Figure 2-1 System Functions

Hardware Functions 2.3

5

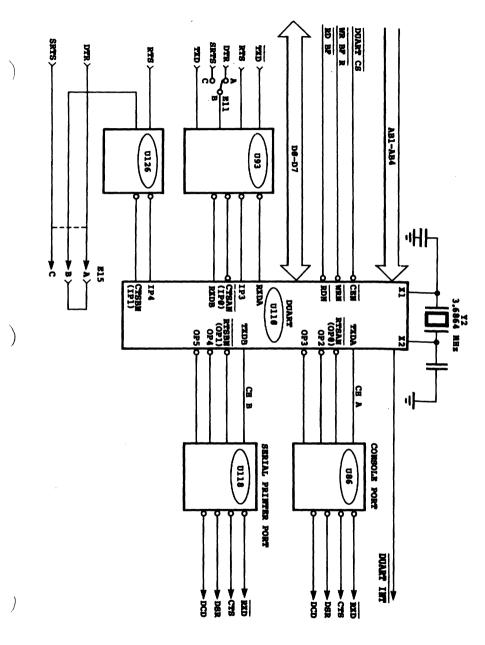

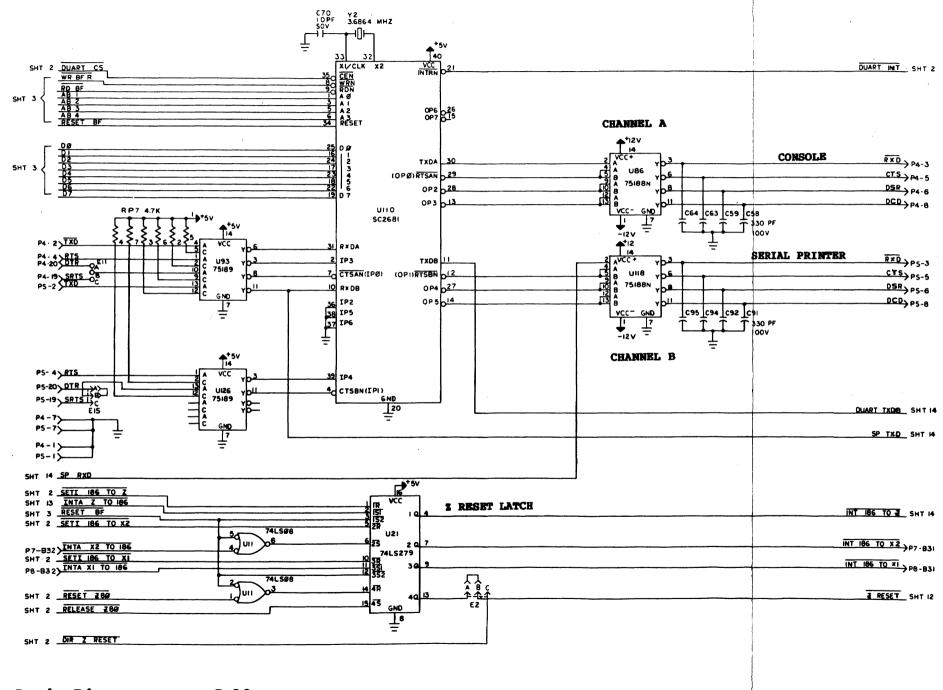

#### DUART (Console and Serial Printer)

The 2681 DUART (see Figure 2-3) controls both the system console port and the serial printer port. This device has programmable, internal baud rate generators derived from a 3.6864 MHz crystal, and provides handshaking signals on the general purpose IPO-IP6 input lines and the general purpose OPO-OP7 output lines.

)

The DUART has two DCE serial RS-232C I/O channels with channel A as the system console port and channel B as the serial printer port. The channels can be reconfigured to a DTE port by the installation of a special cable. They can also be converted for reverse channel protocol by changing the Ell and El5 jumpers (see Appendix A).

The system console port is the system service port that provides keyboard input.

The serial printer port can be configured by the jumpers for two functions. The default configuration sets it as a serial printer port but it can be changed to allow use by a diagnostics console (see Appendix A). This allows access to the Z80A independent of the 80186 CPU operations. This function is not software supported.

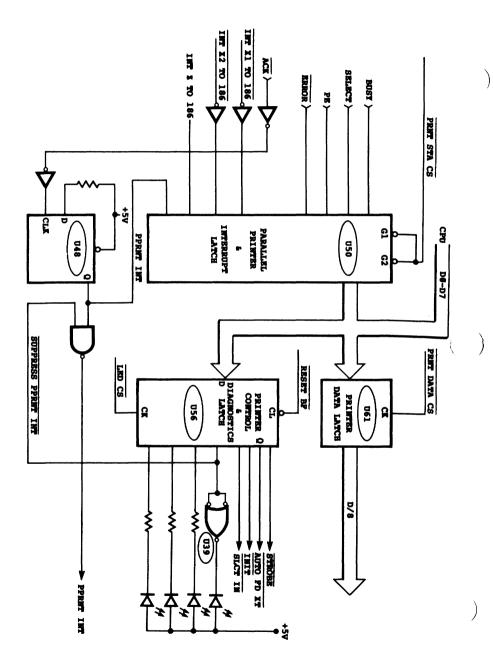

#### PARALLEL PRINTER PORT

The parallel printer port (see Figure 2-4) allows for the use of a parallel data input printer. This section is made up of a parallel printer and interrupt latch (U50), printer data latch (U61), and printer control and diagnostics latch (U56).

#### Hardware Functions 2.6

Figure 2-3 DUART

## Pigure 2-**4** Parallel Printer Port

Hardware Functions 2.8

The parallel printer and interrupt latch receives control signals from the parallel printer and four interrupt signals. These interrupt signals are the INT Z TO 186, -INT X1 TO 186, -INT X2 TO 186, and a software programmable PPRNT INT signal that is not used in the default configuration. Data bits DO-D7 are passed by the latch to the 80186 data bus.

The printer control and diagnostics latch strobes parallel data to the printer and controls the 80186 diagnostic LED's. This latch provides the parallel printer control signals. The most important is the -STROBE signal which strobes the parallel data bits to the printer.

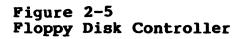

#### FLOPPY DISK CONTROLLER

The floppy disk controller is a Western Digital WD1770 (see Figure 2-5). It contains internal registers to accept highlevel commands from the 80186. The controller interface to the 80186 consists of an 8-bit, bidirectional, data access bus for the transfer of status, data, and commands. All 80186 communication with the drive occurs through these lines. The controller contains an internal digital data separator, digital phase lock loop circuit, and write precompensation.

The drive select buffer (Ull2) controls floppy disk drive selection, motor on, and side selection.

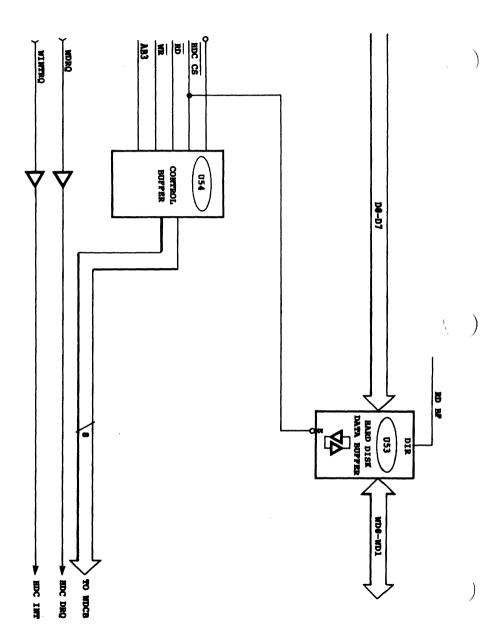

#### HARD DISK INTERFACE

The hard disk interface (see Figure 2-6) includes the Winchester disk controller Board, which is discussed later in this chapter. The interface provides data and control lines from the 80186 to the WDC board.

The hard disk data buffer (U53) holds data for transfer to the WDC board or the 80186.

The control buffer (U54) transfers the control signals to the WDC board.

#### SYSTEM INTERRUPTS

The 80186 has four interrupt inputs: INT 0, INT 1, INT 2, and INT 3. All interrupts are maskable and are prioritized. The interrupts are described according to their priority with the highest priority listed first.

**INT 0** is the DUART interrupt. It is activated when either the system console or serial printer has completed a command function and is ready for another command.

**INT 1** receives one of four interrupts on this input. They are PPRNT INT, INT Z TO 186, -INT X1 TO 186, and -INT X2 TO 186. When this interrupt input is active, the 80186 polls the Parallel Printer and Interrupt Latch (U50) to find out which interrupt is active. This latch also holds error signals from the parallel printer.

**INT 2** is the hard disk controller interrupt. It is activated to let the 80186 know that the previous command has been completed. Figure 2-6 Hard Disk Interface

**INT 3** is the floppy disk interrupt. The drive activates the signal to inform the 80186 CPU that the previous command has been completed and that a new drive command can be issued.

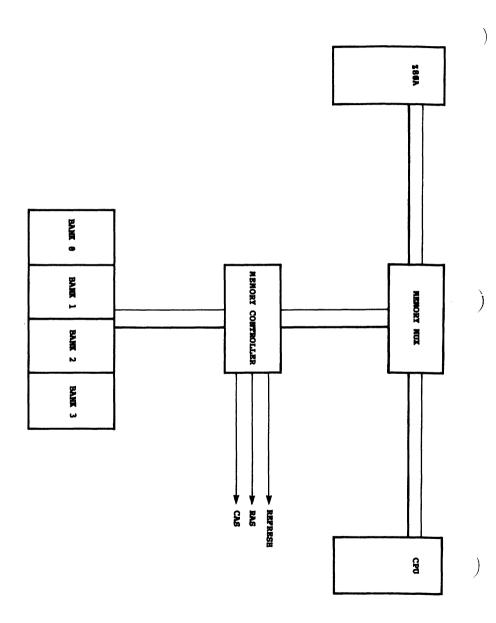

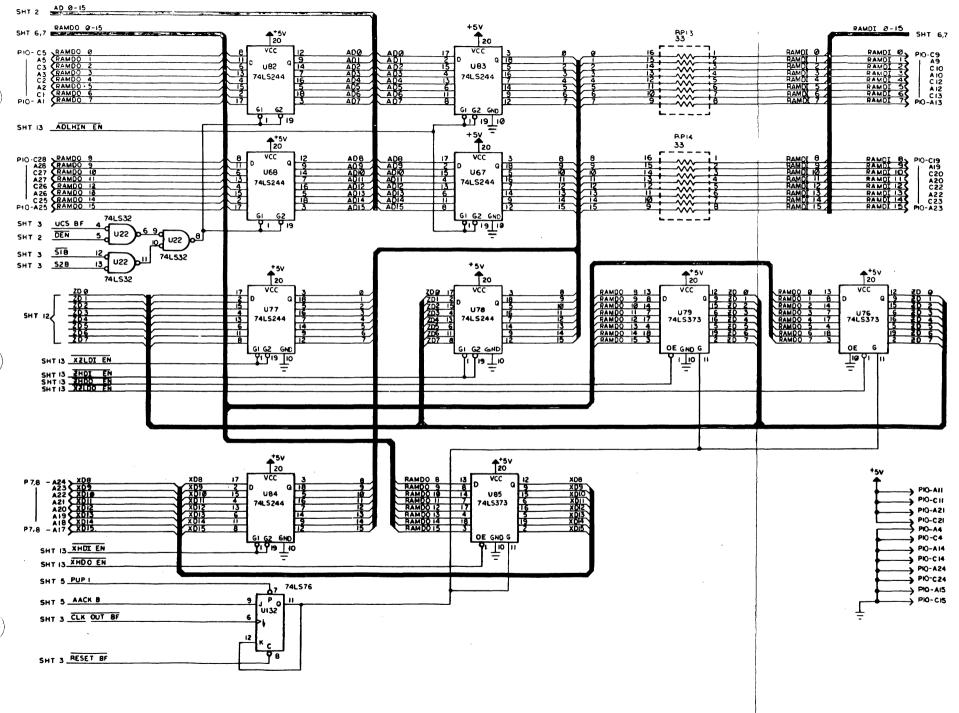

#### MAIN MEMORY

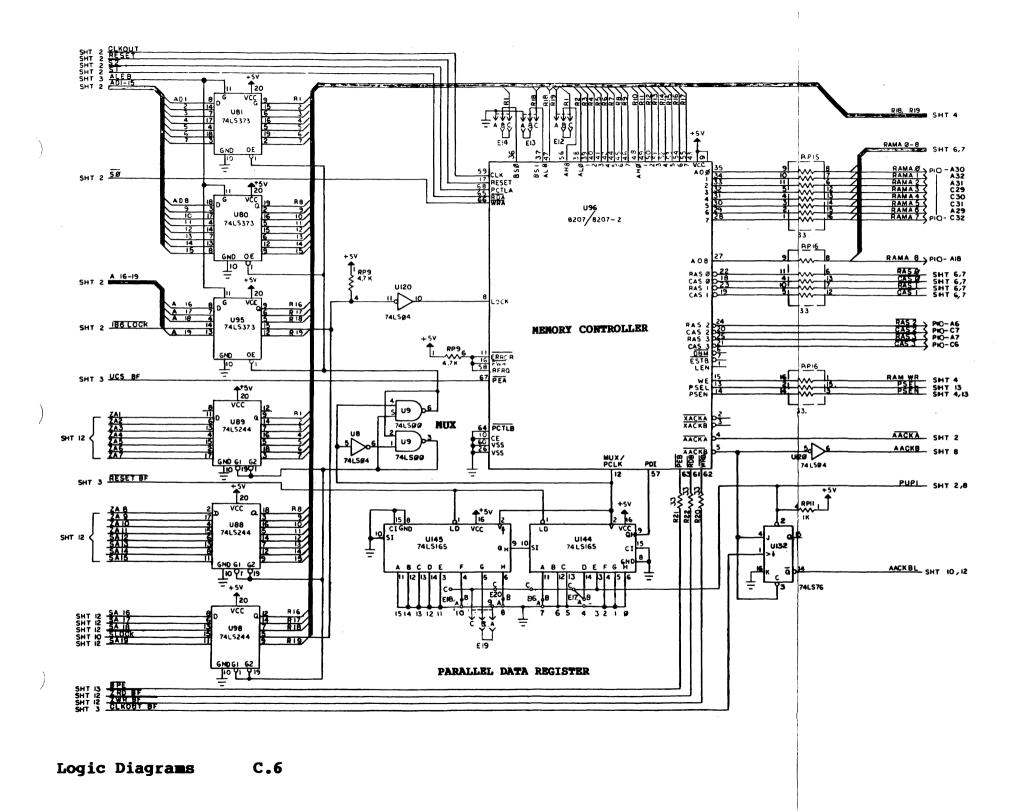

Main memory (see Figure 2-7) is a two-port memory that is equally addressable by the 80186 and the Z80A. The intelligent interface tape backup can also directly access main memory on the 8-bit bus but does not have access to the memory mappers. The 80186 and Z80A can both access up to one megabyte of memory. The main memory contains a memory MUX, memory controller, and memory banks.

#### Memory MUX

The memory MUX (U9) is an R-S flip-flop that enables either the 80186 or Z80A to address main memory. The MUX is set or reset by the memory controller (U96) MUX/PCLK signal.

#### Memory Controller

The 8207 memory controller is configured as a dual-port controller. Port A holds the 80186 CPU address lines and port B holds the Z80A address lines. The controller arbitrates the processor requests and directs data to or from the appropriate port. A priority system reassigns priorities based on past history. Requests are internally queued. Figure 2-7 Main Memory Section

The memory controller limits the number of functions performed by main memory at any time to one event. The controller may be addressing for the Z80A or the 80186, or performing a refresh cycle.

At power-up, parallel data bits from the parallel data register (U144 & U145) are sent to the PDI input. This input programs the controller's jumper selectable options.

Refresh requests are generated internally for the dynamic RAM's. This frees the processors from this function. The controller provides RAS (row) and CAS (column) signals for each of four possible memory banks allowing it to access one megabyte of memory.

The memory-locking feature gives each processor uninterrupted access to a portion of the memory. This allows one processor to complete its data processing before the other processor can access that area.

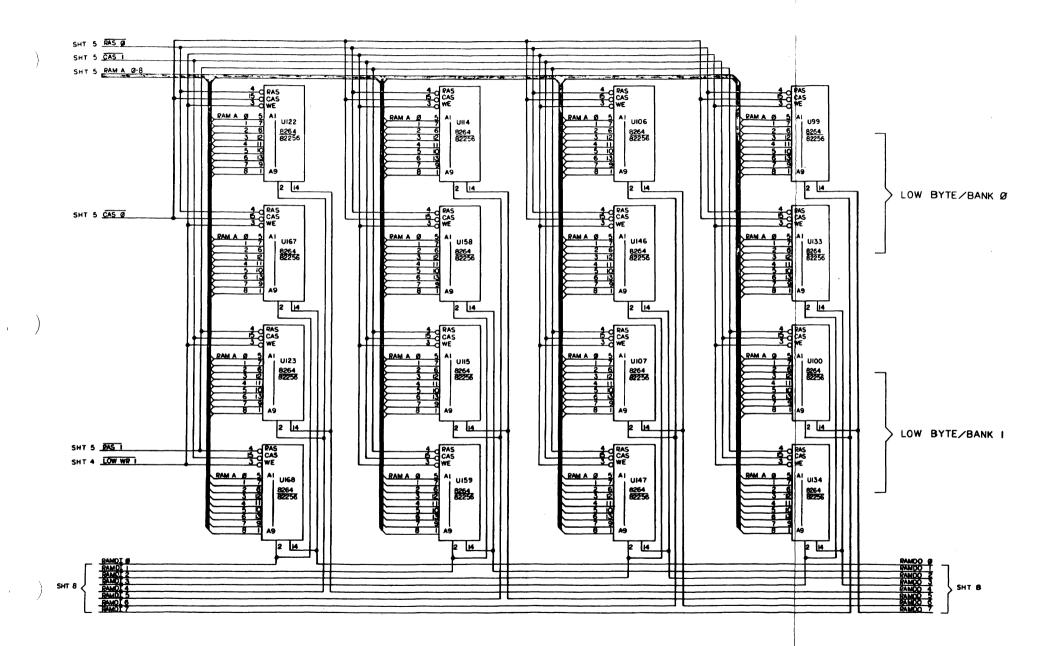

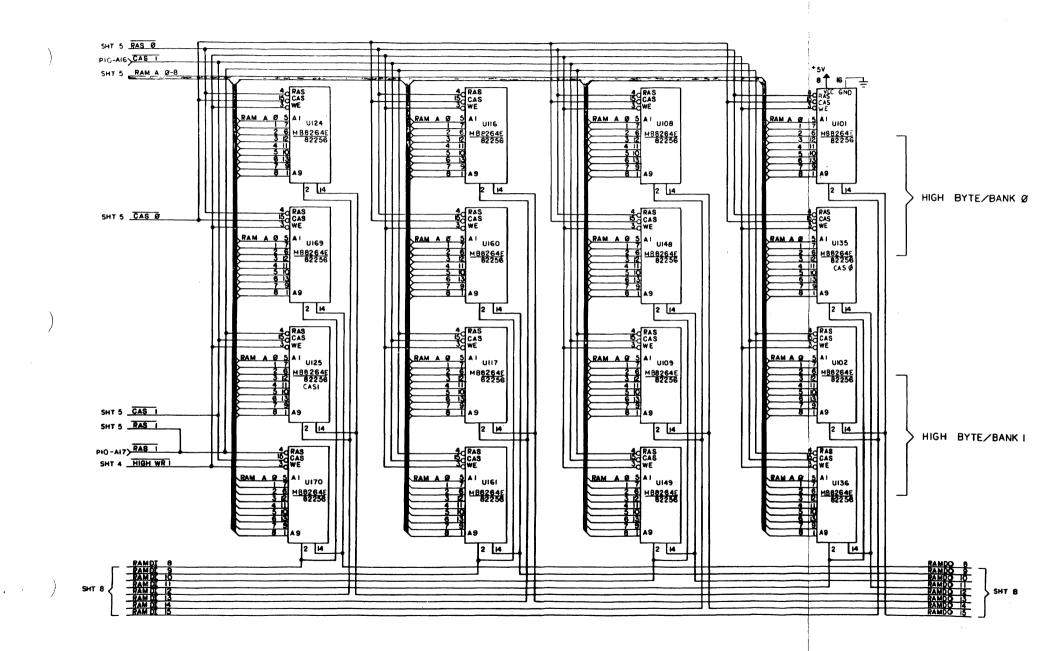

## Memory Banks

)

If the system contains a memory expansion board, the memory controller divides the memory into four banks. The main memory contains 64Kxl dynamic RAM chips to provide 256 Kbytes of main memory. The memory expansion board provides another 256 Kbytes of memory expanding it to 512 Kbytes. The 256 kbyte configuration is basic for the PM/4T and PM/16 units, and the 512 Kbyte configuration is basic for the PM/16T unit. Another option is the use of 256Kxl dynamic RAM chips to provide either 512 Kbytes or 1 Mbyte of main memory. Each bank has its own RAS (row) and CAS (column) lines to strobe the address. The RAS and CAS are selected by the decoding of the program bits RB1 and RB2, and bank input bits BS0 and BS1. Twenty address lines are required to address one megabyte of memory.

The signals from the high and low byte write enable are decoded by the Write Enable Decoder (U49).

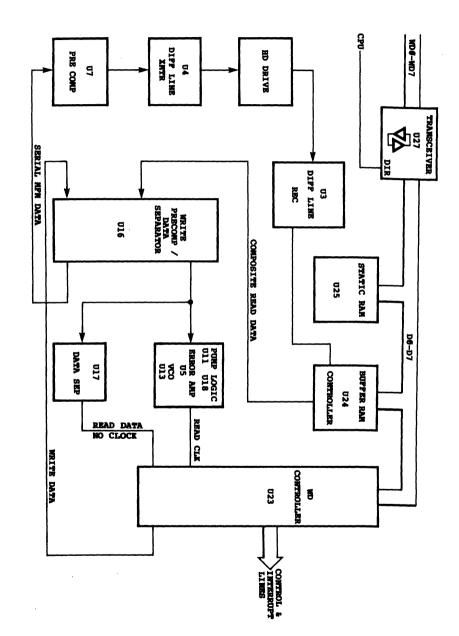

#### WINCHESTER DISK CONTROLLER

The Winchester disk controller board (see Figure 2-8) provides the main controller function for the Winchester disk drive(s).

The WD controller (U23) can handle up to four disk drives and provides all control and data handling functions needed to interface the system with a disk drive.

The controller interfaces the host through a bi-directional transceiver (U27), which is controlled at its DIR input by the 80186. The data bus goes to the controller (U23), buffer RAM Controller (U24), and static RAM (U25).

The static RAM is controlled by the RAM buffer controller and stores one sector of read or write data.

The RAM buffer controller controls the RAM sector data and the head and drive select lines. It also controls the interface between the static RAM and the controller.

Hardware Functions 2.17

)

The write precompensator/data separator (U16) provides the write precompensation logic and data separator control logic that sends a synthesized read clock and read data to the controller.

The controller board receives commands from the 80186 CPU, initiates the commands, and sends status signals to the CPU.

During a read operation, composite read data (serial) is received by the differential line receiver (U3) from the hard disk. This data is passed to the buffer RAM Controller.

During a write operation, data is sent from the write precompensator/data separator to the precompensator, and then to the differential line transmitter (U4) for transmittal to the hard disk.

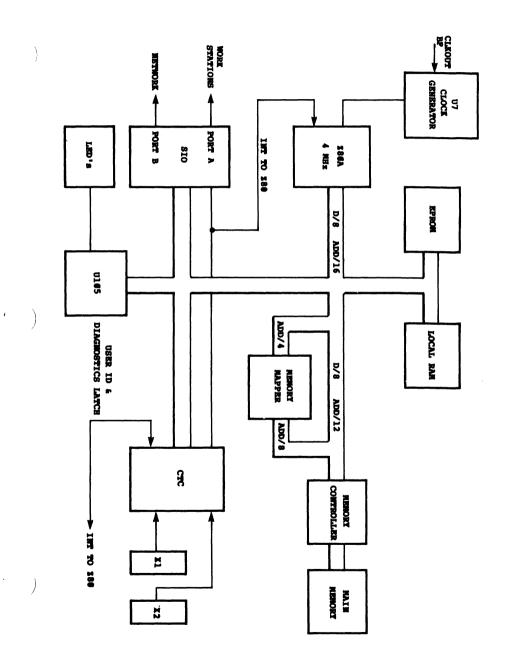

#### 8-BIT NETWORKING FUNCTIONS

The 280A 8-bit processor (see Figure 2-9) controls the 8-bit functions that include networking, expansion cards, and 8-bit diagnostics. The processor runs on a 4 MHz clock generated by the clock generator (U7) from the CPU CLKOUT BF signal. The processor has eight data lines and sixteen address lines. The functional areas of the processor are local memory, memory mapping, SIO and work stations, CTC, and expansion slots. Figure 2-9 280A 8-Bit Section

#### Local Memory

The local memory (see Figure 2-10) has a 4kbyte EPROM and 4 Kbytes of static RAM, expandable to 16 Kbytes. The EPROM performs the 8-bit initialization and diagnostics. The static memory polls the workstations for a service request since interrupts are not used for the workstations.

)

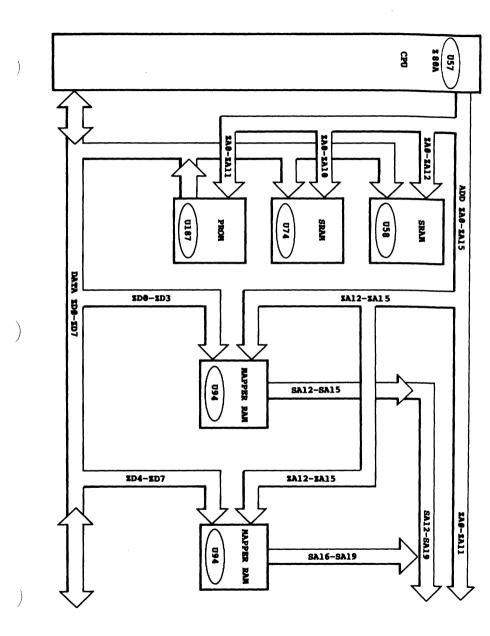

# Memory Mapping

The Z80A has sixteen address lines which allow it to access up to 64 Kbytes of memory. The PM can have up to 1 Mbyte of memory. This means that, in order to access 1 Mbyte of memory, twenty address lines are needed. Address bus bits 0-11 go to the memory controller while bus bits 12-15 go to the memory mapping RAM's (U94 and U97), which are decoded into eight address lines (bus bits 12-19). These eight address lines go to the memory controller to produce a 20-bit address bus.

## Serial I/O And Workstations

The Serial I/O (SIO) contains two RS-422 ports with port A as the workstation port and port B as the daisy-chain network port. Port B also allows for direct access to the 280A by a diagnostic console. A jumper configuration change (see Appendix A) is required for this. The SIO 800 KHz baud rate is generated by the clock generator (U7) which also generates the 800 KHz receive clock to the workstations. Figure 2-10 Local Memory

Port A sends out the TXDA signal to select the one workstation out of the possible sixteen that is latched in the user ID and diagnostics latch (U105). This latch output is also used for diagnostics at power-up. When the diagnostics have been completed, it latches the binary-coded user select address. The ZLK MEM line locks the memory area that the Z80A is using. This allows the processor to complete its operation before the memory area is accessed. The INHIBIT BUS RO signal is used to establish the priority of the expansion cards or the workstations. The -Z PROM OFF signal allows the EPROM memory area to be masked off.

)

#### Counter-Timer Circuit

The CTC (Counter-Timer Circuit) is a four channel device of which only three are currently being used. The CTC is used as an interrupt controller to control and prioritize the following interrupts, which are listed from the highest to lowest in priority:

-INT 186 TO Z -INT X1 TO Z -INT X2 TO Z

In response to an interrupt signal, the CTC issues an interrupt to the Z80A CPU, which in turn interrupts the 80186. The 80186 determines the source of the interrupt by reading the internal registers of the CTC.

# **Expansion Slots**

There are two expansion card slots mounted on the main board. Slots X1 (P8) and X2 (P7) are used for system expansion including the intelligent interface tape backup. An expansion card may contain its own DMA controller for direct access to main memory. The expansion card must be 8-bit to access the 8-bit Z80A bus. On power-up, the processor checks bits 1 and 2 of the buffer (U62) to determine if the slots are occupied. For more information on the expansion slots, refer to Chapter 3.

#### TAPE BACKUP

)

The tape backup (see Figure 2-11) has an intelligent interface that can access the main memory on the 8-bit processor bus. The tape expansion board can be installed in either the X1 or X2 expansion slot but there are jumper requirements (see Appendix A). The tape backup has a storage capacity of 20 Mbytes. The tape expansion board has a DMA and a processor control section.

The local memory is made up of 8 Kbytes of EPROM with a 4 kbyte option, and 4 Kbytes of static RAM with an 8-kbyte or 16-kbyte option.

#### Tape Operation

The 80186 moves data from the hard disk to main memory on the main board. This occurs during the CPU operating cycle. Figure 2-11 Tape Backup

)

}

The DMA requests the 8-bit data bus from the two processors on the main board, and when acknowledged, accesses the bus. All 8-bit functions occur during the Z80A operating cycle. The DMA fetches the data memory address and moves the data to the local static RAM. The DMA continues this process to keep the RAM full as long as there is data in main memory for the tape backup.

)

The Z80A on the tape expansion board provides the local intelligence to access the main memory and communicate with the 80186 microprocessor. It controls the tape drive interface and runs on a 4-MHz clock. The processor moves data from the static RAM to the tape drive in the streaming mode.

The DMA and processor run concurrent operations to keep the RAM buffer full to maintain the streaming of the tape.

#### 3. HARDWARE PROGRAMMING

This chapter provides the programmer with the information necessary to interface with the system hardware. Included in the chapter are discussions on I/O port addresses, coding tables, command codes, and registers for the 80186, Z80A, and the tape expansion card.

#### 80186 MICROPROCESSOR

The 80186 is a 16-bit internal and external HMOS microprocessor device with a 20-bit address bus. The 80186 performs all DMA transfers to the floppy and hard disk drives, and handles interrupts from the 280A 8-bit processor and from peripheral devices. This microprocessor is also responsible for performing diagnostics on the 16-bit side of the system at system initialization. For complete information on the 80186, refer to the Intel iAPX 86/88, 186/188 User's Manual.

#### 80186 Interrupts

The interrupt lines INTO through INT3 on the 80186 provide four prioritized levels of interrupts to service hardware requirements, with INTO having the highest priority. The interrupt levels are shown in Table 3-1. To properly service interrupts, the system software must program the interrupt control registers of the 80186 into the fully-nested mode (non-cascade, non-iRMX operation). All interrupts are maskable.

Interrupts from the 80186 are applied on a SETI line to the reset pin of a set-reset flip-flop. The acknowledgement from the Z80A 8-bit side or from an expansion card returns the flip-flop to the set state. A system reset also places the flip-flop into the set state.

Table 3-1

80186 Interrupt Priorities

| Level | Input | Device                                                                                             |

|-------|-------|----------------------------------------------------------------------------------------------------|

| 0     | INTO  | Serial printer or console port.                                                                    |

| 1     | INTl  | Parallel printer, Z80<br>microprocessor,<br>expansion card slot 1,<br>or expansion card slot<br>2. |

| 2     | INT2  | Winchester hard disk<br>controller board.                                                          |

| 3     | INT3  | Floppy disk controller board.                                                                      |

To determine which device is sending an interrupt on INT1, the 80186 polls bits 4 through 7 of the parallel printer and interrupt status buffer at address %0120. Refer to Figure 3-1 for the bit assignments to the buffer. )

Figure 3-1 Parallel Printer and Status Buffer (\$0120)Bit 6 5 4 7 L L 1 I L 1 0 = Parallel printer interrupt ł 1 1 = Normal input I 1 L 1 I 0 = Normal input I 1 1 = 280 interrupt L 0 = Normal input 1 = Expansion card slot 1 I I interrupt L 0 = Normal input 1 = Expansion card slot 2 interrupt

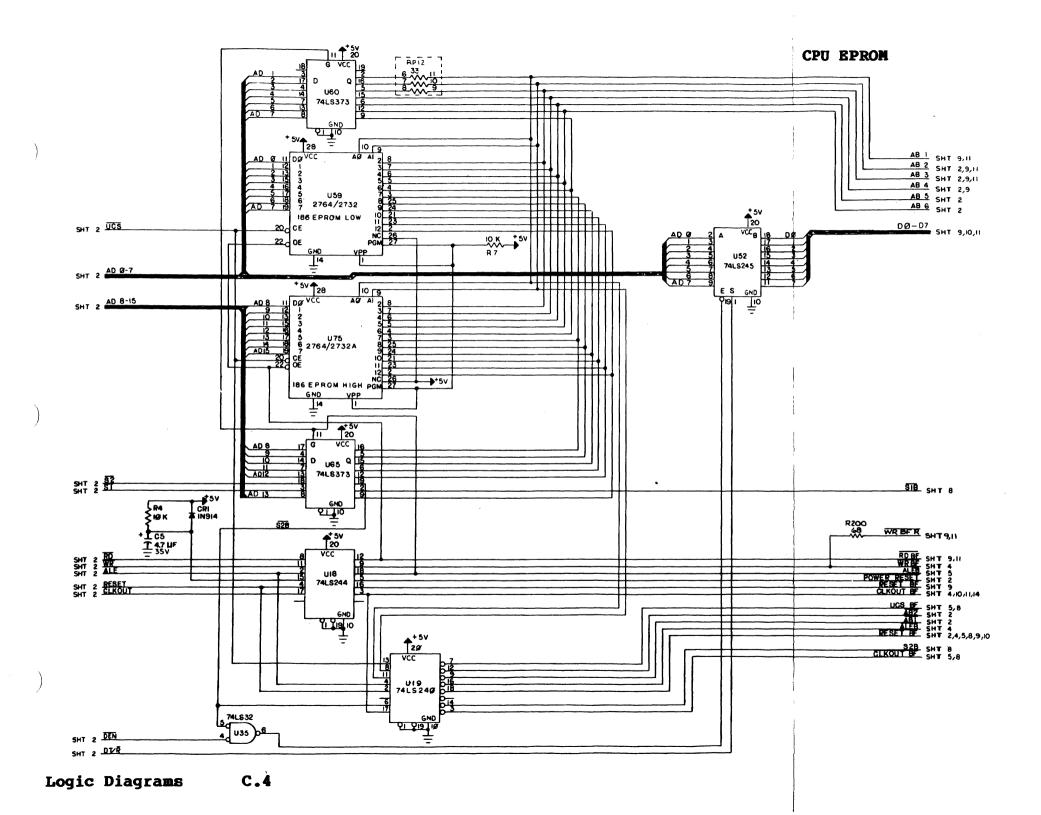

# 80186 Read-Only Memory

Standard read-only memory for the 80186 processor is organized as 4K x 16 bits in two chips, optionally expandable to 8K x 16 bits. Standard ROM is located in address space %FE000 through %FFFFF. The size of the ROM is contained in the firmware itself, thus eliminating the need to change jumpers or switch settings with a change in ROM.

The UCS pin of the 80186 decodes the memory address of the ROM devices. After system reset, the UMCS register must be initialized to the ROM block size and programmed with one wait for the ROM devices.

## 80186 I/O Port Selection

System I/O port selection is performed through the six peripheral chip select lines PCS0 through PCS5 of the 80186. The lines are controlled through the PACS register and the MPCS register. These registers set the programmable base address (PBA) of the peripherals and specify whether the peripherals are mapped into memory or I/O space. Both registers must be accessed to activate the peripheral chip select lines.

The PACS register defines the starting address of the peripheral chip select block. Refer to Table 3-2 for the bit assignments to the register.

## Table 3-2 PACS Register

| Bits   | Function                                                                                                                     |

|--------|------------------------------------------------------------------------------------------------------------------------------|

| 15 - 6 | Correspond to bits 19 through 10<br>of the 20-bit programmable base<br>address (PBA) of the peripheral<br>chip-select block. |

| 5 - 3  | Set to 1.                                                                                                                    |

| 2 - 0  | Specify the READY mode and the wait states, and are encoded as follows:                                                      |

|        | Bits<br>2 1 0<br>0 0 0 = Zero wait states,<br>external RDY also used.                                                        |

|        |                                                                                                                              |

3.4

)

#### Table 3-2 continued Function Bits 2 - 0Bits 2 1 0 n 1 0 = Two wait states inserted, external RDY also used. 1 = Three wait states 1 0 inserted, external RDY also used. 0 = Zero wait states, 1 0 external RDY ignored. 0 1 = One wait state 1 inserted, external RDY ignored. 1 0 = Two wait states1 inserted, external RDY ignored. 1 1 1 = Three wait states inserted, external RDY ignored.

Table 3-3 shows the address range of each peripheral chip select with respect to the PBA contained in the PACS register.

# Table 3-3 PCS Address Ranges

)

| PCS Line | Active Between Locations |

|----------|--------------------------|

| PCS0     | PBA - PBA+127            |

| PCS1     | PBA+128 - PBA+255        |

| PCS2     | PBA+256 - PBA+383        |

| PCS3     | PBA+384 - PBA+511        |

| PCS4     | PBA+512 - PBA+639        |

| PCS5     | PBA+640 - PBA+767        |

The MPCS register controls the mode of operation for the peripheral chip select lines. Refer to Table 3-4 for the bit assignments. Bit 6 of this register determines whether the selects are mapped into memory or I/O space. A one for this bit maps the peripherals into memory space. A zero maps the peripherals into I/O space.

## Table 3-4 MPCS Register

Bits Function

15 Set to 1.

14 - 8 Define the size of the memory block. Only one bit can be set at a time.

| Bits    | Total<br>Block | Individual<br>Select |

|---------|----------------|----------------------|

| 14 - 8  | Size           | Size                 |

| 0000001 | 8K             | 2K                   |

| 0000010 | 16K            | 4K                   |

| 0000100 | 32K            | 8K                   |

| 0001000 | 64K            | 16K                  |

| 0010000 | 128K           | 3 2 K                |

| 0100000 | 256K           | 64K                  |

| 1000000 | 512K           | 128K                 |

7 Set to 1.

6 If 0, the peripherals are mapped into memory space. If 1, the periherals are mapped into I/O space.

#### Table 3-4 continued

#### Bits Function

- 5 3 Set to 1.

- 2 0 Specify the READY mode. Refer to Table 3-3 for the coding.

The I/O port addresses for the 16-bit processor are listed in Table 3-5. The port addresses assume that the programmable base address of the PACS register is zero, that the relocation register is in the default %20FF, and that the ports are I/O mapped. This arrangement assures that the I/O space for the internal control register block is located outside of the low order address space.

Table 3-5 80186 I/O Port Addresses

Address

1

Function

| \$0000               | Printer Control/Diagnostic |

|----------------------|----------------------------|

|                      | Indicators Latch Select    |

| 80004                | Reset FDC                  |

| <b>%0008</b>         | Release FDC Reset          |

| \$000C               | Reset HDC                  |

| \$0010               | Release HDC Reset          |

| 80014                | Reset Z80                  |

| \$0018               | Release Z80 Reset          |

| <b>%0020</b>         | Printer Data Latch Select  |

| <b>%0040</b>         | Floppy Disk Drive Control  |

|                      | Latch                      |

| <b>%0060</b>         | Printer Interrupt          |

|                      | Acknowledge                |

| <b>%0080 - %009E</b> | DUART Device Registers     |

# Table 3-5 continued

| Address              | Function                                                  |

|----------------------|-----------------------------------------------------------|

| <b>%0120</b>         | Parallel Printer and<br>Interrupt Status Buffer<br>Select |

| <b>%0180 - %018E</b> | Floppy Disk Controller<br>Device Registers                |

| <b>%0200 - %020E</b> |                                                           |

| <b>%0280</b>         | Spare 6                                                   |

| 80290                | Spare 7                                                   |

| %02A0                | Set Interrupt 80186 to Z80                                |

| \$02B0               | Set Interrupt 80186 to<br>Expansion Card 1                |

| <b>%</b> 02C0        | Set Interrupt 80186 to                                    |

| %02D0                | Expansion Card 2<br>Interrupt Acknowledge 80186<br>to 280 |

| <b>%02E0</b>         | Interrupt Acknowledge 80186<br>to Expansion Card 1        |

| <b>%02F0</b>         | Interrupt Acknowledge 80186<br>to Expansion Card 2        |

| %FF00 - %FFFE        | 80186 Internal Registers                                  |

#### **Z80 MICROPROCESSOR**

The task of interfacing with the workstations is performed by the 8-bit side of the motherboard with a Z80A CPU running at 4 MHz.

## **280 Interrupts**

Interrupts from the Z80A SIO and Z80A CTC are daisy-chained to the Z80A CPU, with the SIO device having the highest priority. Other interrupts are generated at timer inputs 1 through 3 of the CTC. These interrupts are listed in Table 3-6.

3.8

## Table 3-6 280A Interrupts

Timer

Channel Function

| 1 | Interrupt from 80186 to Z80A CPU               |

|---|------------------------------------------------|

| 2 | Interrupt from expansion slot 1<br>to Z80A     |

| 3 | Interrupt from expansion slot 2<br>to Z80A CPU |

The timer channel is loaded with a count of l; an incoming interrupt decrements this count to 0 to generate a CTC interrupt. The expansion cards can also directly interrupt the 80186, as previously described in Table 3-3. Interrupt acknowledge signals to these devices are sent through the Z80A CPU I/O ports at the addresses listed in Table 3-7.

Interrupts are sent from the Z80A CPU to the 80186 through the Z80A CPU port address %06.

# **Z80 Read-Only Memory**

The 8-bit processor ROM occupies the lower 4 Kbytes of Z80A CPU address space from %0000 through %0FFF. The section also has a local RAM area in the upper Z80A CPU space from %F000 through %FFFF.

Standard local memory is expandable with one or two 8K x 8 static RAM devices to begin local RAM at %E000 or %C000.

# Z80A I/O Ports

Table 3-7 lists the I/O port addresses for the 8-bit processor section.

## Table 3-7 280A I/O Port Addresses

| Address          | Function                                              |

|------------------|-------------------------------------------------------|

| 800              | Interrupt Acknowledge Z80A<br>CPU to 80186            |

| <b>%02</b>       | Interrupt Acknowledge Z80A<br>CPU to Expansion Slot 1 |

| 804              | Interrupt Acknowledge Z80A<br>CPU to Expansion Slot 2 |

| 806              | Interrupt Z80A CPU to 80186                           |

| 808              | Configure Z80A Buffer Select                          |

| 80A              | Spare 5                                               |

| 80C              | Set User ID and Misc. Latch<br>Enable                 |

| <b>%0E</b>       | Set Memory Map Enable                                 |

| 810 - 813        | Z80A CTC Internal Registers                           |

| <b>%20 - %23</b> | Z80A SIO Internal Registers                           |

| <b>%60 - %FF</b> | Expansion Card I/O                                    |

The first four bits of the set user ID and misc latch at address %0C select one of the sixteen workstation channels for input. The latch is sequenced as follows:

| Bit 3 | Bit 2 | Bit l | Bit O | User No. |

|-------|-------|-------|-------|----------|

| 0     | 0     | 0     | 0     | 1        |

| 0     | 0     | 0     | 1     | 2        |

| 0     | 0     | 1     | 0     | 3        |

| 0     | 0     | 1     | 1     | 4        |

)

This continues in binary sequence up to workstation sixteen:

Bit 3 Bit 2 Bit 1 Bit 0 User No. 1 1 1 1 1 16

Bits 0 through 3 of this latch are also used to light the diagnostic LED indicators 1 through 4. These indicators are lit when the bits are low.

The functions of bits 4 through 7 of the latch are listed in Table 3-8.

# Table 3-8 Set User ID and Misc Latch (%OC)

#### Bit Function

4

)

)

- Network Transmit Enable Enables transmission on the RS-422 network channel to allow communications between multiple PM systems.

- 5 8-Bit Processor Main Memory Locking - activates the main memory locking feature of the 16bit processor section.

- 6 Inhibit Bus Request Inhibits a bus request from an expansion card when the cards and the Z80A CPU simultaneously request the section data and address busses.

7 Disable 8-Bit Processor ROM -Frees the address space normally used by the ROM for memory mapping. When writing to a portion of this latch, care must be taken to preserve the remaining bit values. The configure Z80A buffer select is read at address %08. The bit assignments for the buffer are listed in Figure 3-2. Figure 3-2 Configure Z80A Buffer Select (\$08)Bits 7 6 5 4 3 2 1 0

I

I

I

I

I

I

I

I

= Normal operation

I

I

I

= No expansion card in

I

I

I

slot 1

1 L 1 1 1 L I. 1 II0= Expansion cardII0= Expansion cardII1= No expansion card in 1 1 F 1 1 slot 2 1 0 = Expansion card presentin slot 2 I I 1 1 1 Spare for expansion cards 1 1 Spare for expansion cards Spare for expansion cards Spare for expansion cards Not used

## **Z80A** Processor Section Reset

The 8-bit processor section is reset at 80186 I/O port address %0014. This reset includes the expansion card slots. After reset, the 8-bit processor section must be software released at 80186 I/O port address %0018 to begin operation. After release, the Z80A CPU executes a self-diagnostic test as described in Appendix C.

## Hardware Programming

)

## MAIN MEMORY

)

Main memory is contained in 64K x 1 dynamic RAM devices. Standard memory is 256 Kbytes, expandable to 512 Kbytes with an add-on board, and to 1 Mbyte with 256K x 1 dynamic RAM devices. This area can be accessed by either the 16-bit processor or the 8-bit processor sections under control of the dual port RAM controller. When the 8-bit section, including an 8-bit expansion card, accesses main memory, the 20-bit address for the controller is produced through a mapper in the 8-bit section. Generation of this mapped address is described later in this section.

## Dual Port RAM Controller

Main memory is controlled through an Intel 8207 Advanced Dynamic RAM Controller device. This device provides independent access to main memory by each processor section on a last-access-served-first priority scheme. The 8207 generates all control signals for memory, including programmable refresh and data transfer acknowledge. A detailed description of the 8207 is contained in the Intel Microsystem Components Handbook, Volume I.

Port A of the 8207 is connected to the 16bit processor. This port runs in the slowcycle, synchronous, status interface mode of the controller. There are no wait states for a normal memory access with 150 nanosecond RAM devices. Port B of the 8207 services the 8-bit processor and expansion card bus. Port B runs in the slow-cycle, asynchronous, command interface mode of the controller. One wait state is required for a normal memory read and two wait states for an normal memory write.

If one port attempts to access the memory while the other port is active, the port attempting the access must wait from 1 to 5 wait states for 80186 memory cycles (125 nanoseconds/wait), or 3 to 5 wait states for Z80A memory cycles (250 nanoseconds/wait). Longer wait states are necessary if the controller is refreshing memory during a simultaneous request.

Address lines from each processor are multiplexed to a single set of lines for the 8207. Address bit 0 selects the high or low byte during the access along with high byte enable lines -BHE for the 80186, or -ZRBH for the Z80A. Jumper options finalize the memory selection, as described under Memory Organization below.

The 8207 is programmed through a hardware initialization shift register during system reset. Table 3-9 lists these default states. )

)

; )

. )

Table 3-9 Default Initialization of the Memory Controller

| Bit    | Set/Function                      |

|--------|-----------------------------------|

| 0      | Low. Non-ECC mode.                |

| 1      | Low. Port A set asynchronous.     |

|        | Low. Port B set synchronous.      |

| 2<br>3 | High. Slow cycle iAPX 86 mode.    |

| 4      | High. Slow (150 nanoseconds)      |

|        | RAM.                              |

| 5/6    | Low. RAS and CAS to banks as      |

|        | selected by bank select inputs to |

|        | memory controller:                |

|        | (BS1) (BS0) Utilization           |

|        | 0 0 RASO/CASO to Bank 0           |

|        | 0 1 RAS1/CAS1 to Bank 1           |

|        | 1 0 RAS2/CAS2 to Bank 2           |

|        | 1 1 RAS3/CAS3 to Bank 3           |

| 7/8/9  | Low. One refresh each 15.6        |

|        | microseconds, no frequency        |

|        | deviation. Optionally, bit 9 is   |

|        | tied high to give one refresh     |

|        | every 7.8 microseconds with no    |

|        | frequency deviation for some 256K |

|        | RAM devices. Jumpers are          |

|        | required as listed in Appendix B. |

| 10     | Low. Memory cycle is not          |

|        | extended.                         |

| 11     | Low. Fast (8 MHz) 80186 clock.    |

| 12     | Low. In priority contention, the  |

|        | most-recently used port is        |

| 10     | selected.                         |

| 13     | Low. Test mode is not selected.   |

| 14/15  | Low. Reserved.                    |

## **Memory Organization**

Main memory occupies the address space from %00000 through %3FFFF in the standard 256 Kbyte memory version, from %00000 through %7FFFF in the 512 Kbyte option version, and from %00000 through the lower boundary of system ROM in the 1 megabyte system. With standard 8 Kbyte ROM, this boundary is at %FE000. When changed, the new size of ROM and the number of wait states must be programmed into the UMCS register of the 80186.

Referring to Table 3-9, bits 5 and 6 of the initialization register set up the bank interleaving feature of the 8207. Interleaving overlaps the start of the next RAM access cycle with the RAM precharge period of the previous cycle. This feature optimizes memory bandwidth for the PM system.

For systems with 256 Kbytes of memory, banks 0 and 1 are selected using address line Rl to input BS0 of the 8207. For 512 Kbyte memories made up of 64 Kbyte devices, address lines Rl and Rl8 are tied to controller inputs BS0 and BS1, with all four banks of memory selected. When 256 Kbyte devices are used, only bank 0 is selected with no bank interleaving. The 1 megabyte memory uses interleaving in banks 0 and 1 with the address lines utilized as for the 256 Kbyte configuration. Physical selection of these memory configurations is accomplished with jumper options as listed in Appendix B.

Some 256 Kbyte dynamic RAM devices require a refresh every 7.8 microseconds, accomplished by setting the PD9 bit of the 8207 high as listed in Table 3-9.

## Memory Locking

)

A memory-locking feature of the 8207 prevents access to a portion of memory by either processor section. This feature may be used to allow one side to complete processing a block of data before allowing the other section to access the area. The lock feature is multiplexed between the two processor sections; when port A (80186) is selected, the lock feature originates at port A, and when port B (Z80A CPU) is selected, the lock originates at port B.

To use the lock feature, the 80186 must execute a lock prefix instruction and assert the -LOCK line to the 8207. When the Z80A asserts a lock, it writes a 1 to bit 5 of the set user ID latch on the 8-bit side, which is transferred through an address buffer to the lock input of the 8207. Refer to the schematic diagrams and to the 8-bit I/O port listing in Table 3-7. Expansion cards may use lock in a similar manner to the Z80A.

### **Z80A CPU Main Memory Mapping**

Memory mapping, using two high-speed bipolar RAM devices, is used to translate the 16-bit Z80A CPU address into a 20-bit address for main memory. The upper four address bits, on lines ZA15 through ZA12, address the mapper RAM to produce main memory upper address lines SA19 through SA12. The lower Z80A CPU address lines, ZA11 through ZA0 address main memory as SA11 through SA0. Using memory mapping, any 4 Kbyte segment of main memory can be addressed by loading the upper eight bits of its address into the mapper RAM. Using the four address bits to mapper RAM, up to sixteen such segments can be stored for mapping. For example, if the Z80A CPU wishes to address the 4 Kbyte area from %2E000 through %2EFFF of main memory, it loads the value %2E into mapper RAM. If the mapper RAM location chosen for this segment is the one addressed, the upper four address bits would be:

| ZA15 | ZA14 | ZA13 | ZA12 |

|------|------|------|------|

| 0    | 0    | 1    | 1    |

Then the Z80A CPU would produce \$3000 through \$3FFF to access \$2E000 through \$2EFFF. Any other mapper RAM location could have been chosen to map this address, with a corresponding change in the Z80A CPU address to mapper RAM.

Due to possible conflicts between 8-bit processor ROM, local memory, and mapper RAM, several cautions must be observed with mapped addresses:

- The area between %0000 and %0FFF must not be used unless the 8-bit processor ROM is mapped off.

- \* The area between %C000 and %FFFF must not be used if the local RAM consists of two 8K x 8 devices.

- \* The area between %E000 and %FFFF must not be used if the local RAM consists of one 8K x 8 device.

\* The area between %F000 and %FFFF must never be used because it is always occupied by local RAM and cannot be mapped off.

The system determines the areas of 8-bit processor ROM and local memory during power-up and reset, and automatically inhibits mapper RAM access.

Mapper RAM is located at 280A CPU I/O port %2E. Load the mapper address into bits 4 through 7 of register B of the 280A CPU, using bits 12 through 15 for the address. Next, put the map data out using register A, address %2E. Because the RAM devices invert the data, the data to be written must be in complemented form.

#### **EXPANSION CARD SLOTS**

The PM system can accommodate two 8-bit or 16-bit expansion cards in the x1 and x2 slots on the main board. The expansion cards can be intelligent or slave to the 280A microprocessor.

A slave expansion card decodes its address and responds with -XIORQ and -XRD for a read request, and -XIORQ and -XWR for a write request. Hardware timing must conform to the Z80A family timing, with an extra delay due to card buffers. If the card requires wait states, the expansion card must assert the signal -XZ WAIT. There are no provisions for slave expansion card DMA; however, an expansion card can contain its own DMA controller for independent operations. Refer to Table 3-7 for the expansion card I/O port assignments. Only intelligent cards can access main memory. The data bus for the expansion cards is either 8-bit on lines XD7 through XD0, or 16-bit on lines XD15 through XD0. To use a 16-bit data bus, the expansion card sets the XBYTE line low; the default assumes an 8-bit data bus.

If a 16-bit address is provided to main memory from an expansion card, it uses the address bus from the 8-bit processor section through its own lines XZA15 through XZA0 and the memory mapper by setting the XUSEMAP line high. If the expansion card provides a 20-bit address, it accesses main memory on lines XSA19 through XSA12, and lines XZA11 through XZA0. Use of the memory map is assumed; if the expansion card provides a 20-bit address to main memory, it must disable the map by setting its XUSEMAP signal low.

Because some data and address bus lines, and control lines -ZMREQ, -ZIORQ, -ZRD, and -ZWR, are shared by the Z80A CPU and the expansion card, the card must request the buses from the Z80A CPU before each operation. The Z80A CPU can override this request by setting bit 6 of the set user ID and miscellaneous latch low.

To use the buses, the expansion card sets its line -INT X TO Z low and waits for the -BUS AK return signal from the Z80A CPU. Expansion slot 1 has the higher priority, by virtue of its daisy-chained position. Expansion card devices do not have to be in the Z80A family, but the Z80A rules for bus request and acknowledge must be observed. An expansion card can use the lock feature of the 16-bit processor section in the same manner as the 8-bit processor section. The expansion card lock signal is -XLOCK.

Hardware Programming

# System Facilities for Expansion Cards

After power-on or reset, and its selfdiagnostics, the Z80A CPU checks bits 1 and 2 of the configure Z80A buffer to determine if expansion cards are installed (refer to Figure 3-2). These bits are generated on the expansion card, and are active low to indicate card presence. Next, the CPU reads a configuration port on the expansion card to determine the card's identification. This port is intended to be configured in a DIP switch or with jumpers, and is read as an I/O port. Bits 3 through 6 of the configure Z80A buffer are available for general purpose signals. These signals must be of the open-collector type.

Timer channels 0 and 1 of the 80186 are directly useable by the expansion cards. These channels are clocked at 1.6 MHz.

#### PARALLEL PORT

)

The parallel port has three ports for data transfer and control. Table 3-10 and Figures 3-3 and 3-4 give their addresses and bit assignments. **Table 3-10** Data Output Port (\$0020)Bit Signal Pin Num. 2 0 Data 0 3 4 1 Data 1 234567 Data 2 5 6 Data 3 Data 4 7 Data 5 8 Data 6 9 Data 7 Figure 3-3 Control Signal Input Port (\$0120)10 15 12 13 11 Pin 2 1 3 0 Bit 4 L E I - E T 0 = Printer not busy, sendI 1 1 t data L 1 = Printer busy, do not 1 I send data L 1 I 0 = Printer not on line1 1 = Printer on line 1 1 1 0 = Printer has paper L 1 1 = Printer out of paper 1 1 0 = Printer error1 1 = Printer normal L 0 = Acknowledge pulse 1 = Normal input

Figure 3-4 Output Control Port (\$0000) Pin 10 17 16 14 1 Bit 3 2 1 0 4 1 L 1 1 ł 1 0 = Normal setting  $1 = Pulse bit to \tilde{1} to$ ١ 1 send data to the I Ł printer I I 1 1 1 0 = Normal settingI 1 = Auto line feed after I I 1 carriage return ł 0 = Pulse bit must be set low for I 1 at least 50 microseconds to L L initialize the printer 1 1 1 = Normal setting 1 0 = Normal setting L 1 = Allows printer to read output 0 = Printer interrupt disabled 1 = INT1 interrupt enabled on printer acknowledge signal pulse

#### SERIAL AND SYSTEM CONSOLE PORTS

The serial port and the system console port are controlled through the DUART chip and its two independent, asynchronous channels. Channel A controls the console port, and channel B the serial port. Both ports are configured DCE and can be programmed from 50 to 9600 baud. Parity checking, character lengths of from 5 to 8 bits, and eight interrupt masking conditions are also supported.

The independent channels are programmed by initializing the appropriate channel registers. Table 3-11 lists the DUART registers and their addresses.

## Table 3-11 DUART Register Addresses

| Address         | Register                     |

|-----------------|------------------------------|

| <b>%0080</b>    | MR1A: Mode Register 1        |

| <b>%0090</b>    | MRlB: Mode Register l        |

| <b>%0080</b>    | MR2A: Mode Register 2        |

| 80090           | MR2B: Mode Register 2        |

| <b>%0082</b>    | CSRA: Clock Select Register  |

| 80092           | CSRB: Clock Select Register  |

| 80084           | CRA: Command Register        |

| 80094           | CRB: Command Register        |

| <b>%0082</b>    | SRA: Status Register         |

| <b>%0092</b>    | SRB: Status Register         |

| 8009A           | OPRC: Output Port            |

|                 | Configuration Register       |

| <b>%0088</b>    | ACR: Auxiliary Control       |

|                 | Register                     |

| <b>%0088</b>    | IPČR: Input Port Change      |

|                 | Register                     |

| 8008A           | ISR: Interrupt Status        |

|                 | Register                     |

| 8008A           | IMR: Interrupt Mask Register |

| \$008C & \$008E | CTUR/CTLR: Counter/Time      |

|                 | Register                     |

# Mode Register 1 - MRIA & MRIB

The format of the asynchronous data communications is specified through the Channel A Mode Register 1 (MRIA) for the console port and the Channel B Mode Register 1 (MRIB) for the serial port. The bit definitions for both registers are identical and are listed in Table 3-12.

| Table 3-<br>Mode Reg<br>MRlA & M     | ister l                                                              |                                                                                           |                             |

|--------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------|

| Bit                                  | <b>Assignme</b>                                                      | nt                                                                                        |                             |

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | Bits per<br>Parity t<br>Parity m<br>Parity m<br>Error mo<br>Receiver | character<br>character<br>ype select<br>ode select<br>de select<br>interrupt<br>request-t |                             |

| Bits O<br>& 1                        | in each<br>serial c                                                  |                                                                                           |                             |

|                                      | Bit O                                                                | Bit l                                                                                     | Character<br>Length         |

|                                      | 0<br>1<br>0<br>1                                                     | 0<br>0<br>1<br>1                                                                          | 5<br>6<br>7<br>8            |

| Bit 2                                | This bit<br>parity n<br>odd.                                         | designate<br>umber will                                                                   | s whether the<br>be even or |

|                                      | Bit 2                                                                | Parity N                                                                                  | lumber                      |

|                                      | 0<br>1                                                               | Even<br>Odd                                                                               |                             |

)

)

)

These bits enable the parity Bits 3 check. & 4 Bit 3 Parity Check Bit 4 0 0 Parity enabled 1 0 Force parity Parity disabled 0 1 Multiple drop 1 1 mode This bit sets the operating mode Bit 5 of the status bits to either character-by-character status or an accumulation of the status for all characters since the last reset error command (block). Bit 5 Error Mode 0 Character-by-character 1 Block Bit 6 This bit selects either the receiver ready status or the FIFO full status to be used for 80186 interrupts. Interrupt Select Bit 6 Receiver ready status 0 FIFO full status 1 This bit controls the Bit 7 deactivation of the request to send signal (RTSAN) on the OPO output to prevent an overrun in the receiver. Assignment Bit 7 0 Active RTSAN output 1 Deactivate

Hardware Programming

# Clock Select Registers - CSRA & CSRB

The DUART provides each channel with a programmable baud rate generator capable of taking the clock input and dividing it by any divisor from 1 to 65,535. The output frequency of the baud rate generator is sixteen times the baud rate. Channel A Clock Select Register (CSRA) sets the baud rate for the console port, and Channel B Clock Select Register (CSRB) sets the baud rate for the serial port.

Table 3-13 lists the bit assignments for bits 4 through 7 of the CSRA. These bits set the baud rate for the channel receiver.

Table 3-13 CSRA

)

)

|   |   |   |   | Baud             | Rates            |

|---|---|---|---|------------------|------------------|

| 7 | 6 | 5 | 4 | ACR(7) = 0       | ACR(7) = 1       |

| 0 | 0 | 0 | 0 | 50               | 75               |

| 0 | 0 | 0 | 1 | 110              | 110              |

| 0 | 0 | 1 | 0 | 134.5            | 134.5            |

| 0 | 0 | 1 | 1 | 200              | 150              |

| 0 | 1 | 0 | 0 | 300              | 300              |

| 0 | 1 | 0 | 1 | 600              | 600              |

| 0 | 1 | 1 | 0 | 1200             | 1200             |

| 0 | 1 | 1 | 1 | 1050             | 200 <b>0</b>     |

| 1 | 0 | 0 | 0 | 2400             | 2400             |

| 1 | 0 | 0 | 1 | 4800             | 4800             |

| 1 | 0 | 1 | 0 | 7200             | 1800             |

| 1 | 0 | 1 | 1 | 9600             | 9600             |

| 1 | 1 | 0 | 1 | Timer            | Timer            |

| 1 | 1 | 1 | 0 | IP <b>4-16</b> X | IP <b>4-16</b> X |

| ī | 1 | 1 | 1 | IP4-1X           | IP4-1X           |

**NOTE:** IP4 refers to a general purpose input line on the DUART.

Bit 7 of the Auxiliary Control Register selects which of the two sets of baud rates the baud rate generator is to generate.

The definitions for bits 0 through 3 of the CSRA for the channel A transmitter are identical to bits 4 through 7, with the following exceptions:

| Bi | ts |   |   | Baud       | Rates      |

|----|----|---|---|------------|------------|

| 0  | 1  | 2 | 3 | ACR(7) = 0 | ACR(7) = 1 |

| 1  | 1  | 1 | 0 | IP3-16X    | IP3-16X    |

| 1  | 1  | 1 | 1 | IP3-1X     | IP3-1X     |

The definitions of bits 4 through 7 for CSRB, which set the baud rate for the channel B receiver, are identical to the corresponding bits in the CSRA register, with the following exceptions:

| Bi | ts |   |   | Baud          | Rates      |

|----|----|---|---|---------------|------------|

| 4  | 5  | 6 | 7 | ACR(7) = 0    | ACR(7) = 1 |

| 1  | 1  | 1 | 0 | IP6-16X       | IP6-16X    |

| 1  | 1  | 1 | 1 | <b>IP6-1X</b> | IP6-1X     |

The definitions of bits 0 through 3, which set the baud rate for the channel B transmitter, are identical to bits 4 through 7, with the following exceptions:

| Bi<br>O |   | 2      | 3 |                   | Rates<br>ACR(7) = 1       |

|---------|---|--------|---|-------------------|---------------------------|

| 1<br>1  | _ | 1<br>1 | - | IP6-16X<br>IP6-1X | IP <b>6-16X</b><br>IP6-1X |

# Interrupt Status Register - ISR

This register provides the status of all potential interrupt sources. If a bit in the ISR is set at "1" and the corresponding bit in the IMR register is also a "1", the interrupt line INTRN goes low, generating an interrupt. Refer to Table 3-14 for the register bit assignments.

### Table 3-14 Interrupt Status Register

- Bit Description

- 0 The function of this bit is identical to bit 2 of the SRA register.

- 1 Channel A Receiver Receiver Ready or FIFO Full - The function of this bit is programmed by bit 6 in MRIA. If programmed as receiver ready, it indicates that a character has been received in channel B. If programmed as FIFO full, it is set when a character is transferred from the receive holding register to the receive FIFO, causing the FIFO to become full.