# TeleVideo AT Technical Reference Manual

TeleVideo Document Number 128151-00 Rev. A October 1985

TeleVideo Systems, Inc.

Please attach this label to the spine of the binder. See the illustration below for the correct location.

# Copyright

Copyright (c) 1985 by TeleVideo Systems, Inc. All rights reserved. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, without the prior written permission of TeleVideo Systems, Inc., 550 East Brokaw Road, P.O. Box 6602, San Jose, California 95150-6602.

# Disclaimer

TeleVideo Systems, Inc. makes no representations or warranties with respect to this manual. Further, TeleVideo Systems, Inc. reserves the right to make changes in the specifications of the product described within this manual at any time without notice and without obligation of TeleVideo Systems, Inc. to notify any person of such revision or changes.

#### FCC

This device is classified as either a Class A or Class B computing device. Class A devices may only be used in commercial, business, or industrial environments, whereas Class B devices have been approved by the Federal Communications Commission for use in residential areas by the general public. Check the FCC label on the bottom of your terminal to ensure that you have purchased the version appropriate for your end-use environment.

## Class B Warning

This peripheral equipment has been certified to comply with the limits for a Class B computing device, pursuant to Subpart J of Part 15 of the FCC Rules, which are designed to provide reasonable protection against interference to radio and TV reception when operated in a residential environment. The use of good shielded I/O cables is required.

WARNING! There are no user serviceable parts inside the TeleVideo AT. All service should be referred to a qualified technician. Disconnect the power cord from the unit before opening or servicing the AT.

TeleVideo is a registered trademark of TeleVideo Systems, Inc.

IBM is a registered trademark of International Business Machines Corporation.

Intel is a registered trademark of Intel Corporation

NEC is a registered trademark of Nippon Electric Corporation

**TeleVideo Systems, Inc.**, 550 East Brokaw Road, P.O. Box 6602, San Jose, California 95150-6602 408/971-0255

# TABLE OF CONTENTS

# 1 OVERVIEW

(

| Introduction | to | this Manual      | 1.1 |

|--------------|----|------------------|-----|

| Introduction | to | the TeleVideo AT | 1.2 |

# ( 2 HARDWARE FUNCTIONS - MOTHERBOARD

| Introduction                           | 2.1  |

|----------------------------------------|------|

| 80286 Central Processing Unit          | 2.3  |

| CPU Support Circuits                   | 2.5  |

| Wait-State Generation                  | 2.6  |

| 80287 Numeric Coprocessor              | 2.8  |

| System Clock and CPU Reset             | 2.8  |

| MC 146818 Real-Time Clock              | 2.9  |

| System EPROM                           | 2.9  |

| System Memory Control and Organization | 2.9  |

| System RAM                             | 2.11 |

| Memory Controller                      | 2.12 |

| Memory Refresh Controller              | 2.12 |

| Bus Arbitration                        | 2.13 |

| Parity Logic                           | 2.14 |

| 8237A Direct Memory Access (DMA)       | 2.15 |

| Controllers                            |      |

| Page Registers                         | 2.16 |

| DMA Wait-Circuit                       | 2.16 |

| Address and Data Busses                | 2.17 |

| Address and Data Buffering             | 2.17 |

| 8259 Interrupt Controllers             | 2.19 |

| 8254 Programmable Timer                | 2.20 |

| Keyboard Controller                    | 2.20 |

| RS-232C Interface Channel              | 2.21 |

| RS-232C Serial Port                    | 2.21 |

| Parallel Printer Port                  | 2.22 |

| I/O Channels                           | 2.23 |

1

# HARDWARE FUNCTIONS - DISKETTE (FLOPPY)/ FIXED (HARD) DISK CONTROLLER

3

| Introduction<br>Diskette Controller | 3.1<br>3.1 |

|-------------------------------------|------------|

| Fixed Disk (Winchester)             | 3.5        |

| Controller Interface                | 3.5        |

| Fixed Disk (Winchester) Controller  | 3.5        |

| System/Controller Interface         | 3.7        |

| <b>Operations With Dual-Port</b>    | 3.7        |

| Buffer RAM                          |            |

| Writing Disk Data                   | 3.10       |

| Reading Disk Data                   | 3.15       |

)

)

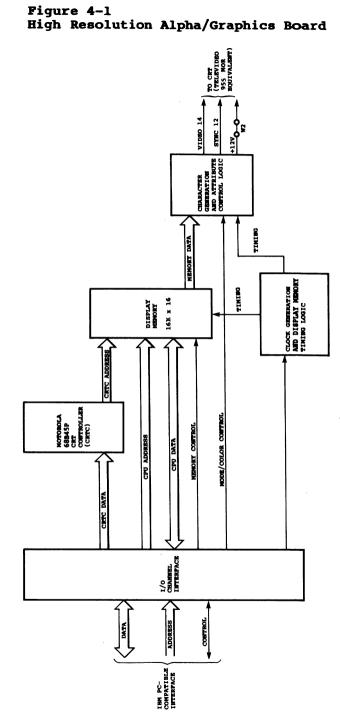

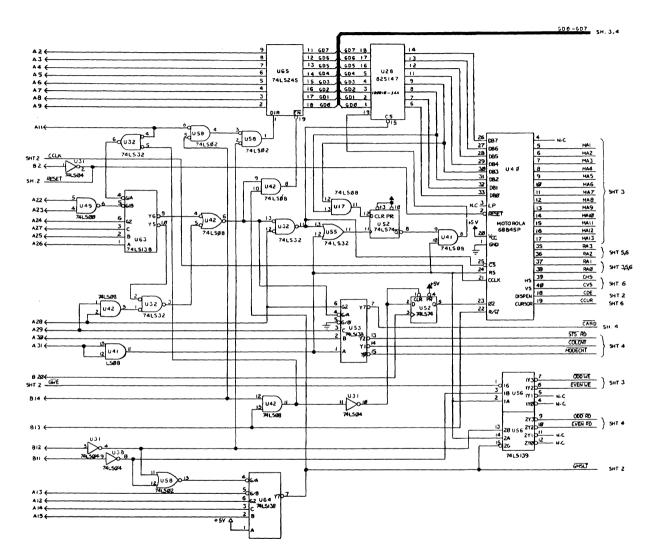

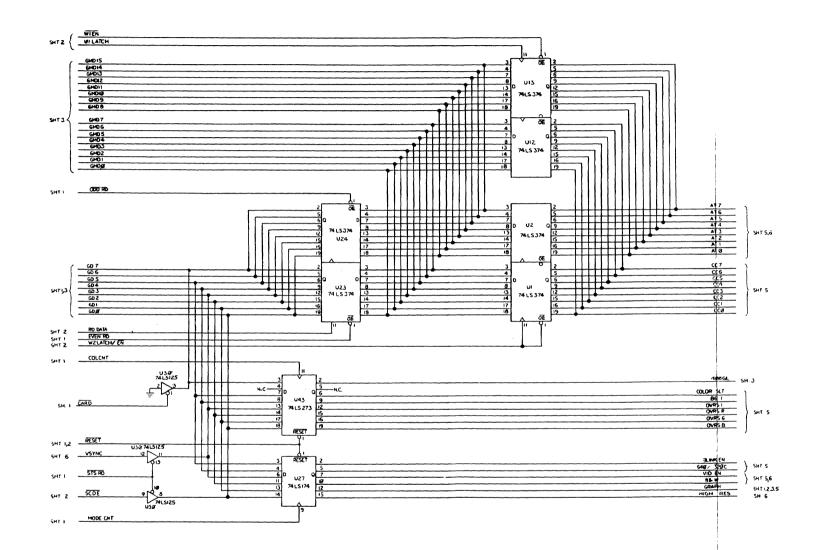

# 4 HARDWARE FUNCTIONS - HIGH-RESOLUTION ALPHA/GRAPHICS BOARD

| Introduction                          | 4.1  |

|---------------------------------------|------|

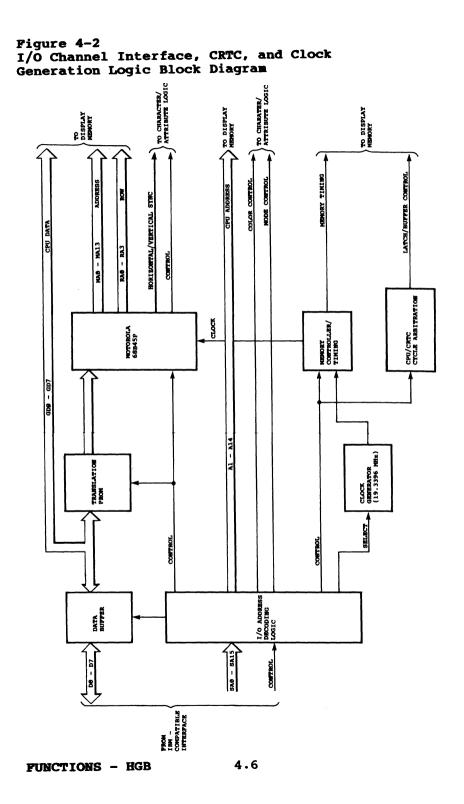

| I/O Channel Interface                 | 4.4  |

| Motorola 68B45P CRT Controller (CRTC) | 4.8  |

| Clock Generation and Display          | 4.9  |

| Memory Timing Logic                   |      |

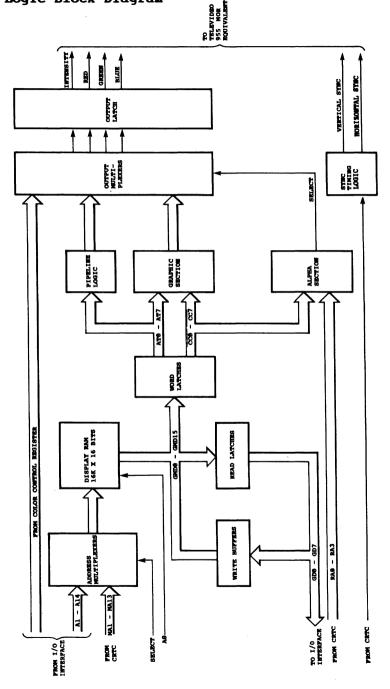

| Dual-Port Display Memory              | 4.10 |

| Character Generation and              | 4.13 |

| Attribute Control Logic               |      |

# 5 HARDWARE PROGRAMMING - MOTHERBOARD

| Introduction                      | 5.1  |

|-----------------------------------|------|

| 80286 Central Processing Unit     | 5.3  |

| Real-Address Mode                 | 5.3  |

| Protected-Address Mode            | 5.3  |

| System Performance                | 5.4  |

| 80287 Numeric Coprocessor         | 5.5  |

| MC146818 Real-Time Clock Plus RAM | 5.6  |

| Real-Time Clock Information       | 5.6  |

| RAM Configuration                 | 5.10 |

| System EPROM                      | 5.17 |

| System RAM                        | 5.17 |

| 8237A DMA Controllers             | 5.18 |

| Page Register                     | 5.19 |

| Programming 16-Bit DMA            | 5.20 |

| Channels 5, 6, and 7              |      |

| 8259A Interrupt Contollers        | 5.22 |

| 8254 Programmable Timer           | 5.23 |

# HARDWARE PROGRAMMING - MOTHERBOARD (continued)

| 8042 Keyboard Controller         | 5.23 |

|----------------------------------|------|

| Receiving Data from the Keyboard | 5.24 |

| Scan-Code Translation            | 5.24 |

| Sending Data to the Keyboard     | 5.28 |

| Inhibit Capability               | 5.28 |

| Keyboard Controller              | 5.28 |

| System Interface                 |      |

| Output Buffer                    | 5.30 |

| Input Buffer                     | 5.31 |

| Controller Ports                 | 5.34 |

| RS-232C Serial Port              | 5.34 |

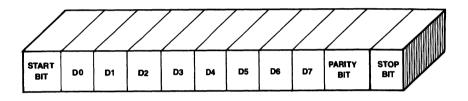

| Serial Data Structure            | 5.35 |

| Serial Port Registers            | 5.35 |

| Parallel Printer Port            | 5.36 |

| Data Latch                       | 5.36 |

| Parallel Printer Control Signals | 5.37 |

| Printer Status                   | 5.37 |

# 6 HARDWARE PROGRAMMING - DISKETTE (FLOPPY)/ FIXED (HARD) DISK CONTROLLER

| Diskette Controller                | 6.1  |

|------------------------------------|------|

| Fixed (Winchester) Disk Controller | 6.15 |

| Data Access                        | 6.16 |

| Error Register                     | 6.16 |

| Write Precomp Register             | 6.17 |

| Sector Count Register              | 6.17 |

| Sector Number Register             | 6.18 |

| Cylinder Number Low Register       | 6.18 |

| Cylinder Number High Register      | 6.18 |

| Sector/Drive/Head Register         | 6.18 |

| Status Register                    | 6.19 |

| Control Register                   | 6.20 |

| Command Register                   | 6.21 |

# 7 HARDWARE PROGRAMMING - HIGH-RESOLUTION GRAPHICS BOARD

Introduction7.1Controller Programming7.3Mode-Select Register7.4Color-Select Register7.5Status Register7.6Alphanumeric Mode7.7Graphics Mode7.8

# 8 INTERFACE

| Introduct | tion       | 8.1  |

|-----------|------------|------|

| Internal  | Interfaces | 8.1  |

| External  | Interfaces | 8.10 |

)

)

)

# APPENDICES

| Specifications                      | A.1     |  |

|-------------------------------------|---------|--|

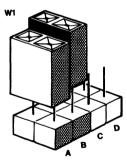

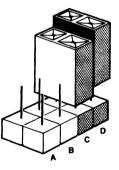

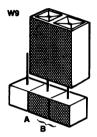

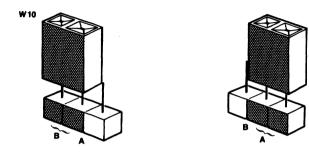

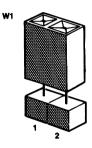

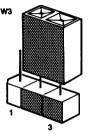

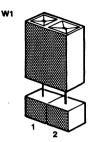

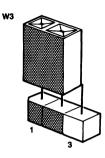

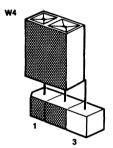

| Motherboard DIP Switch Settings (SW | W1) B.1 |  |

| Jumper Configurations               |         |  |

| Logic Diagrams                      | D.1     |  |

# FIGURES

(

(

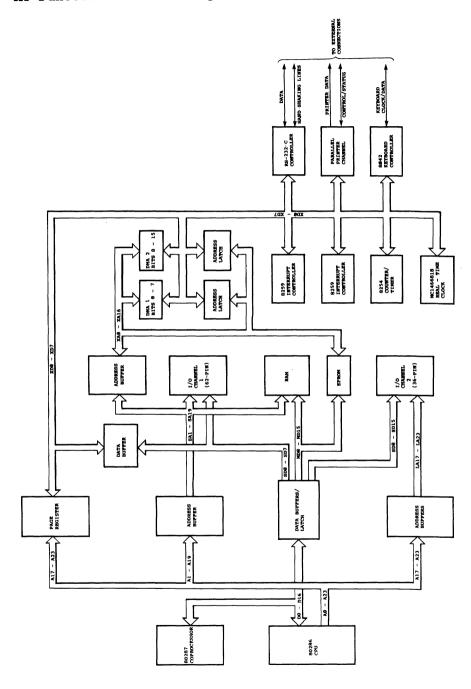

| 2-1  | AT Functional Block Diagram                                              | 2.2  |

|------|--------------------------------------------------------------------------|------|

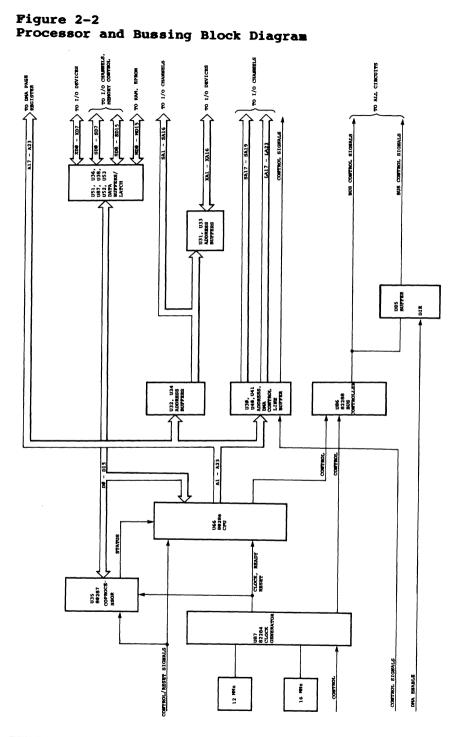

| 2-2  | Processor and Bussing Block Diagram                                      | 2.4  |

| 2-3  | System Memory and I/O Block Diagram                                      | 2.10 |

| 3-1  | Diskette Controller Circuit                                              | 3.3  |

| 3-2  | Fixed Disk (Winchester)                                                  | 3.6  |

|      | Controller Block Diagram                                                 |      |

| 3-3  | Writing Disk Data                                                        | 3.12 |

| 3-4  | Reading Disk Data                                                        | 3.16 |

|      | -                                                                        |      |

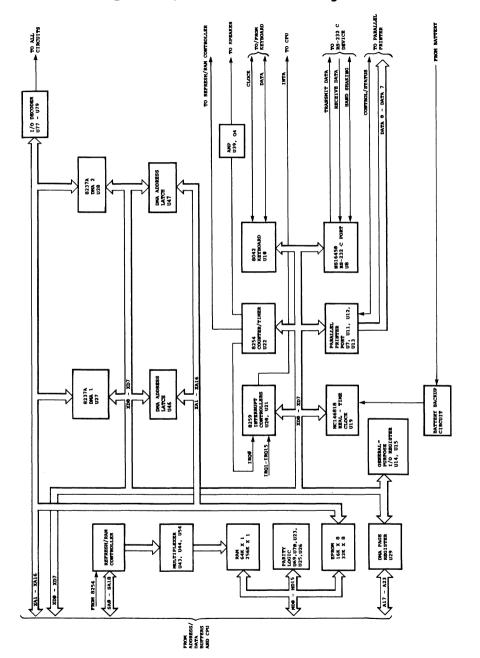

| 4-1  | High-Resolution Alpha/Graphics Board<br>Block Diagram                    | 4.3  |

| 4-2  | I/O Channel Interface, CRTC, and Clock<br>Generation Logic Block Diagram | 4.6  |

| 4-3  | Display Memory and Character/Attribute<br>Logic Block Diagram            | 4.11 |

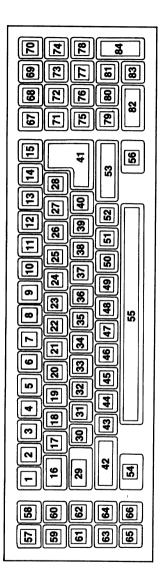

| 5-1  | Keyboard Layout                                                          | 5.25 |

| 5-2  |                                                                          | 5.35 |

|      | Transmission Structure                                                   |      |

| 7-1  | Software-Selectable Palettes                                             | 7.2  |

| 7-2  | Graphics Memory Addresses                                                | 7.9  |

| , -2 | or aphics hemory hadresses                                               |      |

# TABLES

| 3-1  | Diskette Controller Components         | 3.4  |

|------|----------------------------------------|------|

| 3-2  | Fixed Disk (Winchester)                | 3.5  |

|      | Controller Interface Components        |      |

| 3-3  | System/Controller Interface Components | 3.7  |

| 3-4  | Write From Buffer RAM                  | 3.8  |

| 3-5  | Read From Dual-Port Buffer RAM         | 3.9  |

| 3-6  | Writing From Buffer RAM                | 3.13 |

| 3-7  | Disk Data                              | 3.17 |

| 5-1  | TeleVideo AT I/O Address Summary       | 5.1  |

| 5-2  | I/O Device Reference Literature        | 5.2  |

| 5-3  | MC146818 Real-Time Clock Plus RAM      | 5.6  |

| 5-4  | Real-Time Clock Information            | 5.7  |

| 5-5  | Ram Configuration Information          | 5.10 |

| 5-6  | System Memory Map                      | 5.17 |

| 5-7  | DMA Channel Assignments                | 5.19 |

| 5-8  | 2                                      | 5.20 |

| 5-9  |                                        | 5.21 |

| 5-10 | System Interrupts                      | 5.22 |

|      | Counter/Timer Channel Assignments      | 5.23 |

|      |                                        |      |

# TABLES (continued)

| 5-12 | Keyboard Scan-Code Translation Table                          | 5.26 |

|------|---------------------------------------------------------------|------|

|      | Keyboard Controller System Interface-                         | 5.29 |

|      | Status Register                                               | 1    |

| 5-14 | Keyboard Controller System Interface-                         | 5.31 |

|      | System Commands                                               |      |

| 5-15 | Serial Port Registers                                         | 5.36 |

|      | -                                                             |      |

| 6-1  | Digital-Output Register                                       | 6.1  |

| 6-2  | DKC Status Register                                           | 6.2  |

| 6-3  | DKC Command Summary                                           | 6.2  |

| 6-4  | DKC Command Symbols                                           | 6.9  |

| 6-5  | AT Registers                                                  | 6.16 |

| 6-6  | Error Register Bit Assignments                                | 6.17 |

| 6-7  | Status Register Bit Assignments                               | 6.19 |

| 6-8  |                                                               | 6.20 |

| 6-9  | Command Register Format                                       | 6.21 |

| 6-10 | Interleaves                                                   | 6.25 |

|      |                                                               |      |

| 7-1  | CRT Controller Registers                                      | 7.3  |

| 7-2  | Mode-Select Register                                          | 7.4  |

| 7-3  | Mode-Select Register Summary                                  | 7.5  |

| 7-4  | Color-Select Register                                         | 7.5  |

| 7-5  | Status Register                                               | 7.6  |

| 7-6  |                                                               | 7.7  |

| 7-7  | Color Codes                                                   | 7.8  |

| 7-8  | Medium-Resolution Byte Usage                                  | 7.9  |

| 7-9  |                                                               | 7.10 |

|      | Selection Logic                                               |      |

|      |                                                               |      |

| 8-1  | Power Supply (Pl)                                             | 8.1  |

| 8-2  | Power Supply (P2A)                                            | 8.2  |

| 8-3  | Power Supply (P2B)                                            | 8.2  |

| 8-4  | Power Supply (P2B)<br>Power Supply (P2C)<br>Power Supply (P3) | 8.2  |

| 8-5  | Power Supply (P3)                                             | 8.2  |

| 8-6  | Power Supply (P4)                                             | 8.3  |

| 8-7  | Power Supply (DR1-DR4)                                        | 8.3  |

| 8-8  | Battery (J23 - Motherboard)                                   | 8.3  |

| 8-9  | Power Supply (PlA - Motherboard)                              | 8.4  |

|      | Power Supply (PlB - Motherboard)                              | 8.4  |

|      | Speaker (J22 - Motherboard)                                   | 8.4  |

|      | 8-Bit Expansion Board Slot                                    | 8.5  |

| 8-13 | 16-Bit Expansion Board Slot                                   | 8.6  |

|      |                                                               | 0.0  |

)

)

6

# TABLES (continued)

(

(

ĺ

| 8-14 | Diskette/Fixed Disk Controller | Board | - | 8.8  |

|------|--------------------------------|-------|---|------|

|      | Diskette Bus Connector (J1)    |       |   |      |

| 8-15 | Diskette/Fixed Disk Controller | Board | - | 8.9  |

|      | Fixed Disk Control Signal      |       |   |      |

|      | Connector (J5)                 |       |   |      |

| 8-16 | Diskette/Fixed Disk Controller | Board | - | 8.10 |

|      | Fixed Disk Data Signal         |       |   |      |

|      | Connectors (J3 and J4)         |       |   |      |

| 8-17 | Parallel Printer Port          |       |   | 8.10 |

| 8-18 | Serial Communications Port     |       |   | 8.11 |

| 8-19 | Keyboard Connector             |       |   | 8.11 |

| 8-20 | High-Resolution Graphics Board |       |   | 8.11 |

|      | Connector                      |       |   |      |

#### **1 OVERVIEW**

#### INTRODUCTION TO THIS MANUAL

The information in the <u>TeleVideo AT</u> <u>Technical</u> <u>Reference Manual</u> is intended as a hardware reference for those who service or test the AT electronics, or those who write or modify system software for use with the TeleVideo AT. This manual describes only those circuits contained on the motherboard, diskette/fixed disk controller board, and high resolution graphics board (HGB). It does not cover monitors, keyboards, disk subsystems, or other peripheral devices plugged into the I/O channel slots. Separate manuals are provided for these devices.

Overview: The overview chapter of this manual provides a general description of the TeleVideo AT.

Chapters 2 - 4: These chapters provide block-level descriptions of the logic on the motherboard, diskette/fixed disk controller board and HGB.

Chapters 5 - 7: Programming aspects of the AT are described in chapters 5 through 7. Subsections within these chapters are divided with regard to the function performed in the system. Subsections in chapters 2 through 4 parallel those in chapters 5 - 7.

Chapter 8: The "Interface" chapter details the pin-outs and signals for the internal and external connectors in the system.

These eight chapters are supported by information contained in four appendices:

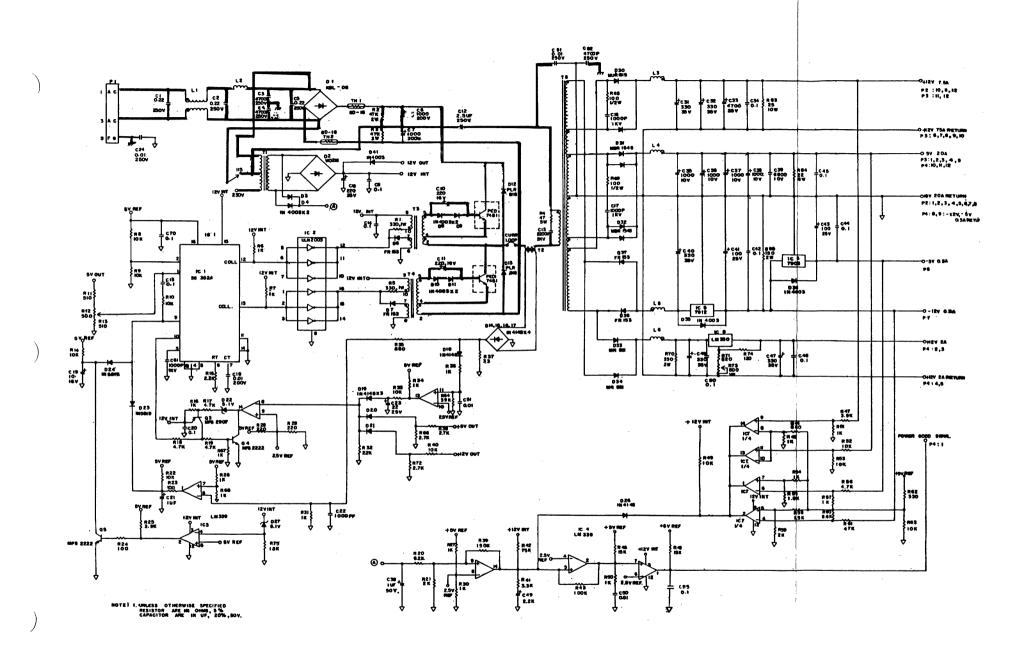

Appendix A: "Specifications" describes the electrical, physical, environmental, memory and peripheral information regarding the TeleVideo AT.

Appendix B: "DIP Switch Settings," identifies the settings for CPU speed, color/graphics or monochrome adapter, and motherboard RAM.

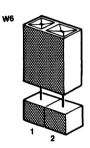

Appendix C: "Jumper Configurations," describes the jumper configurations on the motherboard for selecting I/O port addresses and on the diskette/fixed disk controller board for selecting the primary address port.

Appendix D: "Logic Diagrams," contains the logic diagrams of the motherboard, HGB, and power supply, and an assembly drawing showing component, jumper, and connector locations on the motherboard.

#### INTRODUCTION TO THE TELEVIDEO AT

The TeleVideo AT is a high-performance 16-bit computer configurable as either a single- or multiuser system, depending on the function of add-on circuit boards. The TeleVideo AT is fully hardware and software compatible with the IBM PC AT.

The basic AT system is supplied with a motherboard, 220-watt switching power supply, and eight I/O channels (hardware slots) that can accommodate a very broad range of peripherals, controllers, and communication adapters.

In addition to the motherboard described in this manual, a typical user configuration for the TeleVideo AT also includes a monochrome or color monitor, two floppy disk drives (one 48-tpi drive and one high-capacity 96-tpi drive), one hard disk drive of 20 or 44 megabyte capacity, and a detachable keyboard.

The motherboard contains a high-performance Intel 80286 CPU, an 80287 Numeric Coprocessor (optional), two 8237A DMA controllers, two 8259A interrupt controllers, a three-channel 8254 counter/timer circuit, and a Motorola MCl46818 real-time clock (with battery backup). Motherboard memory consists of 256K, 512K or 640K bytes of RAM with parity checking and up to 128K bytes of EPROM. Additional circuits on the motherboard include an 8042 keyboard controller, one RS-232C serial port, a parallel printer port, and hardware necessary for controlling the timing of these circuits, and the eight I/O channels.

#### 2 HARDWARE FUNCTIONS - MOTHERBOARD

#### INTRODUCTION

The TeleVideo AT computer is based on a 16-bit Intel 80286 CPU with a switch selectable execution speed of 6 or 8 MHz. The default execution speed is 8 MHz.

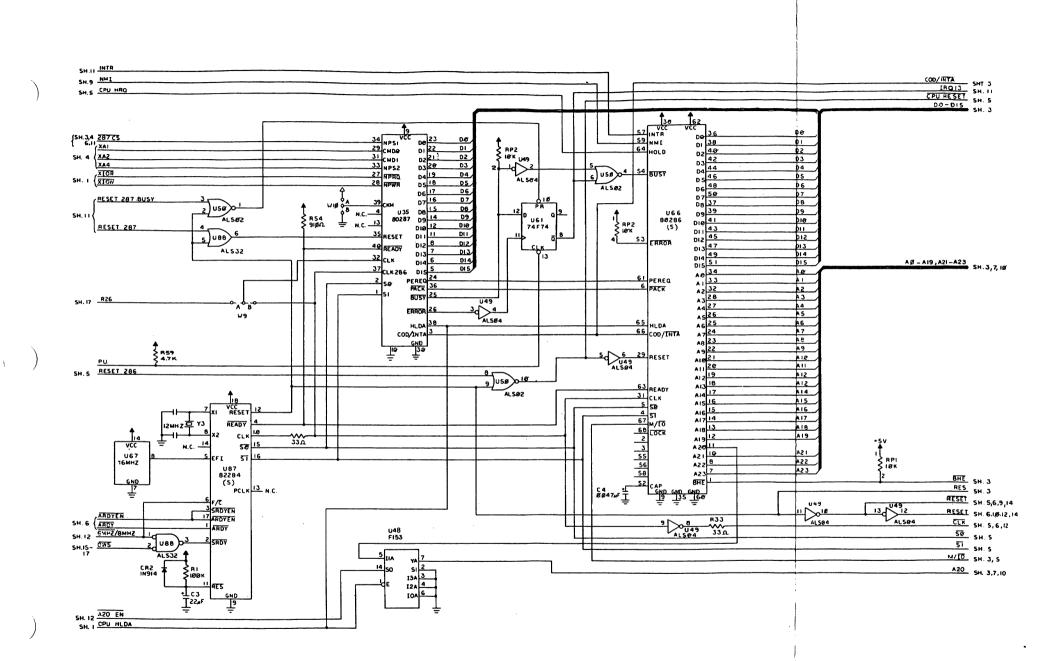

A companion numeric coprocessor circuit, the Intel 80287, can be plugged into the system motherboard to expand the architecture of the CPU to include hardware processing of floating point, extended integer, and BCD data types. Figure 2-1, TeleVideo AT Functional Block Diagram, shows the major functional blocks of the system.

)

# Figure 2-1 AT Functional Block Diagram

#### 80286 CENTRAL PROCESSING UNIT

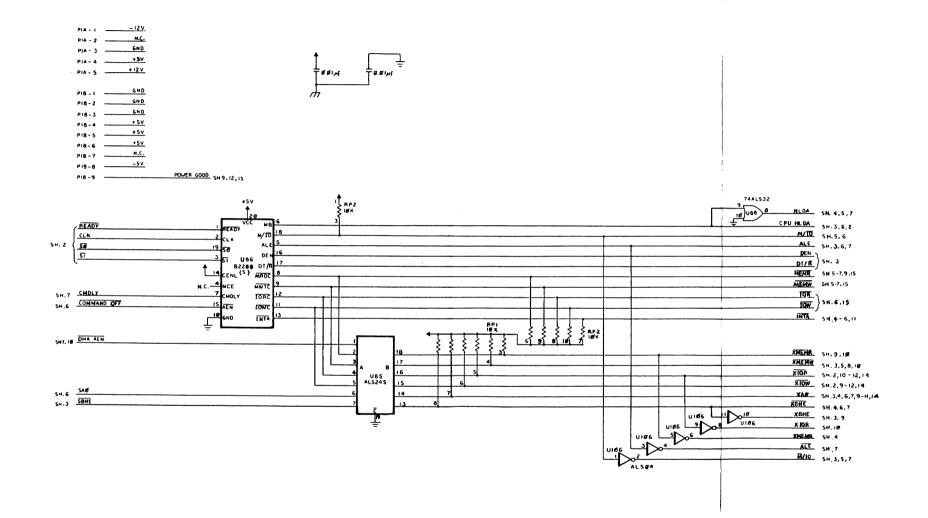

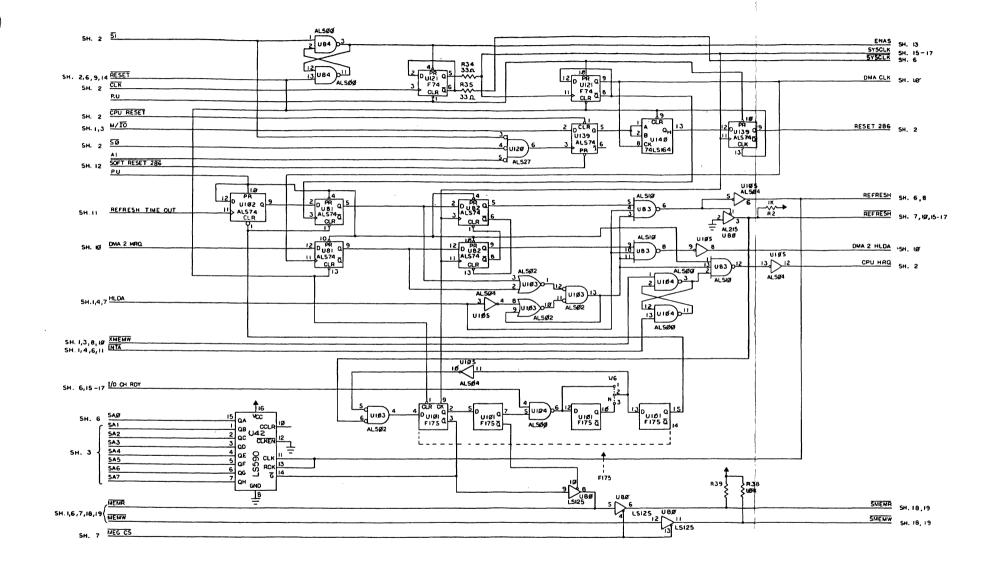

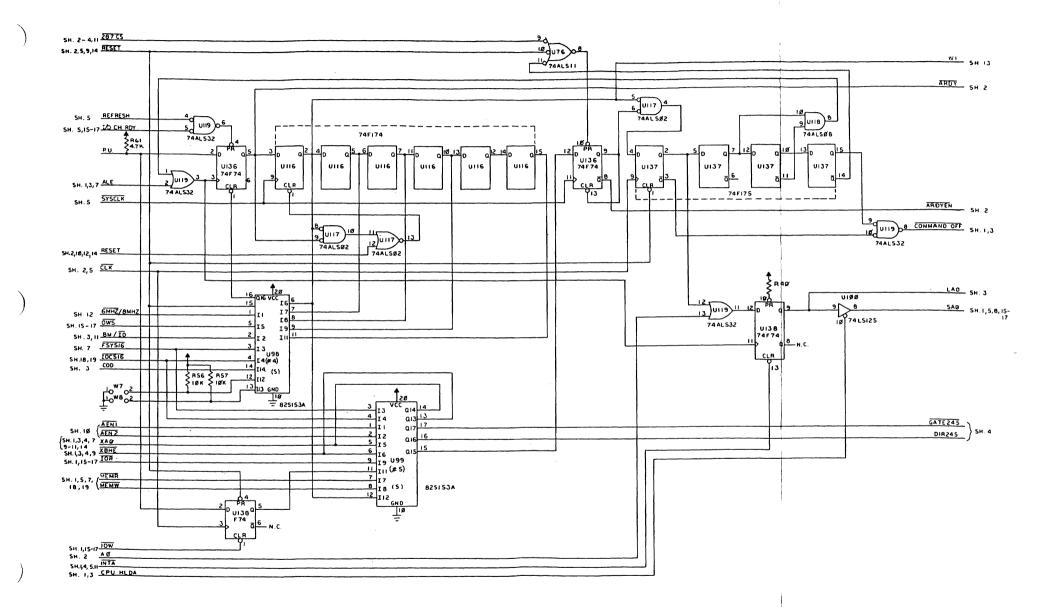

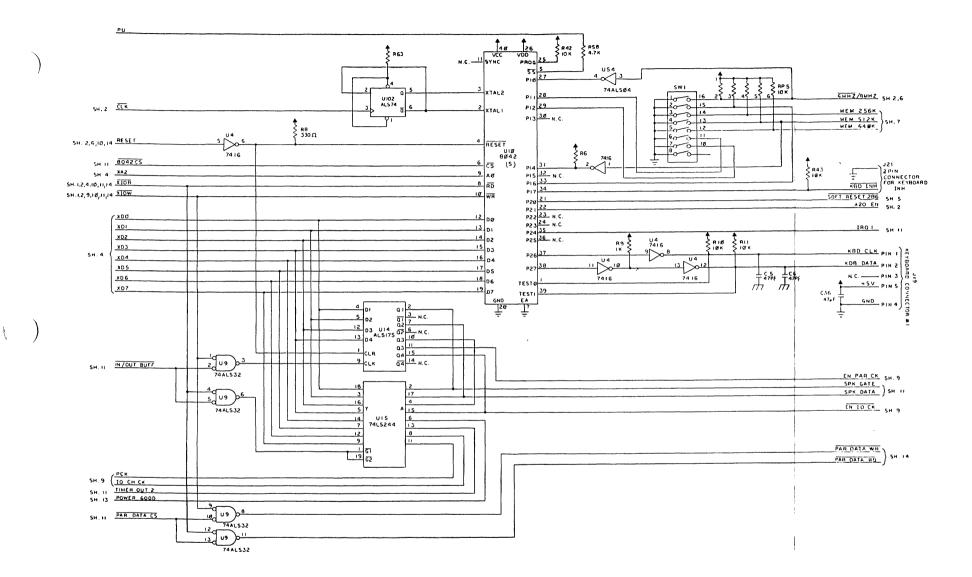

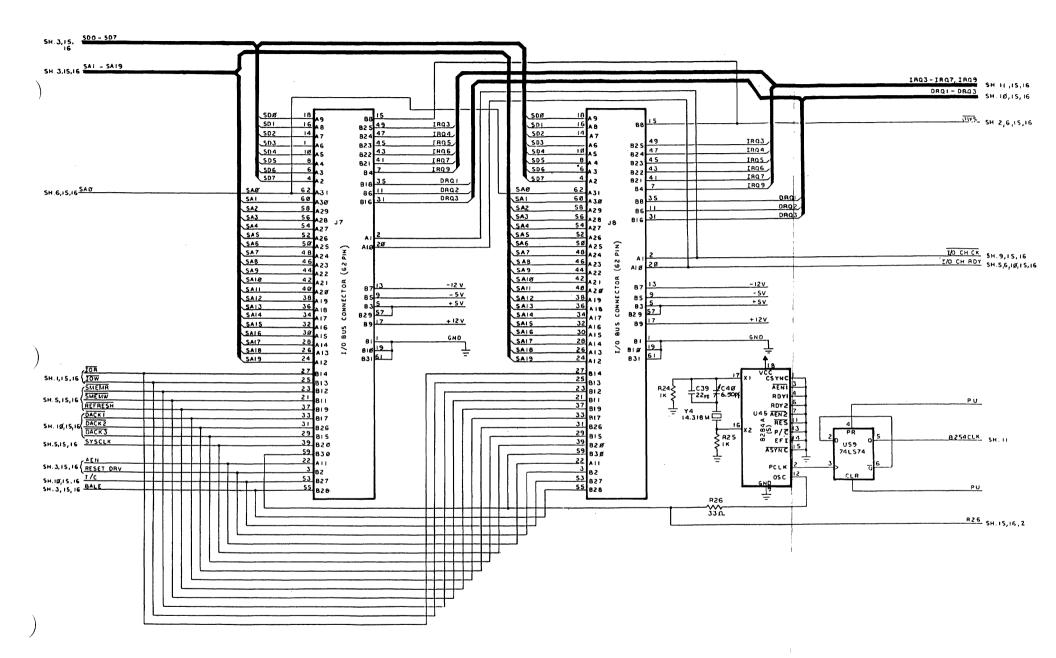

See Figure 2-2, Processor and Bussing Block Diagram, during the following discussions (note that sheet numbers refer to the TeleVideo AT Motherboard Schematic).

On the right side of Sheet 2, the Intel 80286 CPU at U66 is a high-performance microprocessor with specially optimized features useful in multi-user/ multi-tasking systems, such as the TeleVideo AT. The CPU directly addresses up to 16 megabytes of memory and 64K bytes of I/O addresses through 24 address lines AO - A23. Data is transfered between U86 and memory of I/O devices in 16-bit words or 8bit bytes through the data bus lines DO - D15.

Operational details of the 80286-family of devices used in the TeleVideo AT is given extensive attention in the <u>Microsystem Components</u> <u>Handbook</u>, published by the Intel Corporation.

FUNCTIONS - MOTHERBOARD

2.4

## **CPU Support Circuits**

The 80286 requires two support circuits to function properly in the TeleVideo AT system. First, clock, ready, and reset signals for the CPU are provided by U87, an Intel 82284 Clock Generator and Ready Interface shown on the left side of Sheet 2 of the schematics. The 82284 Clock Generator conditions (squares up) the clock, and provides reset and ready signals synchronized to the clock.

Switch 1 of SW1 (Sheet 12) controls the selection of the clock source to be sent to the CPU. When Switch 1 is open, the 6 MHz/8 MHz line to clock generator is high to enable the output of 16-MHz oscillator U67 at the 82284's EFI input to provide the clock for the CPU. The CPU internally divides the clock by two to arrive at the 8-MHz processor speed. If switch 1 is closed, the 12-MHz crystal across the X1 and X2 inputs of the clock generator provides the clock to the CPU.

The RESET output of the 82284 generates a reset signal from an RC circuit composed of Rl and C3 to provide a power-up reset to the CPU and the 80287 coprocessor.

Other reset signals from Sheet 11 of the schematics (RESET 286, RESET 287 and RESET 287 BUSY) are NORed with the power-up reset at gates U88 and U50. Two of these reset signals, RESET 286 and RESET 287, are software resets. RESET 286 is used when software must switch the CPU from its Protected mode to its Real-Address mode. RESET 287 is used by the CPU to reset the 80287 in the event of that device encountering an error in execution. The READY- output of the 82284 clock generator is low whenever the current CPU instruction cycle is complete.

J

The second supporting circuit required by the CPU is the Intel 82288 Bus Controller, shown on Sheet 1 as U86. The 82288 generates 80286 control signals for the various 8-bit I/O devices on the motherboard and 8- or 16-bit devices on the I/O channels. Control input lines to the Bus Controller include the system clock, READY- output of the 82284 clock generator, S0 and S1 control outputs of the CPU, and the COMMAND OFF- and Command Delay (CMDLY) lines from the memory controller logic.

Based on these input signals, the 82288 Bus Controller generates memory and I/O read and write signals, the Interrupt Acknowledge (INTA-) line from the CPU to an interrupting I/O device, Data Enable (DEN), Address Latch Enable (ALE), a memory or I/O selection line, and a Hold Acknowledge (HLDA) line to the DMA circuits. Buffer U85 and inverters at U106 buffer most of these lines to other circuits on the motherboard.

## Wait-State Generation

Wait-state generation circuits and the logic that controls the 8/16-bit conversion buffer U37 is on Sheet 6 of the schematics.

A wait-state causes the CPU to extend one or more clock cycles into any memory or I/O read/write cycle to accommodate I/O devices that cannot respond in the time allocated to a normal I/O or memory read/write cycle. For I/O devices or memory on the motherboard, the number of wait-states can range from one to a maximum of four, depending on the internal speed of the device.

For I/O devices or memory on the I/O channels, 6-MHz operation requires up to four wait-states for all 8-bit processing and one wait-state for 16-bit operations; 8-MHz operation requires up to six wait-states for 8-bit processes, one wait-state for 16-bit memory processes and two wait-states for 16bit I/O operations.

)

All devices may request as many wait-states as required for reliable operation of the device. Note that too many wait-states will effect the operation of the memory refresh generation logic. The wait-state generation circuits consist of ten flip-flops clocked by SYSCLK- and controlled by a custom circuit at U98. Certain conditions, such as a request for zero wait-states from hardware on the I/O channels (OWS), the 6-MHz/8-MHz CPU clock setting, and the memory or I/O (M/IO) selector determine the output of U98, which in turn, determines the number of wait-states generated at the COMMAND OFF- output of the circuit.

During a normal 8-bit I/O cycle, four wait-states are generated. This is in addition to two waitstates the CPU adds during execution of an I/O cycle. This wait timing of almost 1.0 microsecond (actually 996 nanoseconds) makes the I/O cycle timing compatible with the earlier 8088-based PCtype machines. For 16-bit I/O operations, the total wait timing is about 500 nanoseconds. System memory requires one wait-state; faster memory hardware on the I/O channels can request that no wait-states be inserted in the cycle.

On the bottom of Sheet 6 is the control logic for buffer U37. As stated above, this buffer controls the conversion between 16-bit I/O devices in the system and 8-bit I/O devices. The control logic generates two signals, GATE245- and DIR245 from the outputs of a custom circuit at U99. This custom circuit uses the MEMR- and MEMW- to select the direction of data flow in the buffer; XAO, AEN1-, AEN2-, XBHE-, and IOR-, in conjunction with FSYS16and IOCS16-, determine when the buffer is gated. FSYS16- and IOCS16- come from the I/O channels to indicate that an addressed memory or I/O device on the I/O channel is capable of word length data transfers.

On Sheet 11 three I/O decoders at U77, U78, and U79 decode many of the I/O addresses, that is, chip selects and control signals, used by the system's devices. The decoders are addressed using the XAO - XA9 address lines and the XIOR- and XIOW- read and write strobes.

#### 80287 NUMERIC COPROCESSOR

On Sheet 2 of the schematic, the Intel 80287 numeric coprocessor at U35 is upward-compatible with the Intel 8087 coprocessor used in PC-type systems. The numeric coprocessor operates in parallel with the CPU to provide hardware processing of floating point, extended integer, and BCD data types. Using the 80287 to process these operations in hardware is much faster than using the 80286 CPU to implement an equivalent function in software. While the 80287 receives the same 12-MHz or 16-MHz clock output of the 82284 clock generator, it internally divides the clock by three to operate at either 4.00 or 5.33 MHz.

The CPU regards the 80287 coprocessor almost like any other I/O device, such as the DMA or interrupt controller, in the sense that IOW- and IOR- control signals are used for communication. U35 is connected to the data bus through DO - D15. If the coprocessor encounters an error in the execution of an instruction, flip-flop U61 generates interrupt request (IRQ13) to the interrupt controller U21. The CPU then interrogates the interrupt controller, services the interrupt, and resets the flip-flop using the RESET 287 BUSY line.

#### SYSTEM CLOCK AND CPU RESET

The circuitry on the top half of Sheet 5, composed of gates in U84 and a flip-flop at U121, generates the 6-MHz or 8-MHz system clock for the eight I/O channels and some circuits on the motherboard. Another flip-flop at U121 generates a 3-MHz or 4-MHz clock for the DMA controller. Both clocks are synchronized to the clock derived from the CLK output of the 82284 clock generator and used internally by the CPU.

Finally, a gate at Ul20, and flip-flops at Ul39 and Ul40 generate RESET 286. RESET 286 is a stretched pulse required by the CPU and generated when 1) the logic detects that the CPU is in a shut down condition as indicated by the state of the S0 and S1 lines from the CPU, or 2) a software reset changes the CPU from the protected-address mode to the real-address mode.

)

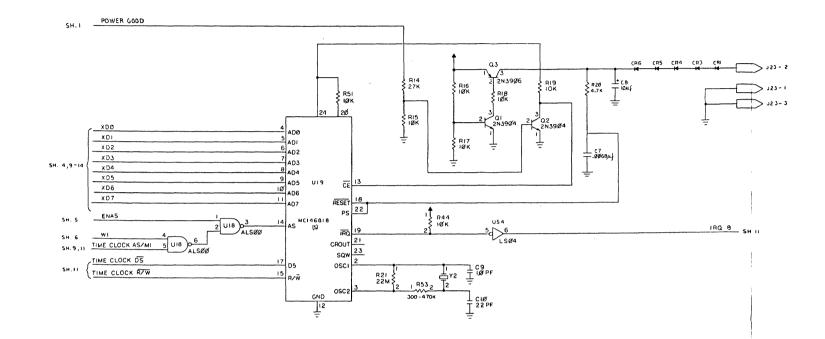

#### MC 146818 REAL-TIME CLOCK

On Sheet 13, the Motorola real-time clock at U19 serves two functions in the TeleVideo AT. First. it supplies time and date information to the CPU. Secondly, the real-time clock contains 50 bytes of RAM used by the system to store system configuration. Data to or from the real-time clock . is transferred on the XDO - XD7 data lines and controlled using several I/O signals decoded by decoder U78 (Sheet 11). The time base is supplied by a 32.768-KHz crystal at Y2. The time, date, and memory are retained by a lithium battery backup circuit made up of transistors Q1, Q2, and Q3 and a 6.0-volt lithium cell at connector J23. When the system is off, that is, once the +5-volt power in the system drops below 3.5 volts, the battery backup circuit allows current from the battery to flow to the clock. Otherwise, the battery is not used. The battery itself has a shelf life of over five years and can supply continuous current to U19 for about 1.5 years. The battery is replaceable.

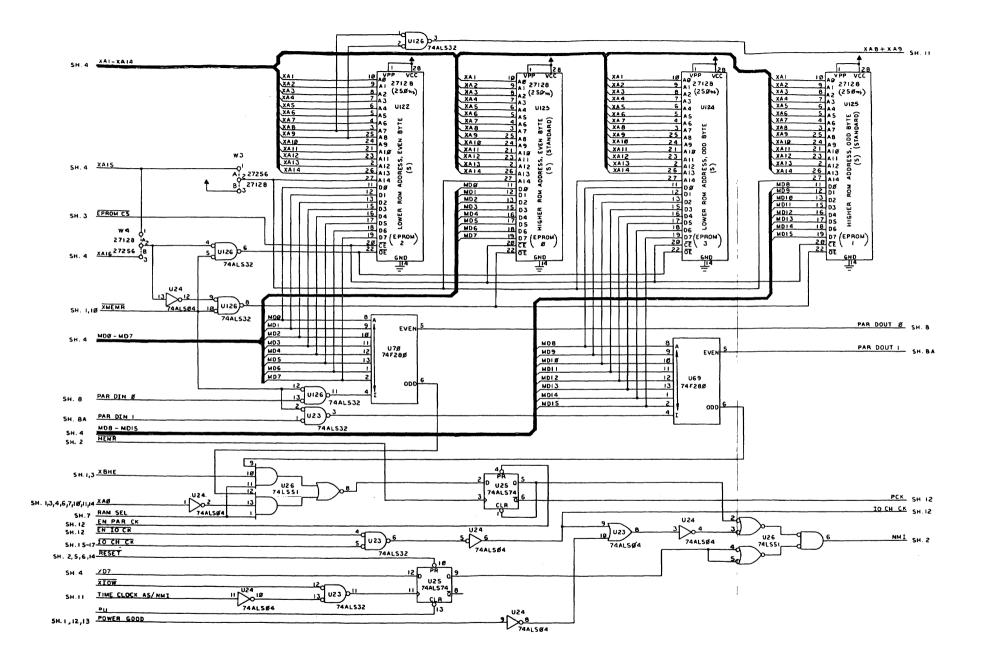

#### SYSTEM EPROM

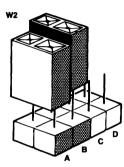

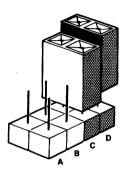

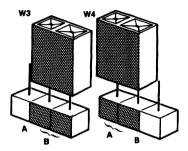

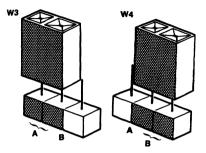

On the top half of schematic Sheet 9, four EPROMs can be accommodated. There can be two types: 16Kx8-bit (27128) or 32Kx8 (27256). Jumpers W3 and W4 select XA15 and XA16 address line assignments for each type. The EPROMs operate in parallel using the XA1 - XA16 lines for address and the MDO - MD7 lines for data. The Chip Enable (CE) input for the EPROMs occurs through the EPROM CS- line from address latch U41 (Sheet 3). All four EPROMs are enabled at the same time; however the Output Enable (OE) input for each EPROM is unique as gated by U126 and inverter U24.

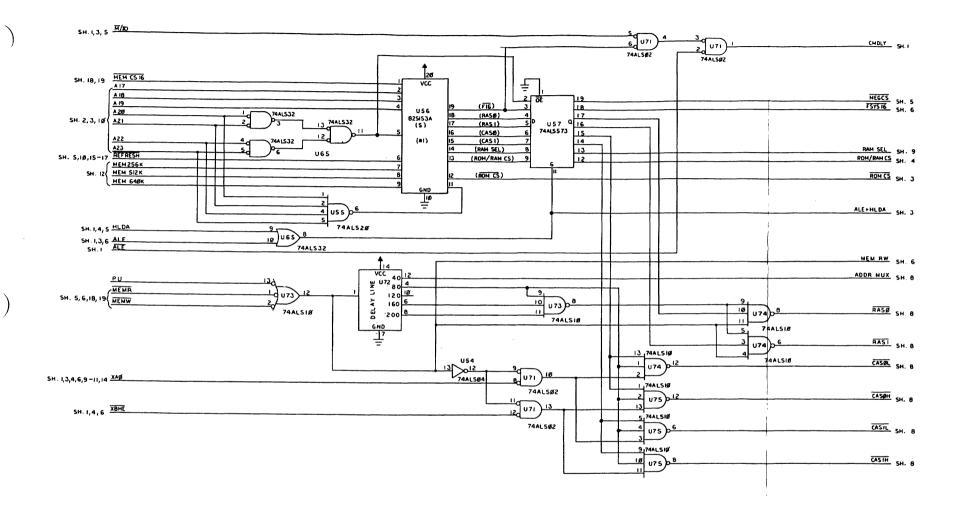

## SYSTEM MEMORY CONTROL AND ORGANIZATION

See Figure 2-3, System Memory and I/O Device Block Diagram, during the following discussions. The system memory control circuits operate to refresh the complement of dynamic RAMs in the system. The circuits also generate the proper timing for access of memory locations by the CPU or DMA controllers. Figure 2-3 System Memory and I/O Device Block Diagram

)

)

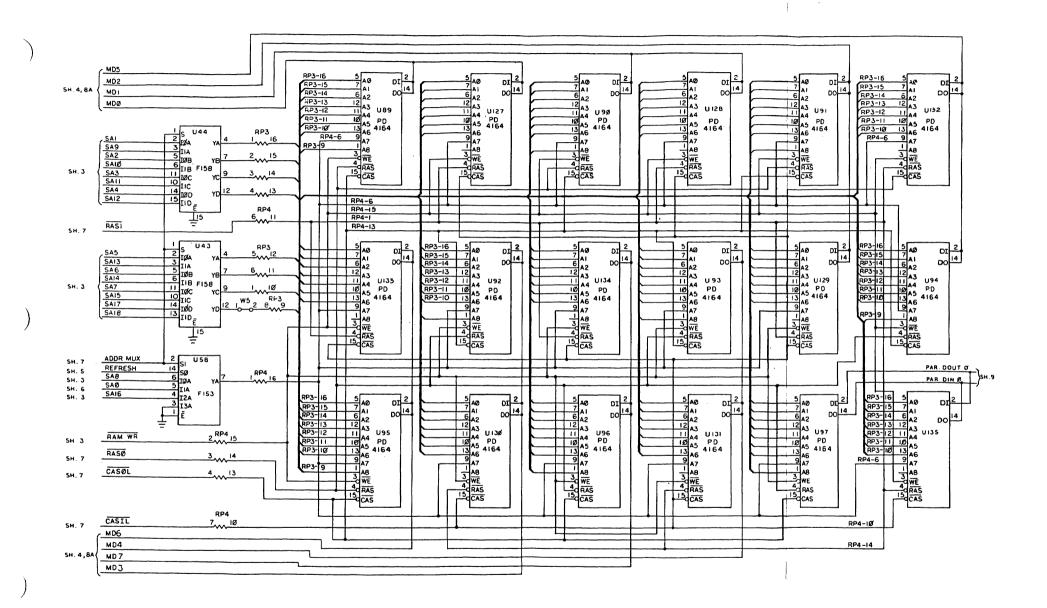

#### SYSTEM RAM

1

Motherboard memory may be composed three ways:

- 1.

- 256 Kbytes using 36 64 x 1 RAM chips 512 Kbytes using 18 256 x 1 RAM chips 2.

- 3. 640 Koytes using 18 256 x 1 RAM chips

and 18 - 64 K X 1 RAM chips.

External RAM can be added by expansion cards on the I/O channels to bring the total RAM complement to 15 megabytes. The dynamic RAMs are refreshed by a separate memory refresh controller, unlike the previous PC-type systems, which use DMA to provide refresh. Up to four 16 Kbyte or 32 Kbyte EPROMs can be installed in the TeleVideo AT.

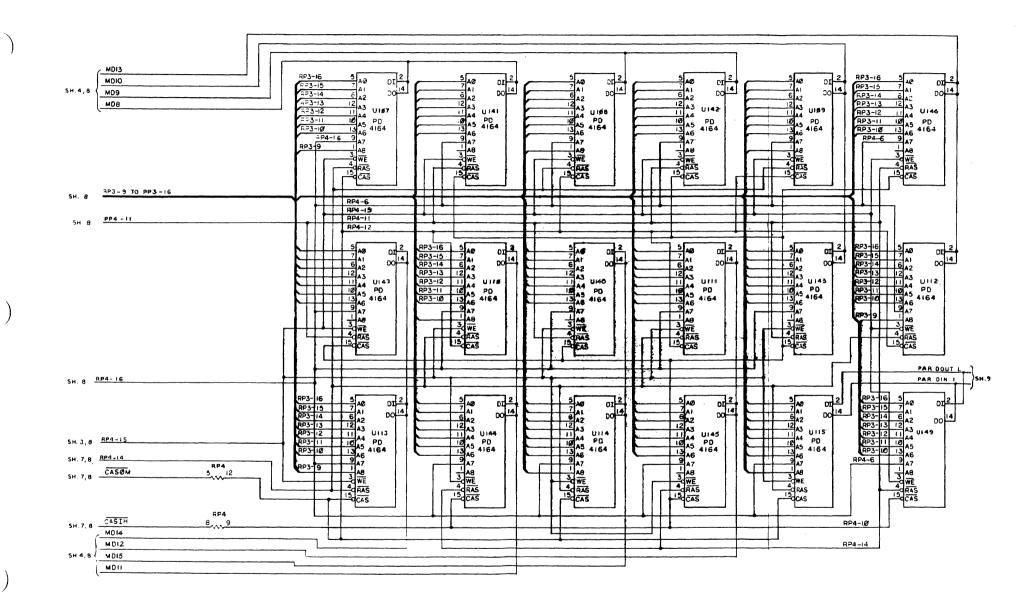

On Sheets 8 and 8A, two banks of RAM are present in the system. Each bank consists of a high and low byte. Nine RAMs per byte are required: one for each data bit plus one for a parity bit. The respective row and column address signals, RASO, RAS1, CASOL, CASOH, CASIL, and CASIH are sent to their respective banks and bytes. Address lines SAO - SA18 are sent to multiplexers U43, U44, and U58 to specify the row and column addresses of the memory location. ADDR MUX is delayed 40 nanoseconds from the memory read or write strobe by U72.

Data to and from the RAMs is transferred over the MDO - MD15 memory data lines to buffers U52 and U53 as discussed above. When data is written into the RAMs. RAM WR- from U40 is active during the time that data is on the memory data lines.

#### Memory Controller

The memory controller on schematice Sheet 7 generates control signals necessary to access the locations in memory. U56 is a custom memory decoder that generates row and column address strobes, and RAM and ROM selection lines. Inputs to this decoder are address lines Al7 - A23, MEM CS 16- from the I/O channels to indicate a word operation, REFRESH- from the refresh controller to indicate that a refresh cycle is active, and three lines from switches at SW1 (Sheet 12) indicating how much memory is in the system.

During a memory read or write cycle, the outputs of U56 are latched at U57 by ALE. The RAS and CAS signals are sent to gates at U74 and U75 to generate the row and column address strobes while the RAM and ROM selection lines are sent to enable their respective devices. The MEMR- or MEMWstrobes are also delayed by delay line U72 to stagger the generation of the RAS and CAS signals. CMDLY is sent to the 82288 Bus Controller during I/O operations only to delay generation of the I/Oread or write strobes. The RAMs receive their address in a multiplexed fashion; one of 256 row address is applied to the address inputs of the RAM while RAS- is active. Next, one of 256 columns is specified at the address inputs while CAS- is active.

)

## Memory Refresh Controller

Dynamic RAMs must be refreshed at certain intervals order to retain their data. Refreshing is accomplished by, one at a time, strobing all 128 or 256 row (128 refresh cycle or 256 refresh cycle) addresses of the RAM array. A normal memory access by the CPU or DMA controllers requires that a row address and a column address be used to specify a valid address.

The TeleVideo AT can use two types of RAM: either 64Kx1-bit or 256Kx1-bit RAMs. The "128 refresh cycle" RAMs must have all their row address lines strobed (refreshed) within 2 milliseconds if they are to retain their data; "256 refresh cycle" RAMs allow 4 milliseconds for a complete refresh. Memory refresh controller logic also arbitrates requests to access the memory by the refresh controller and DMA controllers during a CPU cycle. The circuitry to generate refresh signals for memory is located on the bottom half of Sheet 5.

Two signals are necessary to refresh a row of memory: a refresh address and a memory read signal. The refresh address must be incremented from 0 to 255 to refresh all of the rows of memory in the system. Every 15 microseconds, Counter Channel 1 of U22 times out to generate REFRESH TIME OUT, which starts the refresh access. Counter U42 (LS590) generates the refresh addresses on the SA0 - SA7 system address lines. The counter is clocked from the REFRESH line from pin 6 of U105 to increment the address on its outputs. The pin 3 Qoutput of U107 gates the address to the counter's outputs. When the refresh address is incremented, U107 also forces a memory read signal as System Memory Read (SMEMR-).

#### **Bus Arbitration**

During the time that a row of RAM is being refreshed, the refresh controller places the CPU in a hold state so that it does not try to generate a memory address. When REFRESH TIME OUT occurs and no DMA request is pending on the DMA 2 HRQ line, the refresh controller generates CPU HRQ. When the CPU acknowledges that it is holding (HLDA), the refresh controller gets control of the address bus and generates REFRESH. After a row of RAM has been refreshed, the refresh controller removes the hold request and hands control of the address bus back to the CPU.

Similarly, since the refresh controller is also competing with the DMA controllers for access to the memory, DMA operations must wait until a row of RAM has been refreshed. If the DMA controllers request the address bus while DMA 2 HRQ and REFRESH TIME OUT are active, the arbitration logic ensures that DMA will not be granted its request until a row of memory has been refreshed. Otherwise, the DMA controller will be allowed to take control of the address bus.

## Parity Logic

The parity logic is composed of parity generators U69 and U70, and several gates and flip-flops at U23 through U26. The parity generators operate by examining the bit pattern of a data byte as it is written into a location in RAM on the MD0 - MD7 memory data lines.

For example, assuming that an even parity is desired, if the bit pattern written into the RAM location contains an odd number of 1 bits, e.g., 00100011, the parity generator for that bank of RAM (either U69 for bank 1 or U70 for bank 0) stores a 1 by generating a 1 on its EVEN output. The EVEN outputs of U70 and U69 are stored in the RAM as PAR DOUT 0 and PAR DOUT 1. The resulting nine bits stored in RAM then contain an even number of 1s or 00100011(1). When the same RAM location is read back at a later time, the bit from the parity RAM (PAR DIN 0 or PAR DIN 1) is also read.

As long as the parity generator still sees an odd number of 1 bits in the data byte and a 1 in the parity bit, the parity generator will assert its EVEN output (note that since a memory-read operation is taking place, the EVEN output of the parity generator is not stored in the parity RAM; it is just thrown away). If the data bits plus the parity bit do not contain an even number of 1s the ODD output of the parity generator goes high.

The ODD outputs of the parity generators are sent to logic that generates a non-maskable interrupt (NMI) to the CPU. The odd parity bit that caused the error is latched into U25. The Q output of U25 is sent to other gates that generate the NMI input to the CPU. The Q- output is sent to buffer U15 on Sheet 12 as a parity check signal (PCK on Sheet 12) where it is transferred to the XD7 data line to the CPU. When the CPU receives a NMI, it immediately goes to a software routine that tries to identify which RAM location generated the parity error. An NMI can also be generated by expansion memory hardware on an I/O channel by asserting an I/O channel memory check (IO CM CK-).

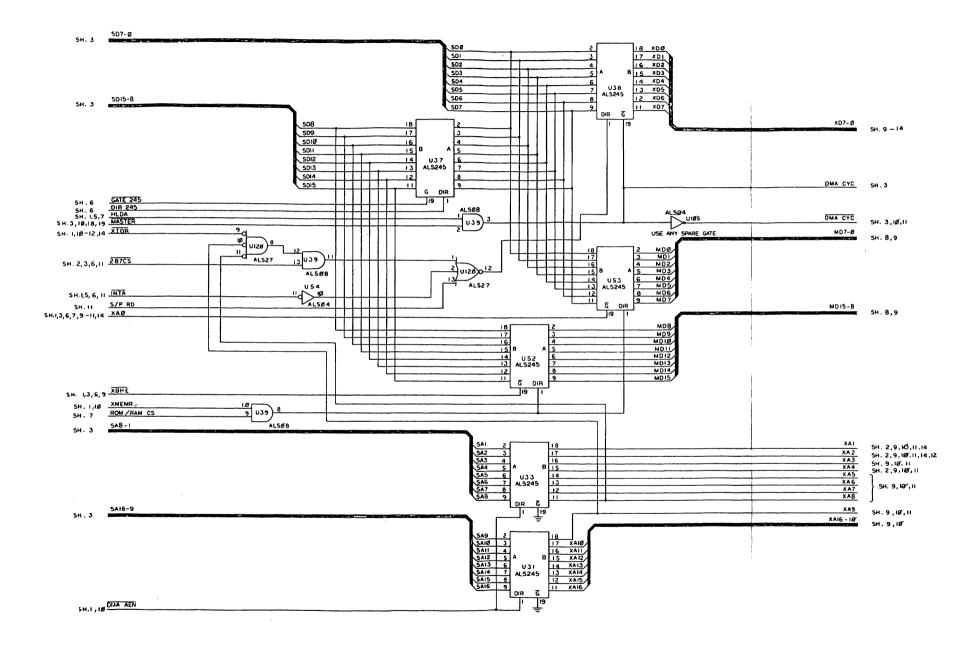

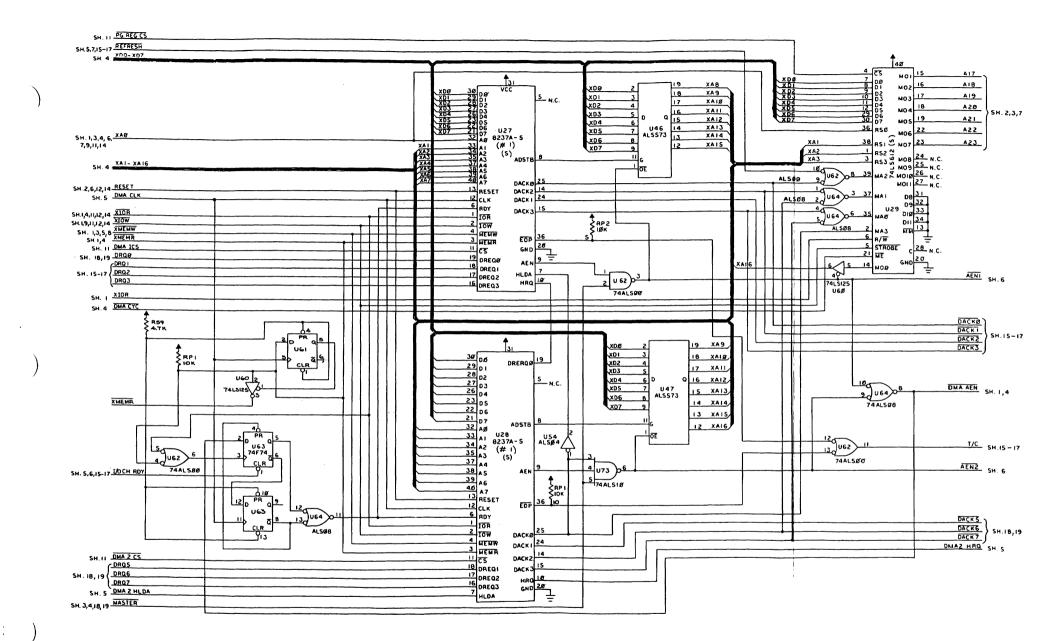

# 8237A DIRECT MEMORY ACCESS (DMA) CONTROLLERS

Direct Memory Access (DMA) of RAM by external devices, such as a disk drive, is provided by a pair of Intel 8237A DMA controllers operating at 3 MHz or 4 MHz. DMA minimizes the time that the CPU must wait for these other I/O devices requiring service. For example, when the CPU wants to read from a diskette, it programs the DMA controller with the number of bytes to be transferred and a memory address at which to start the transfer. The CPU can then return to another task in the system while the DMA controller waits for the data from the disk controller to arrive.

On Sheet 10 of the schematic, two Intel 8237A 8-bit DMA controllers are used in the TeleVideo AT. Operational details of the DMA controllers are given in the <u>Microsystem Components</u> <u>Handbook</u>, published by the Intel Corporation.

Byte data transfer is accomplished by DMA Controller 1 (U27). Word data transfer is accomplished by DMA Controller 2 (U28) working with DMA Controller 1. Controller 2 is not used during byte operations. To operate, the DMA controllers must have control of the address, data and control busses in the system. When an I/O device requests DMA service by asserting its DRQx line, the DMA controller tries to get control of the busses by asserting DMA2 HRQ. This signal is sent to the memory refresh generation logic, which grants the request if a memory refresh cycle is not in progress. If a refresh cycle is in progress, the DMA controller will wait. If the refresh cycle is not active, the DMA will take control of the busses.

The DMA controller then asserts a DMA acknowledge (DACK) to the requesting I/O device to indicate that it has been granted a DMA cycle. When the DMA operation is finished, the DMA controller removes its DMA 2 HRQ and the CPU or memory refresh controller resumes control of the busses. The DMA controllers can address up to 64 Kbytes of memory using 16 address lines. The data lines, shown on the device as DO - D7, are multiplexed to provide the upper eight bits of the address. Address latches U46 and U47 hold the upper eight bits of the memory address while address lines AO -A7 hold the lower eight bits. The address strobe signals (ADSTB) from controller 1 and controller 2 are used to gate the address latches.

In word operations, data transfers always take place on even-byte boundaries, that is, the leastsignificant bit of the address is always zero. Therefore, controller 2 outputs its address on the Al - Al6 address lines, while controller 1 uses the AO - Al5 address lines. The DO - D7 lines are then used to transfer the data to or from the requesting I/O device.

## Page Registers

DMA controller 1 can transfer 64 Kbyte blocks of data to a total of 256 blocks (or pages). Using DMA Controller 2, 128 Kbyte blocks (64K words) can be transferred to a total of 128 byte blocks of memory during each DMA operation.

Using the first DMA Controller, the page register at U29 specifies one of 256 pages of memory in the system where the transfer will occur. Using the second DMA, the page register specifies one of 128 pages of memory. The CPU loads U29 with the page number on the XDO - XD7 data lines. When the first DMA has control of the address bus, the page register supplies the page address on the Al6 - A23 address lines. When using the second DMA controller, the page address is supplied on the Al7 - A23 address lines.

# DMA Wait-Circuit

Some slower I/O devices require extra time between DMA cycles. A flip-flop at U63 provides a waitcircuit between DMA cycles. The ready (RDY) input to the DMA will go high when the I/O device is ready for the next cycle.

#### ADDRESS AND DATA BUSSES

A 24-bit address bus and an 8/16-bit data bus allow the CPU to communicate with memory, peripheral devices, and its I/O channels, which support up to eight circuit boards plugged into connectors on the motherboard. Since a 24-bit address bus is used, up to 16 megabytes of RAM and ROM can be addressed. Furthermore, the CPU can access bytes (eight bits) or words (sixteen bits) depending on the mode selected by software.

To maintain compatibility with the earlier 8088based PC-type machines, much of the peripheral hardware, such as interrupt controllers, DMA controllers, and serial and parallel printer ports, are eight-bit devices. That is, data transfers between these I/O devices and the CPU occur only in bytes, not full sixteen-bit words. Also, memory locations can be addressed in either bytes or words. An extensive address and data buffering scheme ensures this compatibility with the PC-type machines.

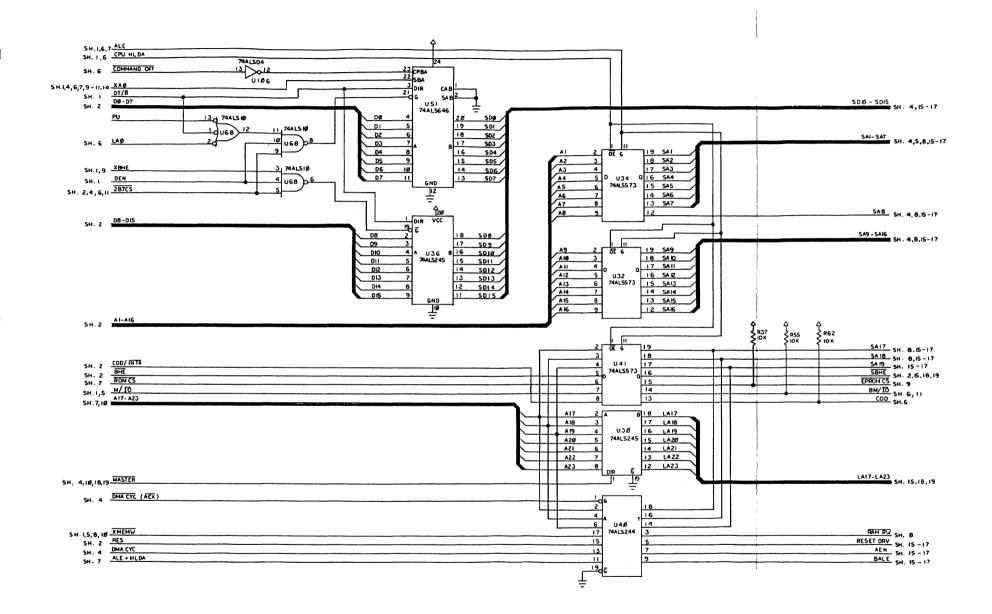

#### Address and Data Buffering

The address bussing scheme consists of address latches and buffers that allow the CPU and DMA controllers to provide addresses for memory and I/O devices on the motherboard and I/O channels. On Sheet 3, address lines Al - Al9 are latched by U41, U32, and U34 as the System Address lines for use by system memory and I/O devices. U41 also latches several control signals relevant to operation of certain system components.

Unlatched, buffered address lines A17 - A23 are also made available to the I/O channels for hardware requiring them as LA17 - LA23. After latching, the SA1 - SA15 data lines are sent to two bidirectional buffers U31 and U33 on Sheet 4, which provide the XA1 - XA16 address lines to the I/O devices on the motherboard. When DMA is active, the direction of data flow reverses. Also concerning DMA operations, U40 buffers address lines A17 - A19 and four control signals. Data buffers U51 and U36 buffer data between the CPU, memory and I/O devices. U51 handles data bits D0 - D7 and is a combination latch and buffer. The CPU is capable of either byte or word operations using 8-bit I/O devices. When the CPU wants to read a word (16 bits) from an 8-bit device, the control logic on the motherboard will generate two read cycles.

The first cycle reads the 8-bit device and latches the lower byte of data on U51. During the second cycle, the CPU reads eight more bits (the high byte) from the device and buffers them through U36. At that time, the CPU reads both bytes on its D0 -D15 data line. The same process works in reverse when the CPU writes 16 bits of data to an 8-bit I/O device. For 16-bit I/O devices or memory, the lower byte of data is not latched; data is simply transferred between D0 - D15 and SD0 - SD15.

The SDO - SD15 data lines are sent to two pairs of bidirectional buffers on Sheet 4, U53 and U38, and U52 and U37. For memory addresses, buffer pair U53 and U52 buffers SDO - SD15 to or from the memory as MDO - MD15 depending on the state of their DIR inputs. For I/O devices in the system, buffer pair U38 and U37 buffers the SDO - SD15.

For example, if the CPU is reading 16 bits of data from an I/O device, the lower byte appears at the inputs of U38 on the XDO - XD7 data lines. The buffer is gated to place the byte on the SDO - SD7 lines to latch/buffer U51. The high byte then appears on the XDO - XD7 data lines and is sent through U38 to U37. U37 sends the data to the SD8 SD8 - SD15 data lines to U36.

When the CPU writes data to an I/O device, the process is reversed. Control of buffer U38's DIR and G- inputs is performed by gates in U39 and U120. For external 16-bit I/O devices connected to the eight I/O channels, the SD8 - SD15 lines go directly to the 36-pin I/O channel connectors.

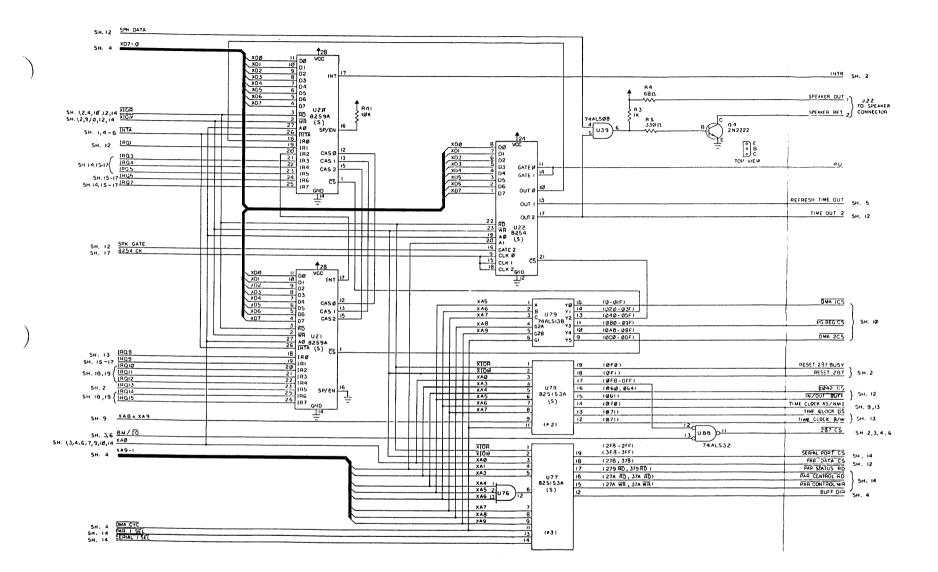

#### 8259 INTERRUPT CONTROLLERS

On Sheet 11 of the schematic, the two Intel 8259A interrupt controllers at U20 and U21 are cascaded to allow up to 15 I/O devices to request service (interrupt) from the CPU. The 8259As manage multiple interrupt sources for the CPU. They are programmed by the CPU using the XDO through XD7 data lines for data, the XAO address line to select internal registers, and the XIOR- and XIOW- read and write strobes to control read and write operations.

When an I/O device interrupts, the request is processed within the 8259A as previously programmed by the CPU. Interrupt priorities are then resolved and any requests for service can be ignored. An interrupt controller asserts INTR to inform the CPU that an I/O device has requested service.

The CPU then interrogates the 8259As to determine which device interrupted. Interrupt requests from such devices as Channel 0 of counter/timer U22 appear at an IRO input of U20.

Channel 0, a general-purpose interrupt, is assigned the highest priority interrupt line IRQO. Other interrupts from the I/O channels, keyboard, etc. are assigned lower priority (higher numbered) inputs into the interrupt controllers. Both controllers are tied together by the CASO - CAS2 cascade lines. U21 interrupts U20 by sending its INT output to the IR2 input of U20. U20, in turn, asserts INT to the CPU.

The sources of interrupts are from the keyboard, real-time clock, numeric coprocessor, floppy disk controller, hard disk controller, and devices on the I/O bus. A non-maskable interrupt directly to the CPU is provided in the event that a parity error occurs in RAM or an error occurs on the I/O bus.

## 8254 PROGRAMMABLE TIMER

On Sheet 11, the 8254 counter/timer has three programmable timer channels. The 8259As are programmed by the CPU using the XDO - XD7 data lines for data, the XAO and XA1 address lines to select internal registers, and the XIOR- and XIOWread and write strobes to control read and write operations.

The 1.19-MHz clock for the counter channels is generated by U45 and U59 on Sheet 17. Channel 0 generates a general-purpose interrupt to 8259A U20. Every 15 microseconds, Channel 1 issues the REFRESH TIME OUT signal to trigger a memory refresh cycle. Channel 2 provides a square wave to modulate a speaker.

This square-wave output is ANDed with speaker data (SPK DATA from latch Ul4) and sent through an amplifier at Q4 to the J22 speaker connector. The output is also sent to buffer Ul5 to be returned to the system data bus.

## KEYBOARD CONTROLLER

An Intel 8042 at Ul0 on Sheet 12 is a single-chip microcomputer that provides the interface between the system data bus and the keyboard. The 8042 contains proprietary firmware to scan the keyboard for depressed keys and to convert the keycodes into standard eight-bit ASCII character codes used by the system's software.

KBD DATA is a bidirectional signal. The signal can be sent either by the 8042 to the keyboard or by the keyboard to the 8042. The KBD CLK signal is sent by the keyboard to the 8042. When a key is depressed, corresponding clock and data are sent back to the TEST 0 and TEST 1 inputs.

The microcomputer then interrupts the CPU via the IRQl line to interrupt controller U20. The CPU reads the ASCII code on the XDO - XD7 data lines using the XIOR- read strobe. During system power up UlO is reset by the RESET line going high from U87 (Sheet 2). When the CPU is in its Protected-

)

Address mode, UlO can also recognize a software reset to the CPU (SOFT RESET 286) that will cause it to go into the Real- Address mode.

Also on Sheet 12 and connected to the XDO - XD7 data lines is a general-purpose latch composed of latch Ul4 and buffer Ul5. The latch and buffer are controlled by IN/OUT BUFF- from I/O decoder U78 (Sheet 11) and by the XIOR- and XIOW- I/O read and write strobes.

The output of U14 includes signals to enable a parity check (EN PAR CK), supply a speaker gate to Channel 2 of the 8254A (SPK GATE) and data (SPK DATA), and a I/O channel check line (CH IO CK) to the relevant circuits indicated. Buffer U15 reads several similar signals.

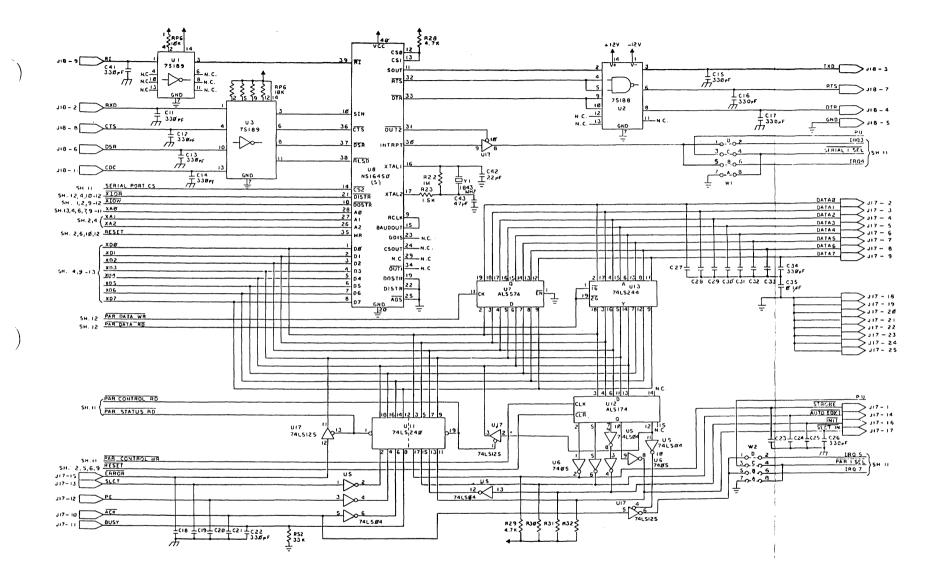

## **RS-232C INTERFACE CHANNEL**

The EIA-standard RS-232C serial channel is controlled by a National 16450 Asynchronous Communications Element. The 16450 supports asynchronous serial communication at standard baud rate increments from 50 to 9,600 baud.

The TeleVideo AT uses a nine-pin, D-subminiature type connector for interconnection with peripheral devices. Two RS-232C channels can be accommodated in the AT. The assignment of the serial port is jumper-selectable to Port 1 or Port 2. See the "External Interfaces" chapter for pinouts and electrical characteristics of this and other external connectors.

## RS-232C Serial Port

On Sheet 14, National 16450 Communications Controller U8, receivers U1 and U3, and driver U2 implement a standard RS-232C communications channel. The National NS16450 Asynchronous Communication Element performs parallel-to-serial conversion of outgoing data from the XDO - XD7 data lines to the TXD line, and serial-to-parallel conversion of incoming data from the RXD line to the data bus. The communications controller contains its own baud rate generator clocked by a 1.843-MHz crystal at Y1. U2 is a standard 75188 RS-232C line driver carrying signals Transmit Data (TXD), Request to Send (RTS), and Data Terminal Ready (DTR) to the peripheral device from U8.

Similarly, Ul and U3 are standard 75189 line receivers carrying signals Ring Indicator (RI), Receive Data (RXD), Clear to Send (CTS), Data Set Ready (DSR), and Carrier Detect (CDC) from the peripheral device to U8.

## PARALLEL PRINTER PORT

The parallel printer port is intended primarily for support of a Centronix-compatible parallel printer, but can be used with other output-only devices if desired. A female, 25-pin D-subminiature type connector is used. All signals are at standard TTL levels. The assignment of the parallel port is jumper-selectable to Port 1 or Port 2. Refer to the "External Interfaces" chapter for pinouts and electrical characteristics.

At the bottom of Sheet 14, the Centronixcompatible parallel printer port is composed of two latches at U7 and Ul2, and two buffers at Ull and Ul3. Data sent to the printer from the XDO - XD7 data lines from the CPU are latched by U7 by PAR DATA WR- (Sheet 12) and sent out to connector J17 as DATAO - DATA7. Buffer Ul3 is wired across the inputs and outputs of U7 for diagnostic loopback purposes and to test whether port 1 or port 2 is selected on the motherboard. Ul3 is enabled by PAR DATA RD-.

Control signals to the printer are also sent on the system data bus to latch Ul2. Signals sent to the printer are the data strobe (STROBE), auto line-feed (AUTO FDXT), an initialization line (INIT-), and a printer selection line (SLCT IN-).

These four signals are also sent to buffer Ull and tri-state buffer Ul7. The incoming status signals include a line to indicate a printer error (ERROR-) printer selection (SLCT), paper empty (PE), a printer acknowledge line (ACK-), and a printer busy signal (BUSY).

2.22

1

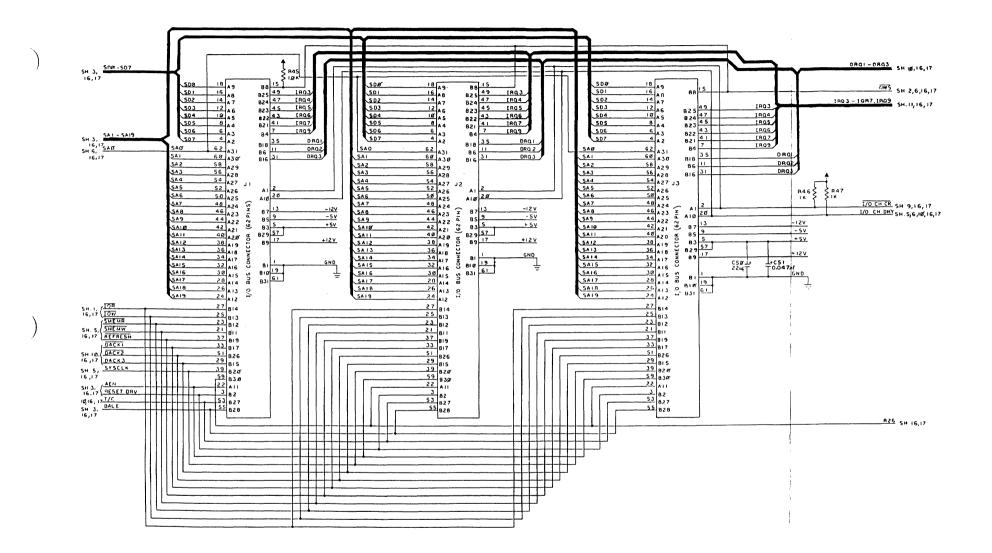

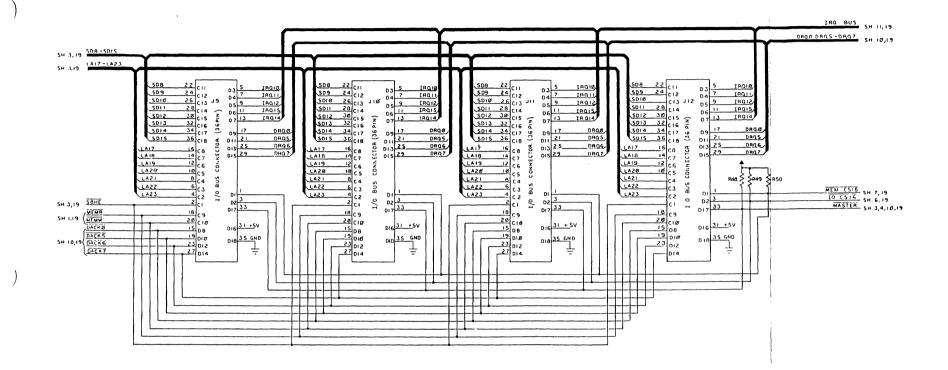

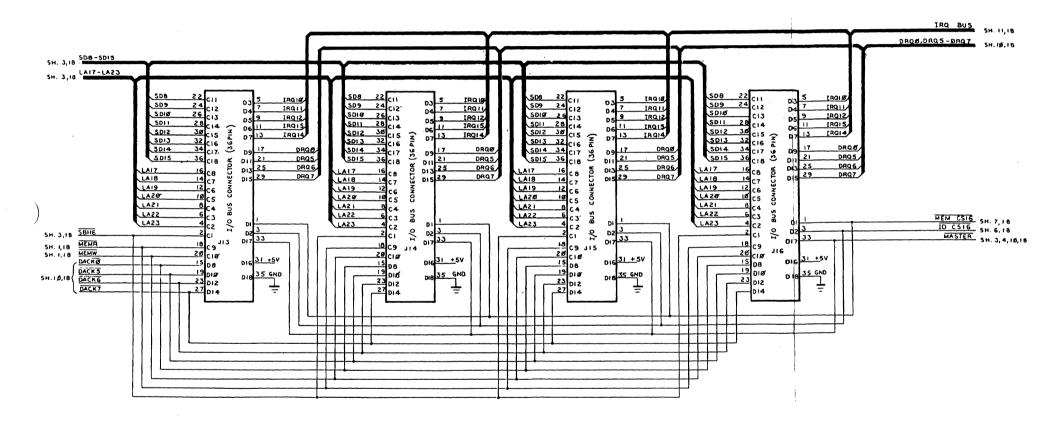

# I/O CHANNELS

A total of eight I/O channels on the motherboard are used by plug-in boards, such as memory expansion, modems and peripheral controllers, and so forth. Six of the channels provide the plug-in board with two connectors. One 62-pin connector is identical to that used in earlier 8-bit 8088-based PC-type systems, and a smaller 36-pin connector is used to expand bus data transfer capability to a full 16 bits.

Each I/O channel is electrically parallel with the other seven channels, as shown on Sheets 15 - 19 of the schematic The 62-pin connector (JI - J8) is functionally identical to that on PC-type systems providing control, address and data lines useful for 8-bit I/O hardware.

A second, 36-pin, connector (J10 - J14 and J16) is compatible with PC AT-type systems providing the control, address and data lines necessary for 16bit I/O hardware. See the External Interfaces chapter of this manual for pinouts and electrical characteristics.

) )

### 3 HARDWARE FUNCTIONS - DISKETTE (FLOPPY)/ FIXED (HARD) DISK CONTROLLER

### Introduction

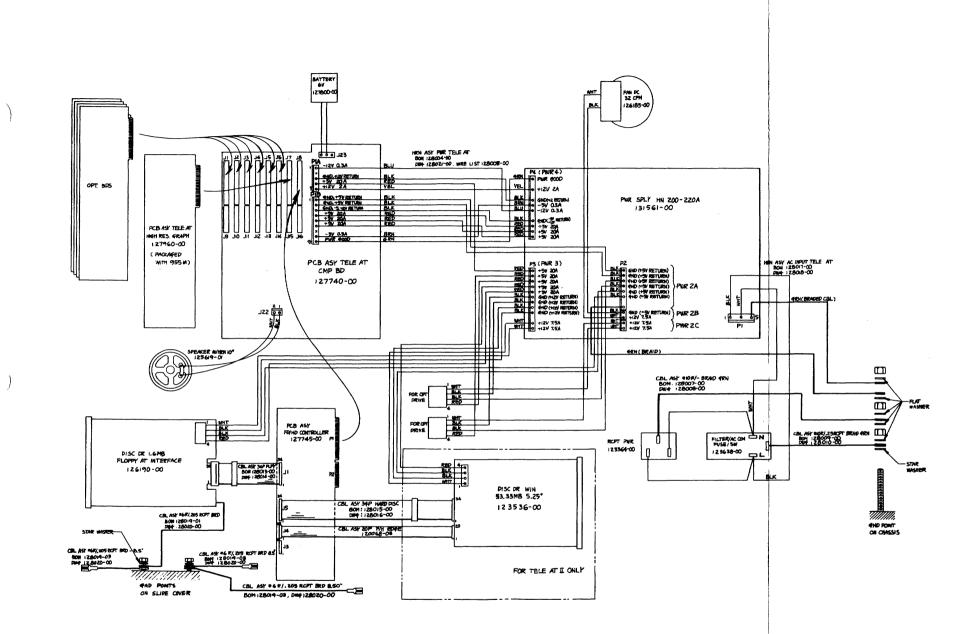

The Diskette/Fixed Disk Controller, an adaptor board, connects to the motherboard using one of the 16-bit expansion slots. This single board provides all signals necessary to operate up to two fixed drives and two 5 1/4-inch diskette drives. The controller allows concurrent data operations on one diskette and one fixed disk drive.

This chapter is divided into two sections. The first section is devoted to diskette controller functions. The second section covers fixed disk (Winchester) controller functions.

### DISKETTE CONTROLLER

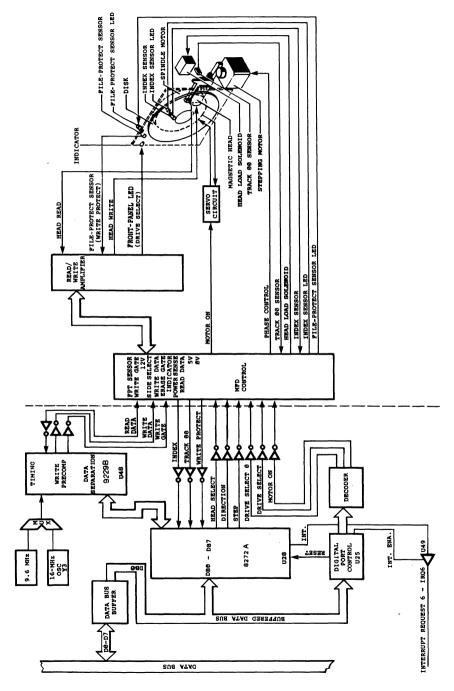

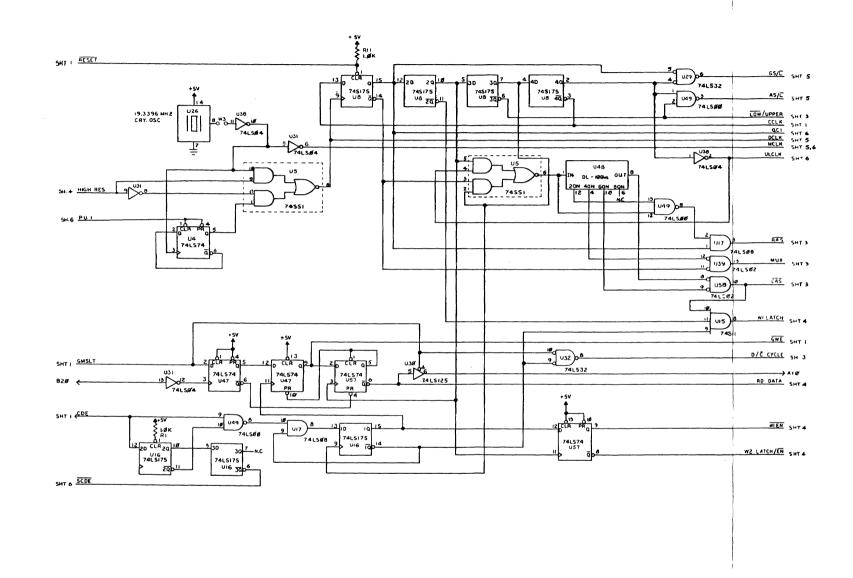

The diskette control circuitry (see Figure 3-1) is based around the 8272A (U28) or NEC D765AC diskette controller chip. The chip provides parallel-toserial and serial-to-parallel data conversion and drive selecting and head tracking functions. The 8272A FDC is programmed to operate in the burst transfer mode. The programming is done by the EPROM during system initialization.

The support 9229B (U48) performs all write precompensation functions. The 9229B also separates data and clock pulses that compose the MFM data being read off the diskette to ensure accurate data exchanges with the 8272A.

The bidirectional buffer (U81) and the diskette drive latch (U17) are important support IC's. They control disk drive selection and starting the diskette motor. These are taken as control words from the system data bus. The basic functions of the diskette controller circuitry are:

- 1. Writing data to the diskette

- 2. Reading data from the diskette

- 3. Determining where to write on the diskette

- 4. Turning the drive off and on and selecting drive A or B

)

1

Functions 1, 2, and 3 are all controlled by the 8272A diskette controller.

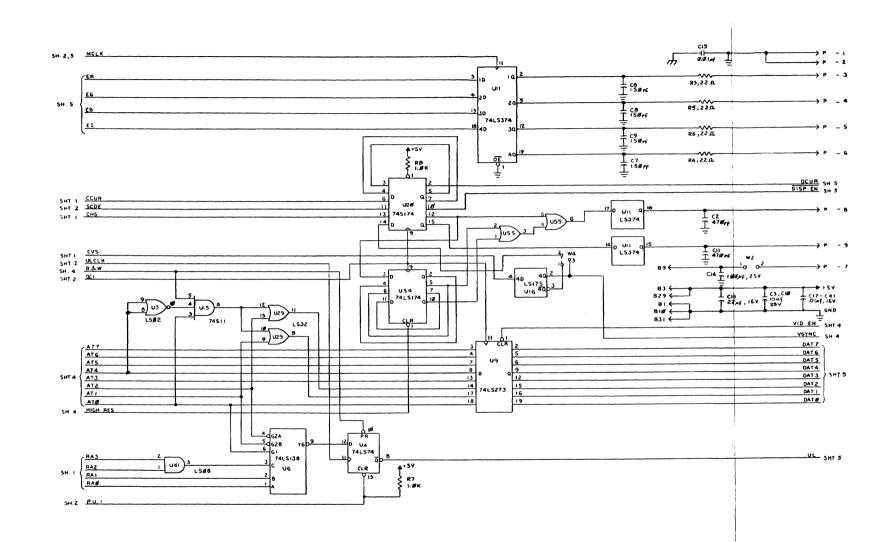

### Figure 3-1 Diskette Controller

FUNCTIONS - DISK CONTROLLER 3.3

| The major comp<br>are:                                                                                        | onents of the diskette controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| U28 Intel 8272A Diskette Controller Device<br>U17 Diskette Drive Control Latch<br>U48 FDC9229B Data Separator |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| The diskette c<br>descriptions a                                                                              | ontroller components and their<br>re listed in Table 3-1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Table 3-1<br>Diskette Contr                                                                                   | oller Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Device or Line                                                                                                | Source/Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| Diskette<br>Controller                                                                                        | Provides parallel-to-serial<br>conversion of data from the system<br>to the diskette, and serial-to-<br>parallel conversion from the<br>diskette to the system. Provides<br>all drive control functions, such as<br>head step, head direction, write<br>protect, and track 0 detection. The<br>controller can be programmed to<br>handle seek track, read sector,<br>write sector, read address, read<br>track, and write track operations.<br>The DB0-DB7 Data Transceiver carries<br>data and programming signals between<br>the diskette controller and CPU. |  |  |

| -COMP READ<br>DATA                                                                                            | FDD. Carries composite read data<br>from the diskette drives.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| -COMP WR<br>DATA                                                                                              | FDC. Carries composite write data<br>to diskette drives.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Diskette<br>Drive Control                                                                                     | Controls the selection of the<br>diskette drive, turning the motor<br>on/off, enabling/disabling<br>interrupt, enabling/disabling DMA<br>operation, and resetting the<br>diskette controller.                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Data<br>Separator                                                                                             | Performs write precompensation and<br>data separation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

1

)

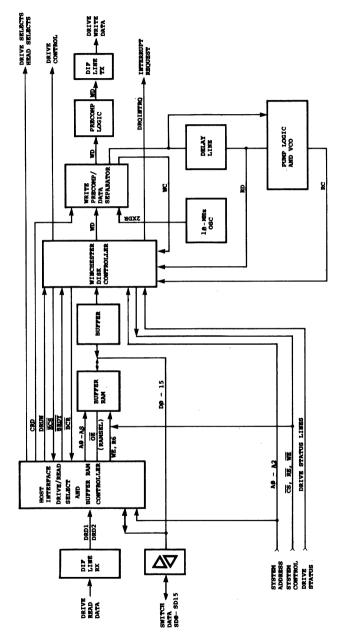

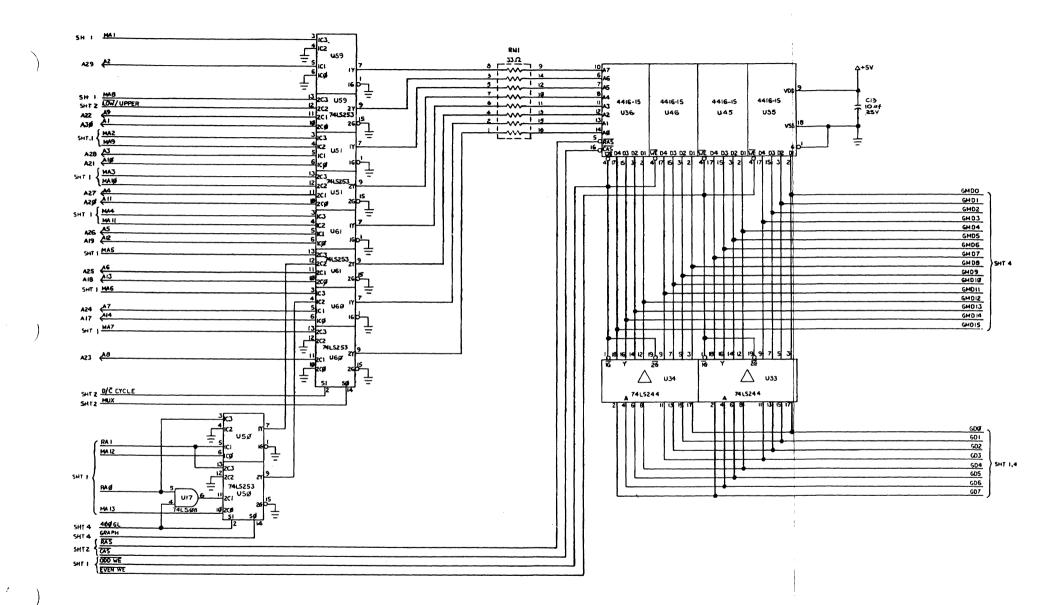

### FIXED DISK (WINCHESTER) CONTROLLER INTERFACE

The major components of the Winchester controller interface and their descriptions are listed in Table 3-2.

A block diagram of the Winchester controller interface is shown in Figure 3-2.

Table 3-2 Fixed Disk (Winchester) Controller Interface Components

ì

1

| Device or Line                                               | Source/Description                                                                                                  |  |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|

| Data/Address<br>Transceiver and<br>Control Signals<br>Buffer | The transceiver and buffer pass<br>data, and control signals to an<br>external Winchester disk<br>controller board. |  |

| WDO-WD7                                                      | Data/Address Transceiver.<br>Buffered data lines to the<br>Winchester controller board.                             |  |

| WAO-WA2                                                      | Control signals buffer.<br>Buffered address lines to the<br>Winchester controller board.                            |  |

| -WCS,-WWE,<br>-WRE,WMR,<br>-WDC,RD                           | Control signals buffer.<br>Buffered control signals to the<br>Winchester controller board.                          |  |

#### FIXED DISK (WINCHESTER) CONTROLLER

The Winchester disk controller provides all control and data handling functions needed to interface the system with a 5 1/4-inch Winchester disk drive. Figure 3-2 shows a block diagram of the Winchester disk controller board.

```

Figure 3-2

Fixed Disk (Winchester) Controller Board Block

Diagram

```

)

FUNCTIONS - DISK CONTROLLER 3.6

The major components of the fixed disk controller are:

| <b>U8</b>  | WD1010-05 Winchester Disk Controller |

|------------|--------------------------------------|

| U26        | WD1100-10 Write Precompensation and  |

|            | Data Separator                       |

| U60,61     | Buffer RAM (two provided)            |

| U62        | Error Amplifier                      |

| U2,19      | Pump Logic                           |

| U39        | Voltage Controlled Oscillator (VCO)  |

| <b>U</b> 5 | Differential Line Receiver           |

| U4         | Differential Line Transmitter        |

### System/Controller Interface

The system programs the Winchester disk controller by accessing the task file registers of the WD1010-05 controller device.

The system/controller interface lines are shown in Figure 3-2.

Table 3-3 lists the system/controller interface components and their descriptions.

### Table 3-3 System/Controller Interface Components

| Active Line | Source/Description                                                             |  |  |

|-------------|--------------------------------------------------------------------------------|--|--|

| A0 to A2    | System. Task file register<br>address.                                         |  |  |

| -WE or -RE  | SystemWE to activate task file<br>write, or -RE to activate task<br>file read. |  |  |

| SDO to SD15 | System. Data or command.                                                       |  |  |

### **Operations With Dual-Port Buffer RAM**

The Winchester disk controller uses dual 1 kilobyte by 8-bit buffer RAM to interact with the system during disk read and write operations. When writing to the disk, the system writes the data to the buffer RAM by sector. After a sector of data is loaded into the buffer RAM, the WD1010-05 writes the data from the buffer RAM to the disk. Table 3-4 lists the write from buffer RAM signals.

### Table 3-4 Write From Buffer RAM

| Active Line | Source/Description                                                                                                                                                                                        |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDO to SD15 | System. Sets up the Task File<br>Register and the Write Sector<br>command in the WDl010-05 task<br>file and writes data to buffer<br>RAM.                                                                 |

| -BCR        | WD1010-05. Strobed to zero counter.                                                                                                                                                                       |

| BDRQ        | WD1010-05. Active to indicate<br>that the buffer RAM is empty.                                                                                                                                            |

| -BCS        | WD1010-05. Set high to enable<br>the host control of buffer RAM.<br>Transceiver direction is ready<br>for write.                                                                                          |

| -we         | System. Loads the buffer and<br>increments the counter<br>with - HDCS.                                                                                                                                    |

| BRDY        | Active to indicate the buffer is full.                                                                                                                                                                    |

| -BCS        | WD1010-05. Active to<br>disconnect the host control of<br>the buffer RAM. Board busy<br>tristate buffer on line WD7 is<br>activated by -BCS to prevent<br>the system access during the<br>next operation. |

| -WDRE       | WD1010-05. Reads the buffer<br>RAM to transfer data to disk<br>(See Writing Disk Data).                                                                                                                   |

### Table 3-4 (continued) Write From Buffer RAM Active Line Source/Description -BCS WD1010-05. Set high to allow the next operation by the system. Board busy tristate buffer is inactive. INTRO WD1010-05. Signals the end of the command to the system. Reads of dual-port buffer RAM occur after a sector of data has been loaded to the RAM from the disk. For a read from buffer RAM, see Table 3-5. Table 3-5 Read From Dual-Port Buffer RAM Active Line Source/Description SDO to SD15 System. Sets up the Task File Registers and places the Read Sector command in the WD1010-05 task file. WD1010-05. Active to -BCS disconnect the host control of buffer RAM. -BCR WD1010-05. Strobed to zero counter. WD1010-05. Loads the buffer -WDWE from the disk (See Reading Disk Data), and increments the counter with -CS. Active to indicate that the BRDY buffer is full. -BCR WD1010-05. Strobed to zero counter.

### Table 3-5 (continued) Read From Dual-Port Buffer RAM

| Active Line | Source/Description                                                    |  |  |

|-------------|-----------------------------------------------------------------------|--|--|

| -BCS        | WD1010-05. Set high to enable<br>the system control of buffer<br>RAM. |  |  |

| BDRQ        | WD1010-05. Active to initiate transfer to the system.                 |  |  |

| -RE         | System. Reads buffer RAM and increments the counter with -CS.         |  |  |

| BRDY        | Active to indicate that the<br>buffer is empty.                       |  |  |

| INTRQ       | WD1010-05. Set high to stop<br>the operation.                         |  |  |

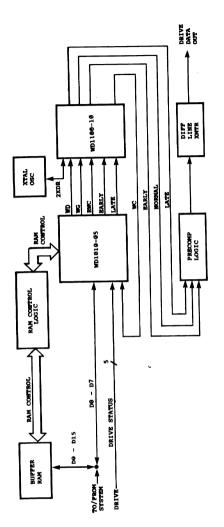

### Writing Disk Data

The write sector command requires that the Winchester controller locate the place on the disk that is to receive the data. The command also controls the write operation to buffer RAM. It must then read the data from the buffer RAM, condition the data into MFM format, and write the data to disk.

Under MFM, clock bits are recorded only when two successive data bits are missing in the serial data stream. Using MFM reduces the total number of bits required to record a given amount of information on the disk. Because this effectively doubles the amount of disk capacity, it is termed "double density."

#### Encoding MFM follows three rules:

- If the current data cell contains a data bit, then no clock is generated.

- 2. If the previous data cell contained a data bit, then no clock is generated,

- 3. If the previous data cell and the present data cell are vacant, then a clock is generated in the current clock cell.

Data and clock cells are defined by the state of the write clock (WC) line. If WC is low, it is a data cell; if WC is high, it is a clock cell. Both clock and data cells are 100 nanoseconds long in ST506-compatible drives.

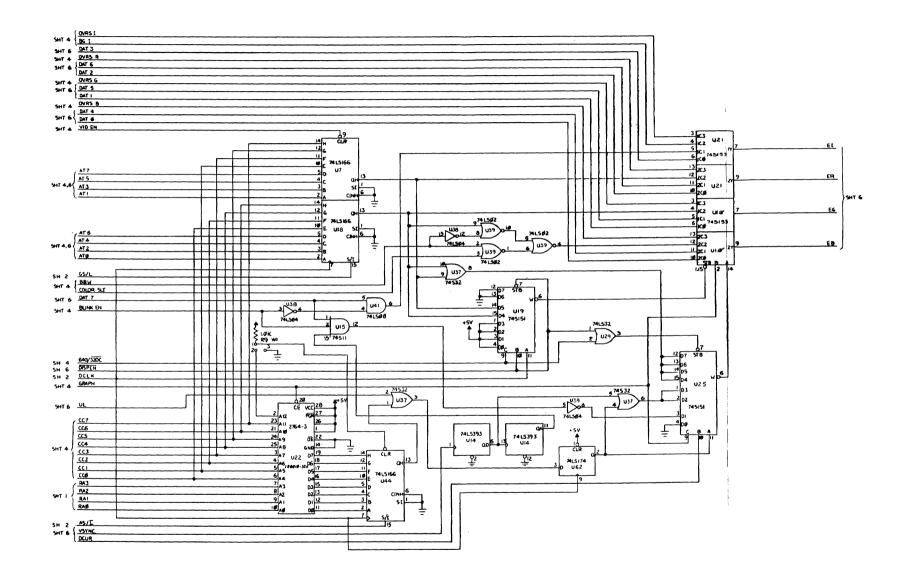

The active lines for writing disk data are shown in Figure 3-3 and listed with a description in Table 3-6.

Figure 3-3 Writing Disk Data

# Table 3-6 Writing from Buffer RAM Active Line Source/Description

- D0 to D7 System. Contains the write sector command. When the WD1010-05 receives this command, it checks its cylinder registers against the current cylinder position.

- -BCR WD1010-05. Strobed to begin write to buffer RAM by the system.

BRDY Buffer RAM is full.

- -BCS WD1010-05. Active to disconnect the host control of the buffer RAM.

- -STEP,-DIRET WD1010-05. Moves head to locate cylinder.

- SEEK COMPLETE Drive. Informs the WD1010-05 that the head settling time for the current step is expired. If the current step is not the required cylinder position, the head is moved again. After seek to desired cylinder, the controller checks for the desired sector address by reading data from the drive.

- WG WD1010-05. Write gate signal to WD1100-10.

WC WD1100-10. Carries the 5-MHz write clock, derived from the 2XDR clock signal, to WD1010-05.

- -RWC WD1010-05. Reduced write current signal; turns on precompensation circuits for write to disk.

- -WD WD1010-05. Write data as read from buffer RAM and serialized by WD1010-05.

## Table 3-6 (continued) Writing from Buffer RAM

| Active Line             | Source/Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -EARLY, -LATE           | WD1010-05. Precompensation<br>signals to WD1100-10.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                         | Precompensation is used to<br>counteract the effects of<br>dynamic bit shift when writing<br>the inside recorded tracks of<br>the disk. Dynamic bit shift<br>results when a bit on the disk<br>influences the position of an<br>adjacent bit. The leading<br>edges of the bits are moved<br>closer together, or further<br>apart, depending upon the<br>polarity of each bit. Because<br>positions of bits shift as they<br>are written to the disk, data<br>is harder to recover without<br>error. Write precompensation<br>is applied to counteract the<br>effects of dynamic bit shift. |

|                         | Precompensation predicts the<br>direction a bit will be<br>shifted. It then writes the<br>bit out of position in the<br>opposite direction of the<br>shift. The prediction is done<br>in the WD1010-05 by checking<br>the next two data bits, the<br>last bit written, and the<br>present bit.                                                                                                                                                                                                                                                                                             |

| EARLY, NORMAL,<br>LATE- | WD1100-10. Precompensation<br>signals to precompensation<br>logic. Data is shifted +/-12<br>nanoseconds from the normal<br>position through a delay line.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Data                    | Differential Line Driver.<br>Carries MFM formatted,<br>precompensated, RS-422 write<br>data to the drive head.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

)

### Table 3-6 (continued) Writing from Buffer RAM

| Active Line | Source/Description                                  |  |  |

|-------------|-----------------------------------------------------|--|--|

| -BCS        | Set high to allow the next operation by the system. |  |  |

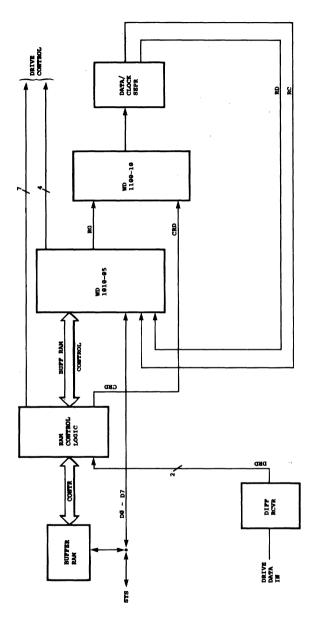

### Reading Disk Data

)

For disk reads, the Winchester disk controller board locates the sector to be read, identifies the start of the data field, reads the data in from the disk, separates the data and clock signals, writes the data to buffer RAM, and controls the system read of the data out of buffer RAM.

The active lines for reading disk data are shown in Figure 3-4 and listed with a description in Table 3-7.

Figure 3-4 Reading Disk Data

Ì