ADDENDUM AND

# **Document Change Notice**

Copyright 1981 by Zilog, Inc. All rights reserved. No part of this publication may be reproduced without the written permission of Zilog, Inc. The information in this publication is subject to change

without notice.

#### 1981 DATA BOOK

# Document Change Notice

for Microcomputer Components Data Book

#### December 1981

Publication No: 00-2034-01 DCN No.: E0-2034-01

This Document Change Notice provides changes for the publication specified above as well as for the stand-alone product specifications on each product. These changes will remain in effect unless specifically amended by another DCN or superceded by a publication revision. Please file this DCN at the back of specified documents to provide a record of changes.

Note: The first page cited refers to the 1981 Data Book. The second page, cited in parentheses, refers to the individual product specification printed stand-alone in cases where the change is applicable to both.

Page iii Delete the final paragraph.

Page 3

## Z8400 Z80<sup>®</sup> CPU Product Specification

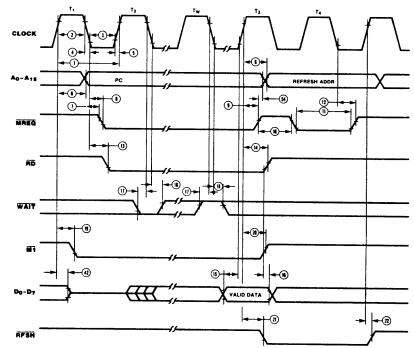

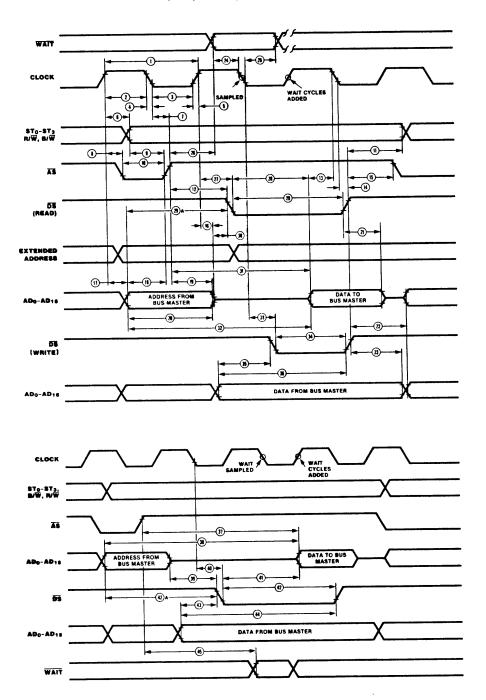

Page 18 (Page 14) In Figure 5, delete #45 and insert #54 in its place.

Delete Z80 CPU from right margin.

NOTE:  $T_{\mathbf{w}}$ -Wait cycle added when necessary for slow ancilliary devices.

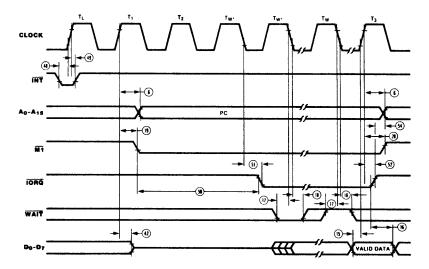

Figure 5. Instruction Opcode Fetch

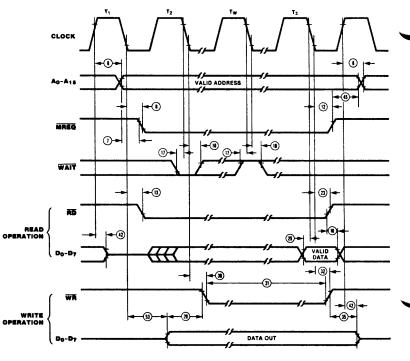

In Figure 6, "Memory Read or Write Cycle," extend parameter 45 as illustrated in the corrected version of the art that follows.

Figure 6. Memory Read or Write Cycles

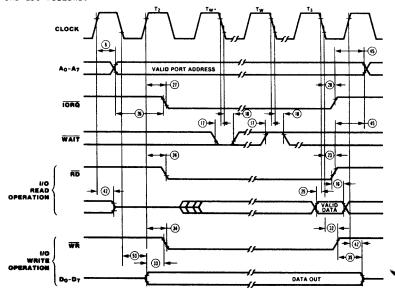

In Figure 7, "Input or Output Cycles," the diagram is incorrect for the ADDRESS BUS, the INPUT/OUTPUT REQUEST, and WAIT lines. A corrected version of the art follows.

NOTE:  $T_{w^*} = One$  Wait cycle automatically inserted by CPU.

2

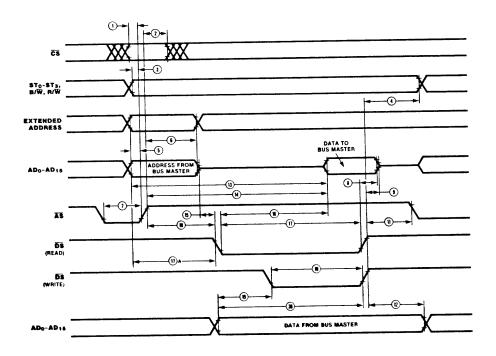

Page 19 (Page 15) In Figure 8, "Interrupt Request/Acknowledge Cycle," the diagram is incorrect for the ADDRESS BUS, MACHINE CYCLE ONE and INPUT/OUTPUT REQUEST lines. A corrected version of the art follows.

NOTE: 1)  $T_L$  = Last state of previous instruction.

2) Two Wait cycles automatically inserted by CPU(\*).

Figure 8. Interrupt Request/Acknowledge Cycle

Page 24 (Page 20) Make the following changes in **AC CHARACTERISTICS:**

- In parameter 45 change "Address Stable after" to "to Address Hold Time."

- 2) Add the following line of characteristics:

|        |          |                                | Z <b>8</b> 0 | Z80A | <b>Z808</b> |

|--------|----------|--------------------------------|--------------|------|-------------|

|        |          |                                | CPU          | CPU  | CPU         |

| Number | Symbol   | Parameter                      | min.         | min. | min.        |

|        |          |                                |              |      |             |

| 54     | TdCTr(A) | MREQ, IORQ, RD to Address Hold | 0            | 0    | 0           |

|        |          | Time                           |              |      |             |

3) Add the footnote:

\*\* All timings assume equal loading on pins with 100 pF.

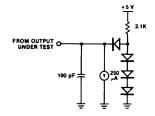

Page 25 (Page 21) In **Standard Test Conditions** the art is incorrect. A corrected version follows.

# Z8440 Z80 SIO Product Specification

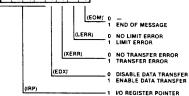

Page 80 (Page 10) In Figure 13, "Read Register Bit Functions," add the following note to Read Register 2\*:

\*(Channel 8 only)

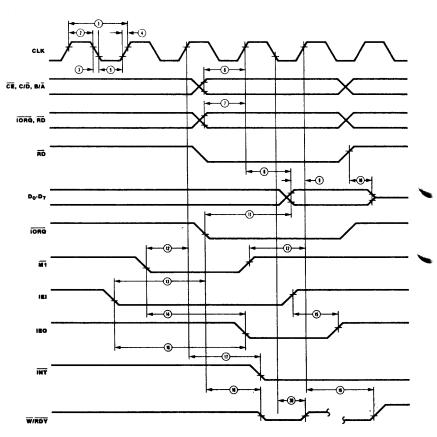

Page 84 (Page 14) To the diagram of AC Electrical Characteristics add W/RDY, WAIT/READY, as a label to the last signal line. A corrected version of the art for that line follows.

The parameter of number 18 should read:

$\overline{IORQ}$  + or  $\overline{CE}$  + to  $\overline{W}/\overline{RDY}$  + Delay (Wait Mode).

The parameter of number 19 should read:

Clock + to  $\overline{W}/\overline{RDY}$  + Delay (Ready Mode).

# Z8470 Z80 DART Product Specification

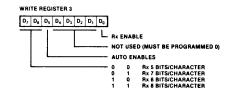

Page 96 (Page 8) In the **Z80 Dart Read and Write Registers,** Write Register 3, the label for bits  $D_4-D_3-D_2-D_1$  should read:

Not Used (Must Be Programmed 0)

# Z8001/2 Z8000<sup>TM</sup> CPU Product Specification

Page 105

The final Feature should read:

(Page 1)

4, 6, and 10 MHz clock rate.

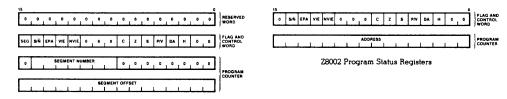

Page 107 (Page 3) In **Program Status Information,** Figure 5, "Z8000 CPU Special Registers" the Flag and Control Word art is incorrectly labeled in bit 13. It should read EPA. A corrected version of the art follows.

Z8001 Program Status Registers

### Figure 5. Z8000 CPU Special Registers

In Interrupt and Irap Structure, the first sentence of the second paragraph should read:

The CPU supports three types of interrupts (non-maskable, vectored and non-vectored) and four traps (system call, <u>Extended Processing</u> <u>Architecture</u> instruction, privileged instructions and segmentation trap).

In Interrupt and Trap Structure the first sentence of the third paragraph should read:

The remaining traps occur when instructions limited to the system mode are used in the normal mode, or as a result of the System Call instruction, or for an  $\underline{EPA}$  instruction.

Change Z8010 MMU in right margin to Z8001/2 CPU.

In **Reset** delete "ST $_0$ -ST $_3$  and" from the third entry.

Page 127

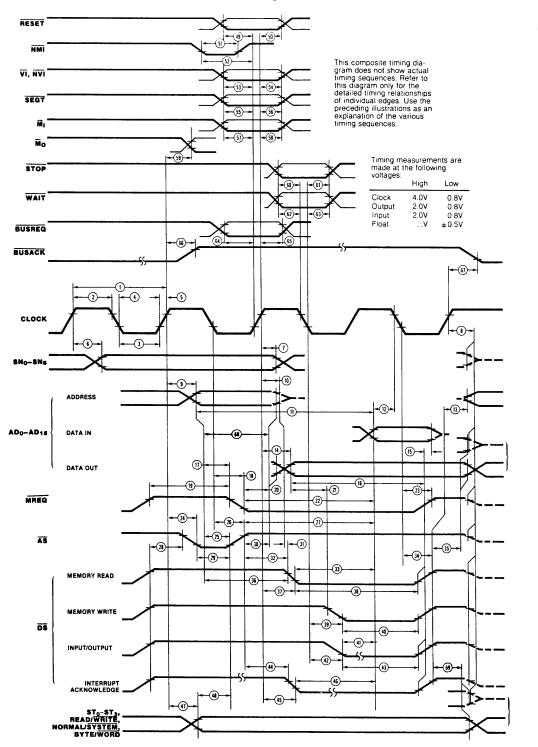

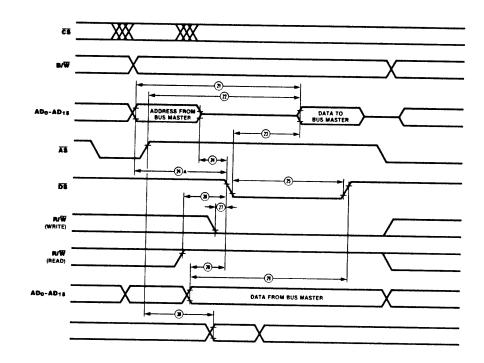

To the **Composite AC Timing Diagram** add the parameters 68 and 69 as illustrated in the following corrected art.

Page 129 (Page 25)

, see

| Pag      | e 129)                |                                                                       | Z8001<br>4M                                   | /Z8002<br>Hz | 6M           |         | 10      | /Z8002B<br>MHz |

|----------|-----------------------|-----------------------------------------------------------------------|-----------------------------------------------|--------------|--------------|---------|---------|----------------|

| No.      | Symbol                | Parameter                                                             | Min(ns)                                       | Max(ns)      | Min(ns)      | Max(ns) | Min(ns) | Max(ns         |

| 1        | TcC                   | Clock Cycle Time                                                      | 250                                           | 2000         | 165          | 2000    | 100     | 2000           |

| 2        | TwCh                  | Clock Width (High)                                                    | 105                                           | 2000         | 70           | 2000    | 40      |                |

| 3        | TwC1                  | Clock Width (Low)                                                     | 105                                           | 2000         | 70           | 2000    | 40      |                |

| 4        | TfC                   | Clock Fall Time                                                       |                                               | 20           |              | 10      |         | 10             |

| 5        | TrC                   | Clock Rise Time                                                       |                                               | 20           |              | 15      |         | 10             |

| 6        | TdC(SNv)              | Clock † to Segment Number Valid                                       |                                               | 130          |              | 110     |         | 70             |

|          |                       | (50 pF load)                                                          |                                               |              |              |         |         | 70             |

| 7        | TdC(SNn)              | Clock † to Segment Number Not Valid                                   | 20                                            |              | 10           |         | 5       |                |

| 8        | TdC(Bz)               | Clock ↑ to Bus Float                                                  |                                               | 65           |              | 55      | -       | 40             |

| 9        | TdC(A)                | Clock † to Address Valid                                              |                                               | 100          |              | 75      |         | 50             |

| 10       | TdC(Az)               | Clock † to Address Float                                              |                                               | 65           |              | 55      |         | 40             |

| 11       | TdA(DR)               | Address Valid to Read Data Required                                   |                                               | 475*         |              | 305*    |         | 180*           |

|          | ,,                    | Valid                                                                 |                                               | 475          |              |         |         | 100.           |

| 12       | TsDR(C)               | Read Data to Clock + Setup Time                                       | 30                                            |              | 20           |         | 10      |                |

| 13       | TdDS(A)               | DS ↑ to Address Active                                                | 80*                                           |              | 45*          |         | 20*     |                |

| 14       | TdC(DW)               | Clock † to Write Data Valid                                           | 00                                            | 100          | 47.          | 75      | 20*     | 50             |

| 15       | ThDR(DS)              | Read Data to DS + Hold Time                                           | 0                                             | 100          | 0            | 15      | 0       | 50             |

| 16       | TdDW(DS)              | Write Data Valid to DS ↑ Delay                                        | 295*                                          |              | 195*         |         |         |                |

| 17       | TdA(MR)               | Address Valid to MREQ + Delay                                         | 275×                                          |              |              |         | 110*    |                |

| 18       | TdC(MR)               | Clock $\neq$ to MREQ $\neq$ Delay                                     | , <u>, , , , , , , , , , , , , , , , , , </u> | 80           | 35*          | 70      | 20*     | 60             |

| 19       | TwMRh                 | MREQ Width (High)                                                     | 210*                                          | 00           | 175*         | 70      | 0.0*    | 40             |

| 20       | TdMR(A)               | MREQ + to Address Not Active                                          |                                               |              | 135*         |         | 80*     |                |

| 21       | TdDW(DSW)             |                                                                       | 70*                                           |              | 35*          |         | 20*     |                |

|          |                       | Write Data Valid to $\overline{DS} \neq$ (Write) Delay                | 55*                                           |              | 35*          |         | 15*     |                |

| 22       | TdMR(DR)              | MREQ + to Read Data Required Valid                                    | 375*                                          |              | 230 <b>*</b> |         | 140*    |                |

| 23       | TdC(MR)               | Clock + MREQ + Delay                                                  |                                               | 80           |              | 60      |         | 45             |

| 24       | TdC(ASf)              | Clock + to AS + Delay                                                 |                                               | 80           |              | 60      |         | 40             |

| 25       | TdA(AS)               | Address Valid to AS + Delay                                           | 55*                                           |              | 35*          |         | 20*     |                |

| 26       | TdC(ASr)              | <u>Cl</u> ock ↓ to AS ↑ Delay                                         |                                               | 90           |              | 80      |         | 40             |

| 27       | TdAS(DR)              | AS + to Read Data Required Valid                                      | 360*                                          |              | 220*         |         | 140*    |                |

| 28       | TdDS(AS)              | <u>DS</u> ↑ to AS ↓ Delay                                             | 70*                                           |              | 35*          |         | 15*     |                |

| 29       | TwAS                  | <u>AS</u> Width (Low)                                                 | 85*                                           |              | 55*          |         | 30*     |                |

| 30       | TdAS(A)               | AS ↑ to Address N <u>ot</u> Active Delay                              | 70 <del>*</del>                               |              | 45*          |         | 20*     |                |

| 31       | TdAz(DSR)             | Address Float to DS (Read) + Delay                                    | 0                                             |              | 0            |         | 0       |                |

| 32       | TdAS(DSR)             | AS ↑ to DS (Read) ↓ Delay                                             | 80*                                           |              | 55 <b>*</b>  |         | 30*     |                |

| 33       | TdDSR(DR)             | DS (Read) + to Read Data Required Valid                               | 205*                                          |              | 130*         |         | 70*     |                |

| 34       | [dC(DSr)              | <u>Cl</u> ock↓ to DS ↑ Delay                                          |                                               | 70           |              | 65      |         | 45             |

| 35       | TdDS(DW)              | DS + to Write Data Not Valid                                          | 75 <b>*</b>                                   |              | 45*          |         | 25*     |                |

| 36       | TdA(DSR)              | Address Valid to $\overline{\text{DS}}$ (Read) $\downarrow$ Delay     | 180×                                          |              | 110*         |         | 65*     |                |

| 37       | TdC(DSR)              | Clock + to DS (Read) + Delay                                          | 100                                           | 120          | 110          | 85      | 02      | 60             |

| 38       | TwDSR                 | DS (Read) Width (Low)                                                 | 275*                                          | 120          | 185*         | 0)      | 110*    | 00             |

| 39       | TdC(DSW)              | Clock + to DS (Write) + Delay                                         |                                               | 95           | 105          | 80      | 110     | 60             |

| 40       | TwDSW                 | DS (Write) Width (Low)                                                | 185*                                          |              | 110*         | 00      | 76*     | 00             |

| 41       | TdDSI(DR)             | $\overline{\text{DS}}$ (I/O) $\downarrow$ to Read Data Required Valid | 330*                                          |              | 110*         |         | 75*     |                |

| 42       | TdC(DSf)              | Clock $\downarrow$ to DS (I/O) $\downarrow$ Delay                     | JJU*                                          | 100          | 210*         | 00      | 120*    |                |

| 43       | TwDS                  | DS (I/O) Width (Low)                                                  | 410*                                          | 120          | 000          | 90      | 4 ( 0 * | 60             |

| 44<br>44 | TdAS(DSA)             |                                                                       | 410*                                          |              | 255*         |         | 160*    |                |

| +4<br>45 |                       | AS $\uparrow$ to QS (Acknowledge) $\downarrow$ Delay                  | 1065*                                         |              | 690*         |         | 410*    |                |

| 45<br>46 | TdC(DSA)<br>TdDSA(DR) | Clock + to DS (Acknowledge) + Delay                                   |                                               | 120          | 005 -        | 85      |         | 65             |

| +0       | TUDSA(DR)             | DS (Acknowledge) + to Read Data                                       | 455*                                          |              | 295*         |         | 165*    |                |

|          | T 10(C)               | Required Delay                                                        |                                               |              |              |         |         |                |

| 17       | TdC(S)                | Clock † to Statu <u>s</u> Valid Delay                                 |                                               | 110          |              | 85      |         | 60             |

| 48       | TdS(AS)               | Status Valid to AS + Delay                                            | 50*                                           |              | 30*          |         | 10*     |                |

| 19       | TsR(C)                | RESET to Clock + Setup Time                                           | 180                                           |              | 70           |         | 50      |                |

| 50       | ThR(C)                | RESET to Clock † Hold Time                                            | 0                                             |              | 0            |         | 0       |                |

| 51       | TwNMI                 | NMI Width (Low)                                                       | 100                                           |              | 70           |         | 50      |                |

| 52       | TsNMI(C)              | NMI to Clock † Setup Time                                             | 140                                           |              | 70           |         | 50      |                |

| 53       | IsVI(C)               | VI, NVI to Clock + Setup Time                                         | 110                                           |              | 50           |         | 40      |                |

| 54       | ThVI(C)               | VI, NVI to Clock + Hold Time                                          | 20                                            |              | 20           |         | 10      |                |

| 55       | TsSGT(C)              | SEGT to Clock † Setup Time                                            | 70                                            |              | 55           |         | 40      |                |

| 6        | ThSGT(C)              | SEGT to Clock * Hold Time                                             | 0                                             |              | Ő            |         | 40      |                |

| 57       | TsMI(C)               | MI to Clock ↑ Setup Time                                              | 180                                           |              | 110          |         | 80      |                |

| 8        | ThMI(C)               | MI to Clock <sup>↑</sup> Hold Time                                    | 0                                             |              | 0            |         | 0       |                |

| 9        | TdC(MO)               | Clock † to MO Delay                                                   | U                                             | 120          | U            | 85      | U       | 70             |

| 50       | TsSTP(C)              | STOP to Clock + Setup Time                                            | 140                                           | 120          | on           | 67      | 50      | 70             |

|          |                       | STOP CO CIUCK 7 JELUD IINE                                            | 140                                           |              | 80           |         | 50      |                |

\*Clock-cycle-time-dependent characteristics. See table on following page.

|     |           |                              | Z8001/Z8002<br>4₩Iz | Z8001A/Z8002A<br>6MHz | Z8001B/Z8002B<br>10MHz |

|-----|-----------|------------------------------|---------------------|-----------------------|------------------------|

| No. | Symbol    | Parameter                    | Min(ns) Max(ns)     | ) Min(ns) Max(ns)     | Min(ns) Max(ns)        |

| 61  | ThSTP(C)  | STOP to Clock + Hold Time    | 0                   | 0                     | 0                      |

| 62  | Ts₩(C)    | WAIT to Clock + Setup Time   | 50                  | 30                    | 20                     |

| 63  | ThW(C)    | WAIT to Clock + Hold Time    | 10                  | 10                    | 5                      |

| 64  | TsBRQ(C)  | BUSREQ to Clock † Setup Time | 90                  | 80                    | 60                     |

| 65  | ThBRQ(C)  | BUSREQ to Clock + Hold Time  | 10                  | 10                    | 5                      |

| 66  | TdC(BAKr) | Clock † to BUSACK † Delay    | 100                 | 75                    | 60                     |

| 67  | TdC(BAKf) | Clock † to BUSACK + Delay    | 100                 | 75                    | 60                     |

| 68  | TwA       | Address Valid Width          | 150*                | 95*                   | 50*                    |

| 69  | TdDS(S)   | DS + to STATUS Not Valid     | 80*                 | 55 <b>*</b>           | 30*                    |

Page 130

(Page 26)

A revised version of follows.

$\textit{version} \quad \textit{of} \quad \textit{the } \textbf{Clock-Cycle-Time-Dependent} \quad \textbf{Characteristics}$

|        | Clock-Cycle-Time-Dependent Characteristics (Page 130) |                         |                           |                           |  |  |  |

|--------|-------------------------------------------------------|-------------------------|---------------------------|---------------------------|--|--|--|

| Number | Symbol                                                | Z8001/Z8002<br>Equation | Z8001A/Z8002A<br>Equation | 280018/280028<br>Equation |  |  |  |

| 11     | TdA(DR)                                               | 2TcC + TwCh - 130 ns    | 2TcC + TwCh - 95 ns       | 2TcC + TwCh - 60 ns       |  |  |  |

| 13     | TdDS(A)                                               | TwCl – 25 ns            | TWC1 - 25 ns              | TwCl – 20 ns              |  |  |  |

| 16     | TdDW(DS)                                              | TcC + TwCh - 60 ns      | TcC + TwCh – 40 ns        | TcC + TwCh - 30 ns        |  |  |  |

| 17     | TdA(MR)                                               | TwCh – 50 ns            | TwCh - 35 ns              | TwCh – 20 ns              |  |  |  |

| 19     | TwMRh                                                 | TcC - 40 ns             | TcC - 30 ns               | 1cC - 20 ns               |  |  |  |

| 20     | TdMR(A)                                               | TwCl - 35 ns            | TwCl – 35 ns              | TwCl – 20 ns              |  |  |  |

| 21     | TdDW(DSW)                                             | TwCh – 50 ns            | TwCh – 35 ns              | TwCh – 25 ns              |  |  |  |

| 22     | TdMR(DR)                                              | 2ĭcC – 130 ns           | 2TcC - 100 ns             | 2TcC - 60 ns              |  |  |  |

| 25     | TdA(AS)                                               | ⊺wCh − 50 ns            | TwCh – 35 ns              | TwCh – 20 ns              |  |  |  |

| 27     | TdAS(DR)                                              | 2TcC - 140 ns           | 2TcC - 110 ns             | 2TcC - 60 ns              |  |  |  |

| 28     | TdDS(AS)                                              | TwCl – 35 ns            | TwCl – 35 ns              | ⊺wCl – 25 ns              |  |  |  |

| 29     | TwAS                                                  | TwCh – 20 ns            | TwCh – 15 ns              | TwCh – 10 ns              |  |  |  |

| 30     | TdAS(A)                                               | TwCl – 35 ns            | TwCl - 25 ns              | ⊺wCl – 20 ns              |  |  |  |

| 32     | TdAS(DSR)                                             | TwCl - 25 ns            | TwCl - 15 ns              | TwCl – 10 ns              |  |  |  |

| 33     | TdDSR(DR)                                             | TcC + TwCh - 150 ns     | TcC + TwCh - 105 ns       | TcC + TwCh - 70 ns        |  |  |  |

| 35     | TdDS(DW)                                              | TwCl – 30 ns            | TwCl – 25 ns              | TwCl – 15 ns              |  |  |  |

| 36     | TdA(DSR)                                              | TcC - 70 ns             | TcC - 55 ns               | TcC - 35 ns               |  |  |  |

| 38     | TwDSR                                                 | TcC + TwCh - 80 ns      | TcC + TwCh - 50 ns        | TcC + TwCh - 30 ns        |  |  |  |

| 40     | TwDSW                                                 | IcC - 65 ns             | TcC - 55 ns               | TcC - 25 ns               |  |  |  |

| 41     | TdDSI(DR)                                             | 2TcC - 170 ns           | 2TcC - 120 ns             | 21cC - 80 ns              |  |  |  |

| 43     | TwDS                                                  | 2TcC - 90 ns            | 21cC - 75 ns              | 2TcC - 40 ns              |  |  |  |

| 44     | TdAS(DSA)                                             | 4TcC + TwCl - 40 ns     | 4TcC + TwCl - 40 ns       | 4TcC + TwC1 - 30 ns       |  |  |  |

| 46     | TdDSA(DR)                                             | 2TcC + TwCh - 150 ns    | 2TcC + TwCh - 105 ns      | 2TcC + TwCh - 75 ns       |  |  |  |

| 48     | TdS(AS)                                               | TwCh – 55 ns            | TwCh – 40 ns              | TwCh – 30 ns              |  |  |  |

| 68     | TwA                                                   | TcC - 90 ns             | TcC - 70 ns               | TcC - 50 ns               |  |  |  |

| 69     | IdDS(S)                                               | TwCl – 25 ns            | ⊺wCl – 15 ns              | TwCl – 10 ns              |  |  |  |

Page 131 (Page 27) In  $\ensuremath{\mathsf{Test}}$  Conditions, the first sentence of the note following the diagram should read:

All ac parameters assume a total load capacitance (including parasitic capacitances) of 100 pF max, except for parameter 6 (50 pF max).

In **Ordering Information** the Description of all Z8001 and Z8001A Product Numbers should read:

CPU (segmented, <u>48</u>-pin).

In the Notes to **Ordering Information** change CM =  $-55^{\circ}$ C to +125°C to read:

$MB = -55^{\circ}C \text{ to } +125^{\circ}C.$

Page 133 (Page 1) In Figure 2, "Pin Assignments,"  $\overline{\text{DS}}$  and  $\overline{\text{AS}}$  were reversed. A corrected version of the art follows.

Figure 2. Pin Assignments

Page 138 (Page 6) In **Segment Trap and Acknowledge** the first sentence of the third paragraph should read:

Following the acknowledge cycle the CPU automatically pushes the Program Status ( $\underline{PC}$  and  $\underline{FCW}$ ) onto the system stack and loads another Program Status from the Program Status Area.

The third sentence of the third paragraph should read:

If the store creates a write warning condition, a Segment Trap Request is generated and is serviced at the end of the <u>program status</u> swap.

The fifth sentence of the third paragraph should read:

If a violation rather than a write warning occurs during the program status swap, the FATL flag is set rather than the SWW flag.

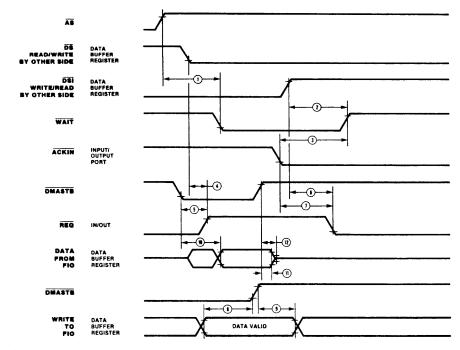

| Page 139                                   | In <b>DMA Operation</b> the third paragraph, the first three sentences should read                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (Page 7)                                   | as follows:                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                            | At the start of a DMA cycle, DMASYNC must go Low for <u>at least two</u> <u>clock</u> cycles, indicating to the MMU the beginning of a DMA cycle. A Low DMASYNC inhibits the MMU from using an indeterminate segment number on lines $SN_0-SN_6$ . When the DMA logical memory address is valid, the DMASYNC line must be High <u>before</u> a rising edge of Clock and the MMU then performs its address translation and access protection functions. |

| Page 144                                   | The DMASYC Pin Description should read as follows:                                                                                                                                                                                                                                                                                                                                                                                                     |

| (Page 12)                                  | DMA/Segment Number Synchronization Strobe (input, active High). A Low<br>on this line indicates that <u>the segment number lines are 3-state</u> ; a<br>High indicates that the segment number is valid. It must always be<br>High during CPU cycles. If a DMA device does not use the MMU for<br>address translation, the BUSACK signal from the CPU may be used as an<br>input to DMASYNC.                                                           |

| Page 145                                   | Add the following note to the DC Characteristics:                                                                                                                                                                                                                                                                                                                                                                                                      |

| (Page 13)                                  | NOTE: The on-chip back-bias voltage generator takes approximately 20<br>us to pump the back-bias voltage to -2.5V after the power has<br>been turned on. The performance of the Z8010 Z-MMU is not<br>guaranteed during this period.                                                                                                                                                                                                                   |

| Page 146<br>(Page 14)                      | Add the following note to AC Characteristics:                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                            | ** Timing measurements are made at the following voltages:                                                                                                                                                                                                                                                                                                                                                                                             |

|                                            | High Low<br>Clock 4.0V 0.8V<br>Output 2.0V 0.8V<br>Input 2.0V 0.8V<br>Float ΔV <u>+</u> 0.5V                                                                                                                                                                                                                                                                                                                                                           |

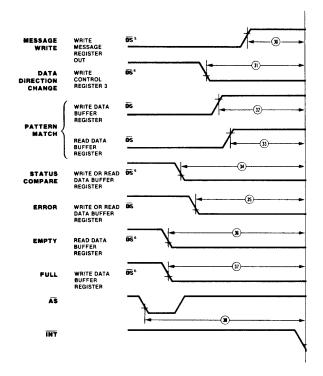

| Z8030 Z8000 Z-SCC<br>Product Specification |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Page 155                                   | In <b>Interrupts</b> add the following to the end of the fifth paragraph:                                                                                                                                                                                                                                                                                                                                                                              |

| (Page 7)                                   | Two or three $\overline{\text{AS}}$ rising edges are required from the time an interrupt condition occurs until $\overline{\text{INT}}$ is activated.                                                                                                                                                                                                                                                                                                  |

| Page 158<br>(Page 10)                      | Add the following to the end of the first paragraph of <b>Programming:</b>                                                                                                                                                                                                                                                                                                                                                                             |

|                                            | In the shift right mode the channel select $A/\overline{B}$ is taken from $AD_0$ and the state of $AD_5$ is ignored. In the shift left mode $A/\overline{B}$ is taken from $AD_5$ and the state of $AD_0$ is ignored. $AD_7$ and $AD_6$ are always ignored as address bits and the register address itself occupies $AD_4$ - $AD_1$ .                                                                                                                  |

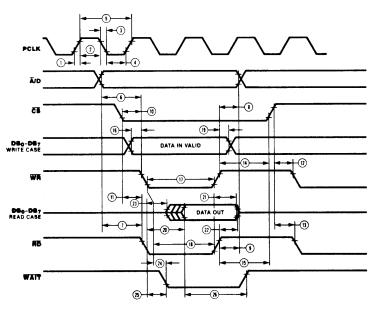

| Pages 164-68<br>(Pages 16-20)              | The timing tables on these pages have been revised and expanded to include 6 MHz timing. Corrected versions of these tables follow.                                                                                                                                                                                                                                                                                                                    |

#### Z-SCC Read and Write Timing (Page 164)

| No. | Symbol    | Parameter                                     | 4 MHz<br>Min(ns) Max(ns) | 6 MHz<br>Min(ns) Max(ns) | Notes* |

|-----|-----------|-----------------------------------------------|--------------------------|--------------------------|--------|

| 1   | TwAS      | AS Low Width                                  | 70                       | 50                       |        |

| 2   | TdDS(AS)  | DS ↑ to AS ↓ Delay                            | 50                       | 25                       |        |

| 3   | TsCSO(AS) | ĈŜ <sub>O</sub> to ĀŠ † Setup Time            | 0                        | 0                        | 1      |

| 4   | ThCSO(AS) | CSO to AS <sup>+</sup> Hold Time              | 60                       | 40                       | 1      |

| 5   | TsCS1(DS) | CS1 to DS ↓ Setup Time                        | 100                      | 80                       | 1      |

| 6   | ThCS1(DS) | CS1 to DS+ Hold Time                          | 55                       | 40                       | 1      |

| 7   | TsIA(AS)  | INTACK to AS + Setup Time                     | 0                        | 0                        |        |

| 8   | ThIA(AS)  | INTACK to AS + Hold Time                      | 250                      | 250                      |        |

| 9   | TsRWR(DS) | R/W(Read) to DS + Setup Time                  | 100                      | 80                       |        |

| 10  | ThRW(DS)  | R/W to DS + Hold Time                         | 55                       | 40                       |        |

| 11  | TsRWW(DS) | R/₩(Write) to DS ↓ Setup Time                 | 0                        | 0                        |        |

| 12  | TdAS(DS)  | ĀS ↑ to DS ↓ Delay                            | 60                       | 40                       |        |

| 13  | TwDS1     | DS Low Width                                  | 390                      | 250                      |        |

| 14  | TrC       | Valid Access Recovery Time                    | 6TcPC                    | 6TcPC                    | 2      |

|     |           | ·                                             | +200                     | +130                     |        |

| 15  | TsA(AS)   | Address to AS 🛧 Setup Time                    | 30                       | 10                       | 1      |

| 16  | ThA(AS)   | Address to $\overline{\text{AS}}$ + Hold Time | 50                       | 30                       | 1      |

| 17  | TsDW(DS)  | Write Data to DS 🕴 Setup Time                 | 30                       | 20                       |        |

| 18  | ThDW(DS)  | Write Data to DS † Hold Time                  | 30                       | 20                       |        |

| 19  | TdDS(DA)  | DS + to Data Active Delay                     | 0                        | 0                        |        |

| 20  | TdDSr(DR) | DS 🕇 to Read Data Not Valid Delay             | 0                        | 0                        |        |

| 21  | TdDSf(DR) | DS + to Read Data Valid Delay                 | 250                      | 180                      |        |

| 22  | TdAS(DR)  | AS 🕈 to Read Data Valid Delay                 | 520                      | 335                      |        |

#### NOTES:

1. Parameter does not apply to Interrupt Acknowledge transactions.

<sup>2.</sup> Parameter applies only between transactions involving the Z-SCC.

|     |            | Z-SCC Cycle Timing (Page                                                | : 165) |                  |     |                  |       |

|-----|------------|-------------------------------------------------------------------------|--------|------------------|-----|------------------|-------|

| No. | Symbol     | Parameter                                                               |        | MHz<br>) Max(ns) | -   | MHz<br>) Max(ns) | Notes |

| 23  | TdDS(DRz)  | DS + to Read Data Float Delay                                           |        | 70               |     | 45               | 3     |

| 24  | TdA(DR)    | Address Required Valid to Read Data Valid<br>Delay                      |        | 570              |     | 420              |       |

| 25  | TdDS(W)    | DS ↓ to Wait Valid Delay                                                |        | 240              |     | 200              | 4     |

| 26  | TdDSf(REQ) | DS + to W/REQ Not Valid Delay                                           |        | 240              |     | 200              |       |

| 27  | TdDSr(REQ) | DS + to DTR/REQ Not Valid Delay                                         |        | 5TcPC            |     | 5TcPC            |       |

|     |            |                                                                         |        | +300             |     | +250             |       |

| 28  | TdAS(INT)  | AS 🛧 to INT Valid Delay                                                 |        | 500              |     | 500              | 4     |

| 29  | TdAS(DSA)  | AS 🛧 to DS 🕴 (Acknowledge) Delay                                        |        |                  |     |                  | 5     |

| 30  | TwDSA      | DS (Acknowledge) Low Width                                              | 390    |                  | 250 |                  |       |

| 31  | TdDSA(DR)  | DS ↓ (Acknowledge) to Read Data Valid Delay                             |        | 250              |     | 180              |       |

| 32  | TsIEI(DSA) | IEI to DS ↓ (Acknowledge) Setup Time                                    | 120    |                  | 100 |                  |       |

| 33  | ThIEI(DSA) | IEI to DS 🛧 (Acknowledge) Hold Time                                     | 0      |                  | 0   |                  |       |

| 34  | TdIEI(IEO) | <u>IE</u> I to IEO Delay                                                |        | 120              |     | 100              |       |

| 35  | TdAS(IEO)  | AS 🛧 to IEO Delay                                                       |        | 250              |     | 250              | 6     |

| 36  | TdDSA(INT) | DS ↓ (Acknowledge) to INT Inactive Delay                                |        | 500              |     | 500              | 4     |

| 37  | TdDS(ASQ)  | $\overline{\text{DS}}$ + to $\overline{\text{AS}}$ + Delay for No Reset | 30     |                  | 15  |                  |       |

| 38  | TdASQ(DS)  | AS + to DS + Delay for No Reset                                         | 30     |                  | 30  |                  |       |

| 39  | Twres      | AS and DS Coincident Low for Reset                                      | 250    |                  | 250 |                  | 7     |

| 40  | TwPC1      | PCLK Low Width                                                          | 105    | 2000             | 70  | 1000             |       |

| 41  | TwPCh      | PCLK High Width                                                         | 105    | 2000             | 70  | 1000             |       |

| 42  | TcPC       | PCLK Cycle Time                                                         | 250    | 4000             | 165 | 2000             |       |

| 43  | TrPC       | PCLK Rise Time                                                          |        | 20               |     | 15               |       |

| 44  | TfPC       | PCLK Fall Time                                                          |        | 20               |     | 10               |       |

#### NOTES:

- 3. Float delay is defined as the time required for a  $\pm 0.5$  V change in the output with a maximum dc load and minimum ac load.

- 4. Open-drain output, measured with open-drain test load.

- Parameter is system dependent. For any Z-SCC in the daisy chain, TdAS(DSA) must be greater than the sum of TdAS(IEO) for the highest priority device in the daisy chain, TsIEI(DSA) for the Z-SCC, and TdIEIf(IEO) for each device

separating them in the daisy chain.

- Parameter applies only to a Z-SCC pulling INT Low at the beginning of the Interrupt Acknowledge transaction.

- Internal circuitry allows for the reset provided by the Z8 to be recognized as a reset by the Z-SCC.

\*Timings are preliminary and subject to change. All timing references assume 2.0 V for a logic "1" and 0.8 V for a logic "0". Z-SCC General Timing (Page 166)

| No. | Symbol      | Parameter                           |       | MHz<br>)Max(ns) |       | ) Max(ns) | Notes*          |

|-----|-------------|-------------------------------------|-------|-----------------|-------|-----------|-----------------|

| 1   | TdPC(REQ)   | PCLK + to ₩/REQ Valid               |       | 250             |       | 250       |                 |

| 2   | TdPC(W)     | PCLK ↓ to Wait Inactive Delay       |       | 350             |       | 350       |                 |

| 3   | TsRXC(PC)   | RxC + to PCLK + Setup Time          | 50    |                 | 50    |           | 1,4             |

| 4   | IsRXD(RXCr) | RxD to RxC + Setup Time (X1 Mode)   | 0     |                 | 0     |           | 1               |

| 5   | ThRXD(RXCr) | RxD to RxC + Hold Time (X1 Mode)    | 150   |                 | 150   |           | 1               |

| 6   | IsRXD(RXCf) | RxD to RxC ↓ Setup Time (X1 Mode)   | 0     |                 | 0     |           | 1,5             |

| 7   | ThRXD(RXCf) | RxD to RxC + Hold Time (X1 Mode)    | 150   |                 | 150   |           | 1,5             |

| 8   | TsSY(RXC)   | SYNC to RxC + Setup Time            | -200  |                 | -200  |           | 1               |

| 9   | ThSY(RXC)   | SYNC to RxC + Hold Time             | 3TcPC |                 | 3TcPC |           |                 |

|     |             |                                     | +200  |                 | +200  |           | 1               |

| 10  | IsTXC(PC)   | TxC ↓ to PCLK ↑ Setup Time          | 0     |                 | 0     |           | 2,4<br>2<br>2,5 |

| 11  | TdTXCf(TXD) | TxC + to TxD Delay (X1 Mode)        |       | 300             |       | 300       | 2               |

| 12  | IdIXCr(IXD) | TxC + to TxD Delay (X1 Mode)        |       | 300             |       | 300       | 2,5             |

| 13  | TdTXD(TRX)  | TxD to TRxC Delay (Send Clock Echo) |       |                 |       |           |                 |

| 14  | TwRTXh      | RTxC High Width                     | 180   |                 | 180   |           |                 |

| 15  | TwRTX1      | RTxC Low Width                      | 180   |                 | 180   |           |                 |

| 16  | TcRTX       | RTxC Cycle Time                     | 400   |                 | 400   |           |                 |

| 17  | TcRTXX      | Crystal Oscillator Period           | 250   | 1000            | 250   | 1000      | 3               |

| 18  | TwTRXh      | TRxC High Width                     | 180   |                 | 180   |           |                 |

| 19  | TwTRX1      | TRxC Low Width                      | 180   |                 | 180   |           |                 |

| 20  | TcTRX       | TRxC Cycle Time                     | 400   |                 | 400   |           |                 |

| 21  | Twext       | DCD or CTS Pulse Width              | 200   |                 | 200   |           |                 |

| 22  | TwSY        | SYNC Pulse Width                    | 200   |                 |       |           |                 |

- RxC is RTxC or TRxC, whichever is supplying the receive clock.

TxC is TRxC or RTxC, whichever is supplying

- the transmit clock. 3. Both RTxC and SYNC have 30 pF capacitors to

- the ground connected to them. 4. Parameter applies only if the data rate is

one-fourth the PCLK rate. In all other cases, no phase relationship between RxC and and PCLK or TxC and PCLK is required. 5. Parameter applies only to FM encoding/

- decoding.

- \*Timings are preliminary and subject to change.

| Units<br>TcPC<br>TcPC<br>TcPC<br>TcPC | Notes<br>2<br>1,2 |

|---------------------------------------|-------------------|

| TcPC                                  | _                 |

|                                       | 12                |

| TcPC                                  |                   |

|                                       | 2                 |

| TcPC                                  | 1,2               |

| ĀS                                    |                   |

| TcPC                                  | 3                 |

| TcPC                                  | 1,3               |

| TcPC                                  | 3                 |

| TcPC                                  | 1,3               |

| AS                                    |                   |

| ĀŠ                                    | 1                 |

| ĀŠ                                    | 1                 |

|                                       |                   |

| supplyi                               | ing th            |

| 3                                     | TcPC<br>TcPC      |

12

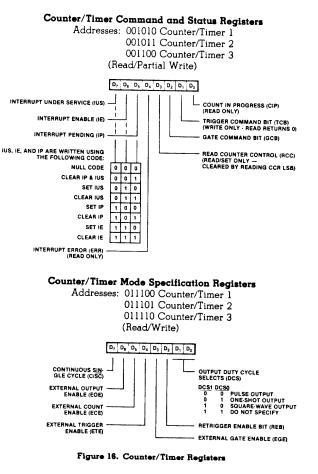

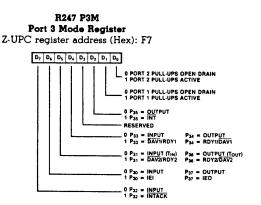

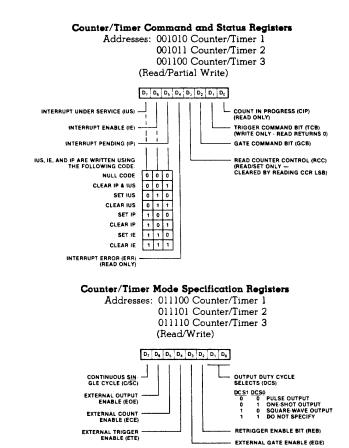

# Z8036 Z8000 Z-C10 Product Specification

Page 172 (Page 2) In Pin Description, the PCLK entry, delete the last sentence:

Maximum input frequency is 4MHz.

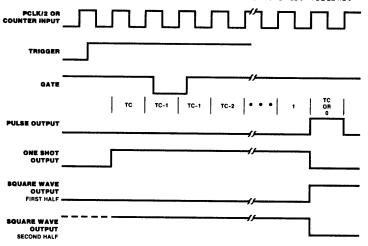

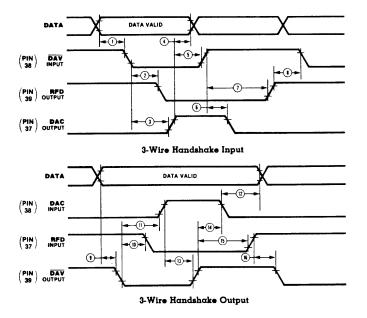

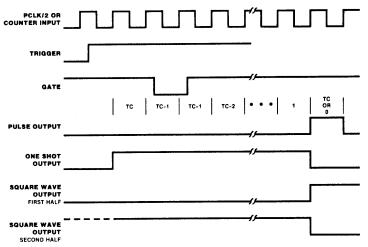

Page 179 (Page 9) In Figure 10, "Counter/Timer Waveforms," the time constant line is incorrect between TC-2 and 1. A corrected version of the art follows.

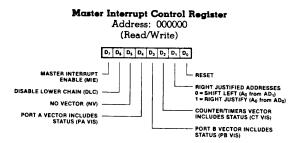

In Figure 11, "Master Control Registers," the mnemonics were omitted for bits  $D_1$  and  $D_5$ . They should read, respectively:

Right Justified Addresses (RJA) No Vector (NV)

Figure 11. Master Control Registers

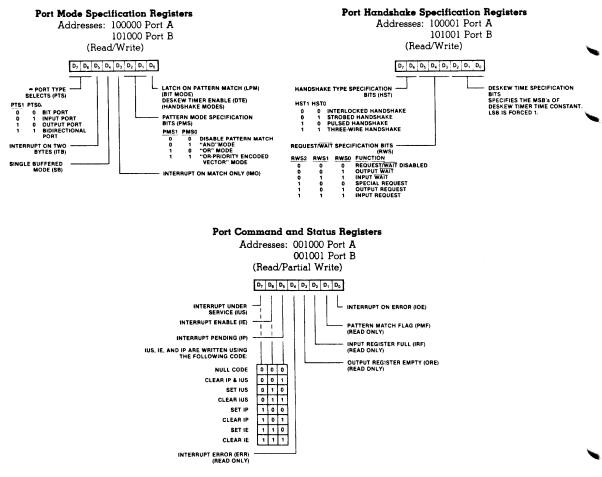

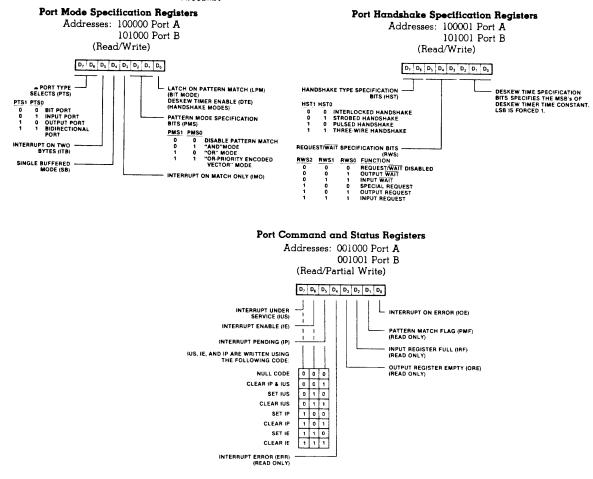

In Figure 12, "Port Specification Registers," the Port Mode Specification Registers Addresses should read:

100000 Port A 101000 Port B

The Port Handshake Specification Registers Addresses should read:

100001 Port A 101001 Port B

The Port Command and Status Registers Addresses should read:

001000 Port A 001001 Port B

In Port Mode Specification Registers "PTS2" should read "PTS0." Corrected versions of the art follow.

Figure 12. Port Specification Registers

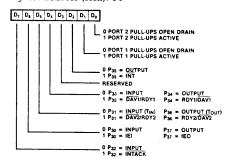

Page 185 (Page 15) In the Register Address Summary add the following note to the Address columns:

\*When RJA = 0,  $A_0$  from  $AD_1$ ; when RJA = 1,  $A_0$  from  $AD_0$ .

Delete  $({\rm AD}_7-{\rm AD}_0)$  below Address in all cases. Delete XX at the end of the Address in all cases.

In **Most Often Accessed Registers** change Counter/Timer Control to Counter/ Timer Command and Status in all cases. A corrected version of the art follows.

| Register<br>Address<br>Summary | Address<br>000000<br>000001<br>000010<br>000010<br>000100<br>000101<br>000110 | Main Control Registers<br>Register Name<br>Master Interrupt Control<br>Master Configuration Control<br>Port A's Interrupt Vector<br>Port B's Interrupt Vector<br>Counter/Timer's Interrupt Vector<br>Port C's Data Path Polarity<br>Port C's Data Direction<br>Port C's Special I/O Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Address<br>100000<br>100001<br>100010<br>10010<br>100101<br>100101<br>100110 | <b>Port A Specification Registers</b><br><b>Register Name</b><br>Port A's Mode Specification<br>Port A's Handshake Specification<br>Port A's Data Darbert<br>Port A's Data Direction<br>Port A's Special I/O Control<br>Port A's Pattern Polarity<br>Port A's Pattern Transition<br>Port A's Pattern Mask |

|--------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                | Address                                                                       | Most Often Accessed Registers<br>Register Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Address                                                                      | Port B Specification Registers<br>Register Name                                                                                                                                                                                                                                                           |

|                                | 001000<br>001001<br>001010<br>001011<br>001100<br>001101<br>001110<br>001111  | Port A's Command and Status<br>Port B's Command and Status<br>Counter/Timer 1's Command and Status<br>Counter/Timer 2's Command and Status<br>Counter/Timer 3's Command and Status<br>Port A's Data<br>Port B's Data<br>Port C's Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 101000<br>101001<br>101010<br>101011<br>101100<br>101101                     | Port B's Mode Specification<br>Port B's Handshake Specification<br>Port B's Data Path Polarity<br>Port B's Data Direction<br>Port B's Special I/O Control<br>Port B's Pattern Polarity<br>Port B's Pattern Transition<br>Port B's Pattern Mask                                                            |

|                                | Address                                                                       | Counter/Timer Related Registers<br>Register Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                              |                                                                                                                                                                                                                                                                                                           |

|                                | 010000<br>010001<br>010010<br>010011<br>010100<br>010111<br>010110<br>011011  | Counter/Timer 1's Current Count-MSBs<br>Counter/Timer 1's Current Count-LSBs<br>Counter/Timer 2's Current Count-LSBs<br>Counter/Timer 2's Current Count-LSBs<br>Counter/Timer 3's Current Count-LSBs<br>Counter/Timer 3's Current Count-LSBs<br>Counter/Timer 1's Time Constant-LSBs<br>Counter/Timer 2's Time Constant-LSBs<br>Counter/Timer 2's Time Constant-LSBs<br>Counter/Timer 2's Time Constant-LSBs<br>Counter/Timer 3's Mode Specification<br>Counter/Timer 3's Mode Specification<br>Counter/Timer 3's Mode Specification<br>Counter/Timer 3's Mode Specification |                                                                              |                                                                                                                                                                                                                                                                                                           |

Page 187 (Page 17) In **DC Characteristics** the Maximum rating for Symbol  $I_{CC}$  should read 200.

Pages 188-194 (Pages 18-23)

The timing tables for these pages have been revised and expanded to include the 6MHz timing. Corrected versions of the tables follow.

#### Z-CIO CPU Interface Timing (Page 188)

|            | <b>C</b> 1 <b>1</b> |                                                                           |             | MHz  |     | MHz  |                 |       |

|------------|---------------------|---------------------------------------------------------------------------|-------------|------|-----|------|-----------------|-------|

| No.        | Symbol              | Parameter                                                                 | Min         | Max  | Min | Max  | Units           | Notes |

| 1          | TwAS                | AS Low Width                                                              | 70          | 2000 | 50  | 2000 | ns              |       |

| 2          | TsA(AS)             | Address to AS 🛧 Setup Time                                                | 30          |      | 10  |      | ns              | 1     |

| 3          | ThA(AS)             | Address to AS + Hold Time                                                 | 50          |      | 30  |      | ns              | 1     |

| 4          | TsA(DS)             | Address to DS + Setup Time                                                | 130         |      | 100 |      |                 | •     |

| 5          | TsCSO(AS)           | CSn to AS + Setup Time                                                    | 0           |      | 0   |      | ns              | 1     |

| 6          | ThCSO(AS)           | $CS_0$ to $\overline{AS}$ + Hold Time                                     | 60          |      | 40  |      | ns              | 1     |

| 7          | TdAS(DS)            | $\overrightarrow{AS} \uparrow to \overrightarrow{DS} \downarrow Delay$    | 60<br>60    |      | . = |      | ns              | 1     |

| 8          | TsCS1(DS)           | CS <sub>1</sub> to DS ↓ Setup Time                                        |             |      | 40  |      | ns              | 1     |

| 9          | TsRWR(DS)           | R/W (Read) to DS + Setup Time                                             | 100         |      | 80  |      | ns              |       |

| 10         | TsRWW(DS)           | R/W (Write) to DS + Setup Time                                            | 100         |      | 80  |      | ns              |       |

| 11         | TwDS                | $\overline{\text{DS}}$ Low Width                                          | 0           |      | 0   |      |                 |       |

| 12         |                     |                                                                           | 390         |      | 250 |      | ns              |       |

|            | TsDW(DSf)           | Write Data to DS ↓ Setup Time                                             | 30          |      | 20  |      | ns              |       |

| 13         | TdDS(DRV)           | DS (Read) ↓ to Address Data Bus Driven                                    | 0           |      | 0   |      |                 |       |

| 14         | TdDSf(DR)           | DS ↓ to Read Data Valid Delay                                             |             | 250  |     | 180  | ns              |       |

| 15         | ThDW(DS)            | Write Data to DS ↑ Hold Time                                              | 30          |      | 20  |      | ns              |       |

| 16         | TdDSr(DR)           | DS ↑ to Read Data Not Valid Delay                                         | 0           |      | 0   |      |                 |       |

| 17         | TdDS(DRz)           | DS 🛧 to Read Data Float Delay                                             |             | 70   |     | 45   | ns              | 2     |

| 18         | ThR₩(DS)            | R/₩ to DS ↑ Hold Time                                                     | 55          |      | 40  |      | ns              | ~     |

| 19         | ThCS1(DS)           | CS <sub>1</sub> to DS + Hold Time                                         | 55          |      | 40  |      | ns              |       |

| 20         | TdDS(AS)            | $\overline{\text{DS}}$ + to $\overline{\text{AS}}$ + Delay                | 50          |      | 25  |      |                 |       |

| 21         | Tre                 | Valid Access Recovery Time                                                | 1000        |      | 650 |      | ns<br>ns        | 3     |

|            |                     | Z-CIO Interrupt Timin                                                     | 9           |      |     |      |                 |       |

| 22         | TdPM(INT)           | Pattern Match to INI Delay (Bit Port)                                     |             | 1    |     | 1    | AS cycle        |       |

| 23         | TdACK(INT)          | $\overline{ACKIN}$ to $\overline{INI}$ Delay (Port with Handshake)        |             | 4    |     | 4    | AS cycle        |       |

| 24         | TdCI(INT)           | Counter Input to $\overline{	ext{INI}}$ Delay (Counter Mode)              |             | 1    |     | 1    | AS cycle        | 4     |

| 25         | TdPC(INT)           | PCLK to INT Delay (Timer Mode)                                            |             | 1    |     | 1    | +ns<br>AS cycle |       |

| 26         | TdAS(INT)           | AS to INT Delay                                                           |             |      |     |      | +ns<br>ns       |       |

|            |                     | Z-CIO Interrupt Acknowledge                                               | Timing      |      |     |      |                 |       |

| 27         | TsIA(AS)            | INTACK to AS + Setup Time                                                 | 0           |      | 0   |      | ns              |       |

| 28         | ThIA(AS)            | INTACK to AS + Hold Time                                                  | 250         |      | 250 |      |                 |       |

|            | TsAS(DSA)           | AS + to DS (Acknowledge) + Setup Time                                     | 350         |      | 250 |      | ns              | -     |

|            | TdDSA(DR)           | DS (Acknowledge) + to Read Data Valid Delay                               | <i>)</i> )0 | 250  | 200 | 180  | ns              | 5     |

| -          | TwDSA               | DS (Acknowledge) V to Kead Data Valid Delay<br>DS (Acknowledge) Low Width | 390         | 270  | 250 | 100  | ns              |       |

|            | TdAS(IEQ)           | AS A to IEO + Delay (INTACK Cycle)                                        | 290         | 75.0 | 250 | 05.0 | ns              | -     |

|            | IdIEI(IEO)          | IEI to IEO Delay                                                          |             | 350  |     | 250  | ns              | 5     |

|            | TsIEI(DSA)          | IEI to DS (Acknowledge) ↓ Setup Time                                      | 100         | 150  | 70  | 100  | ns              | 5     |

| 35         | ThIEI(DSA)          | IEI to DS (Acknowledge) + Setup lime                                      | 100         |      | 70  |      | ns              | 5     |

| 36         | TdDSA(INT)          | IEI to DS (Acknowledge) + Hold Time                                       | 100         | (    | 70  |      | ns              |       |

| <i>~</i> 0 | TUDOA(INT)          | DS (Acknowledge) + to INT + Delay                                         |             | 600  |     | 600  | ns              |       |

2. Float delay is measured to the time when the output has changed 0.5 V from steady state with minimum ac load and maximum dc load.

- This is the delay from DS + of one CIO access to DS + of another CIO access.

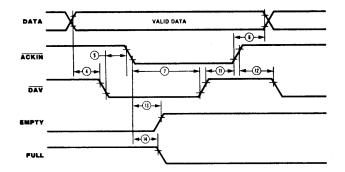

The delay is from DAV + for 3-Wire Input Handshake. The delay is from DAC + for 3-Wire Output Handshake. One additional AS cycle is the delay is the delay is the delay is the delay is from DAC + for 3-Wire Output Handshake. The delay is the delay is from DAC + for 3-Wire Output Handshake. required for ports in the Single Buffered mode.

- particular daisy chain must meet the following constraint: the delay from  $\overline{AS} \uparrow to \overline{DS} \lor$  must \_following be greater than the sum of TdAS(IEO) for the highest priority peripheral, TsIEI(DSA) for lowest priority peripheral, and TdIEI(IEO) for each peripheral separating them in the chain.

- \*Timings are preliminary and subject to change. All timing references assume 2.0 V for a logic "1" and 0.8 V for a logic "0".

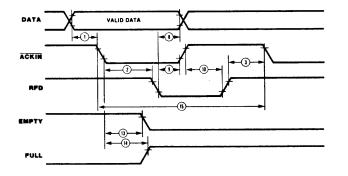

|     |              |                                                                        | 4 M | Hz  | 6 M | Hz  |         |       |

|-----|--------------|------------------------------------------------------------------------|-----|-----|-----|-----|---------|-------|

| No. | Symbol       | Parameter                                                              | Min | Max | Min | Max | Units   | Notes |

| 1   | TsDI(ACK)    | Data Input to ACKIN + Setup Time                                       | 0   |     | 0   |     | ns      |       |

| 2   | ThDI(ACK)    | Data Input to ACKIN + Hold Time<br>Strobed Handshake                   |     |     |     |     | ns      |       |

| 3   | TdACKf(RFD)  | ACKIN + to RFD + Delay                                                 | 0   |     | 0   |     | ns      |       |

| 4   | TwACK1       | ACKIN Low WidthStrobed Handshake                                       |     |     |     |     | ns      |       |

| 5   | TwACKh       | ACKIN High WidthStrobed Handshake                                      |     |     |     |     | ns      |       |

| 6   | TdRFDr(ACK)  | RFD + to ACKIN + Delay                                                 | 0   |     | 0   |     | ns      |       |

| 7   | IsDO(DAV)    | Data Out to DAV + Setup Time                                           | 25  |     | 20  |     | ns      | 1     |

| 8   | TdDAVf(ACK)  | DAV + to ACKIN + Delay                                                 | 0   |     | 0   |     | ns      |       |

| 9   | ThDO(ACK)    | Data Out to ACKIN + Hold Time                                          | 1   |     | 1   |     | AS cycl | е     |

| 10  | TdACK(DAV)   | ACKIN + to DAV + Delay                                                 | 1   |     | 1   |     | AS cycl | е     |

| 11  | ThDI(RFD)    | Data Input to RFD + Hold Time<br>Interlocked Handshake                 | 0   |     | 0   |     | ns      |       |

| 12  | TdRFDf(ACK)  | RFD + to ACKIN + Delay                                                 | 0   |     | 0   |     | ns      |       |

| 13  | TdACKr(RFD)  | Interlocked Handshake<br>ACKIN + (DAV + ) to RFD + Delay               | 0   |     | 0   |     | ns      |       |

| 14  | TdDAVr(ACK)  | Interlocked and 3-Wire Handshake<br>DAV+to ACKIN + (RFD + )Interlocked | 0   |     | 0   |     | ns      |       |

|     |              | and 3-Wire Handshake                                                   |     |     |     |     |         |       |

| 15  | Tdack(DAV)   | ACKIN + (RFD + ) to DAV + Delay<br>_Interlocked and 3-Wire Handshake   | 0   |     | 0   |     | ns      |       |

| 16  | TdDAVIf(DAC) | DAV + to DAC + Delay-Input<br>3-Wire Handshake                         | 0   |     | 0   |     | ns      |       |

| 17  | ThDI(DAC)    | Data Input to DAC + Hold Time                                          | 0   |     | 0   |     | ns      |       |

| 18  | TdDACOr(DAV) | 3-Wire Handshake<br>DAC ↑ to DAV ↑ DelayInput                          | 0   |     | 0   |     | ns      |       |

| 19  | TdDAVIr(DAC) | <u>3-</u> Wire Handshake<br>DAV ↑ to DAC ↓ DelayInput                  | 0   |     | 0   |     | ns      |       |

| 20  | TdDAVOf(DAC) | <u>3-</u> Wire Handshake<br>DAV + to DAC + DelayOutput                 | 0   |     | 0   |     | ns      |       |

|     |              | 3-Wire Handshake                                                       |     |     |     |     |         |       |

| 21  | ThDO(DAC)    | Data Output to DAC ↑ Hold Time<br>3-Wire Handshake                     | 1   |     | 1   |     | AS cycl |       |

| 22  | TdDACIr(DAV) | DAC+to DAV + DelayOutput<br>3-Wire Handshake                           | 1   |     | 1   |     | AS cycl | е     |

| 23  | TdDAVOr(DAC) | DAV + to DAC + DelayOutput<br>3-Wire Handshake                         | 0   |     | 0   |     | ns      |       |

NOTES: 1. This time can be extended through the use of the deskew timers. \*Timings are preliminary and subject to change.

All timing references assume 2.0 V for a logic "1" and 0.8 V for a logic "0".

| Z-C10 | Counter/Timer | Timing | (Page | 192) |

|-------|---------------|--------|-------|------|

|-------|---------------|--------|-------|------|

|     |          |                                                               | 4   | MHz  | 61  | MHz  |       |        |

|-----|----------|---------------------------------------------------------------|-----|------|-----|------|-------|--------|

| No. | Symbol   | Parameter                                                     | Min | Max  | Min | Max  | Units | Notes* |

| 1   | ТсРС     | PCLK Cycle Time                                               | 250 | 4000 | 165 | 4000 | ns    | 1      |

| 2   | TwPCh    | PCLK High Width                                               | 105 | 2000 | 70  | 2000 | ns    |        |

| 3   | TwPC1    | PCLK Low Width                                                | 105 | 2000 | 70  | 2000 | ns    |        |

| 4   | TFPC     | PCLK Fall Time                                                |     | 20   |     | 10   | ns    |        |

| 5   | TrPC     | PCLK Rise Time                                                |     | 20   |     | 15   | ns    |        |

| 6   | TcCI     | Counter Input Cycle Time                                      | 500 |      | 330 |      | ns    |        |

| 7   | TCIh     | Counter Input High Width                                      | 230 |      | 150 |      | ns    |        |

| 8   | TwCI1    | Counter Input Low Width                                       | 230 |      | 150 |      | ns    |        |

| 9   | IfCI     | Counter Input Fall Time                                       |     | 20   |     | 15   | ns    |        |

| 10  | TrCI     | Counter Input Rise Time                                       |     | 20   |     | 15   | ns    |        |

| 11  | TsTI(PC) | Trigger Input to PCLK + Setup Time<br>(Timer Mode)            |     |      |     |      | ns    | 2      |

| 12  | TsTI(CI) | Trigger Input to Counter Input + Setup Time<br>(Counter Mode) |     |      |     |      | ns    | 2      |

| 13  | TwTI     | Trigger Input Pulse Width (High or Low)                       |     |      |     |      | ns    |        |

| 14  | TsGI(PC) | Gate Input to PCLK + Setup Time<br>(Timer Mode)               |     |      |     |      | ns    | 2      |

| 15  | TsGI(CI) | Gate Input to Counter Input ♦ Setup Time<br>(Counter Mode)    |     |      |     |      | ns    | 2      |

| No. | Symbol   | Parameter                                                 | 4 MHz                                 |     | 6 MHz |     |       |        |

|-----|----------|-----------------------------------------------------------|---------------------------------------|-----|-------|-----|-------|--------|

|     |          |                                                           | Min                                   | Max | Min   | Max | Units | Notes* |

| 16  | ThGI(PC) | Gate Input to PCLK ♦ Hold Time (Timer Mode)               | · · · · · · · · · · · · · · · · · · · |     |       |     | ns    | 2      |

| 17  | ThGI(CI) | Gate Input to Counter Input + Hold Time<br>(Counter Mode) |                                       |     |       |     | ns    | 2      |

| 18  | TdPC(CO) | PCLK to Counter Output Delay (Timer Mode)                 |                                       |     |       |     | ns    |        |

| 19  | TdCI(CO) | Counter Input to Counter Output Delay<br>(Counter Mode)   |                                       |     |       |     | ns    |        |

NOTES:

PCLK is only used with the counter/timers (in Timer mode), the deskew timers, and the REQUEST/WAIT logic. If these functions are not used, the PCLK input can be held Low.

- ----

trigger or gate are valid for the next counter/timer cycle. \*Timings are preliminary and subject to change.

2. These parameters must be met to guarantee

\*Timings are preliminary and subject to change. All timing references assume 2.0 V for a logic "1" and 0.8 V for a logic "0".

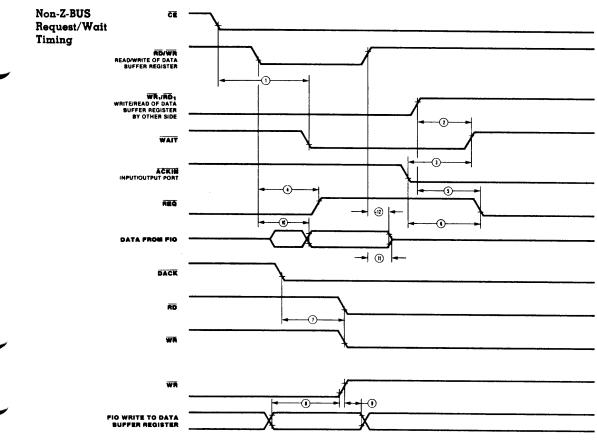

| Z-CIU REQUEST/WAI | l liming (Page 193) |

|-------------------|---------------------|

|                   |                     |

|     |                     |                         | 4 M | 4 MHz |     | Hz  |           |        |

|-----|---------------------|-------------------------|-----|-------|-----|-----|-----------|--------|

| No. | o. Symbol Parameter | Parameter               | Min | Max   | Min | Max | Units     | Notes* |

| 1   | TdDS(REQ)           | DS + to REQ + Delay     |     |       |     |     | ns        |        |

| 2   | TdDS(WAIT)          | DS + to WAIT + Delay    |     |       |     |     | ns        |        |

| 3   | TdPC(REQ)           | PCLK + to REQ + Delay   |     |       |     |     | ns        |        |

| 4   | TdPC(WAIT)          | PCLK + to Wait + Delay  |     |       |     |     | ns        |        |

| 5   | TdACK(REQ)          | ACKIN + to REQ + Delay  |     |       |     |     | AS cycle  | es 1   |

|     |                     |                         |     |       |     |     | +PCLK cyc | cles   |

|     |                     |                         |     |       |     |     | +ns       |        |

| 6   | TdACK(WAIT)         | ACKIN ↓ to Wait ↑ Delay |     |       |     |     | PCLK cycl | les    |

|     |                     |                         |     |       |     |     | +ns       |        |

#### NOTES:

The Delay is from DAV + for the 3-Wire Input Handshake. The delay is from DAC + for the 3-Wire Output Handshake.

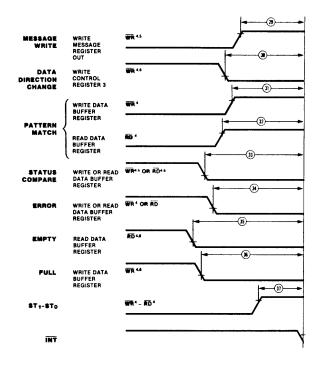

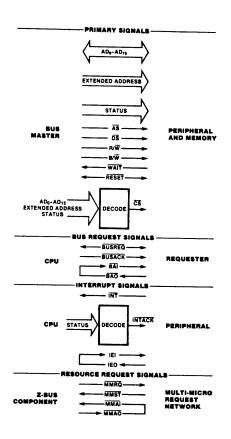

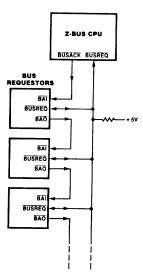

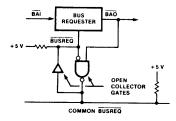

\*Timings are preliminary and subject to change. All timing references assume 2.0 V for a logic "1" and 0.8 V for a logic "O".